Устройство для суммирования -разрядных последовательно поступающих чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

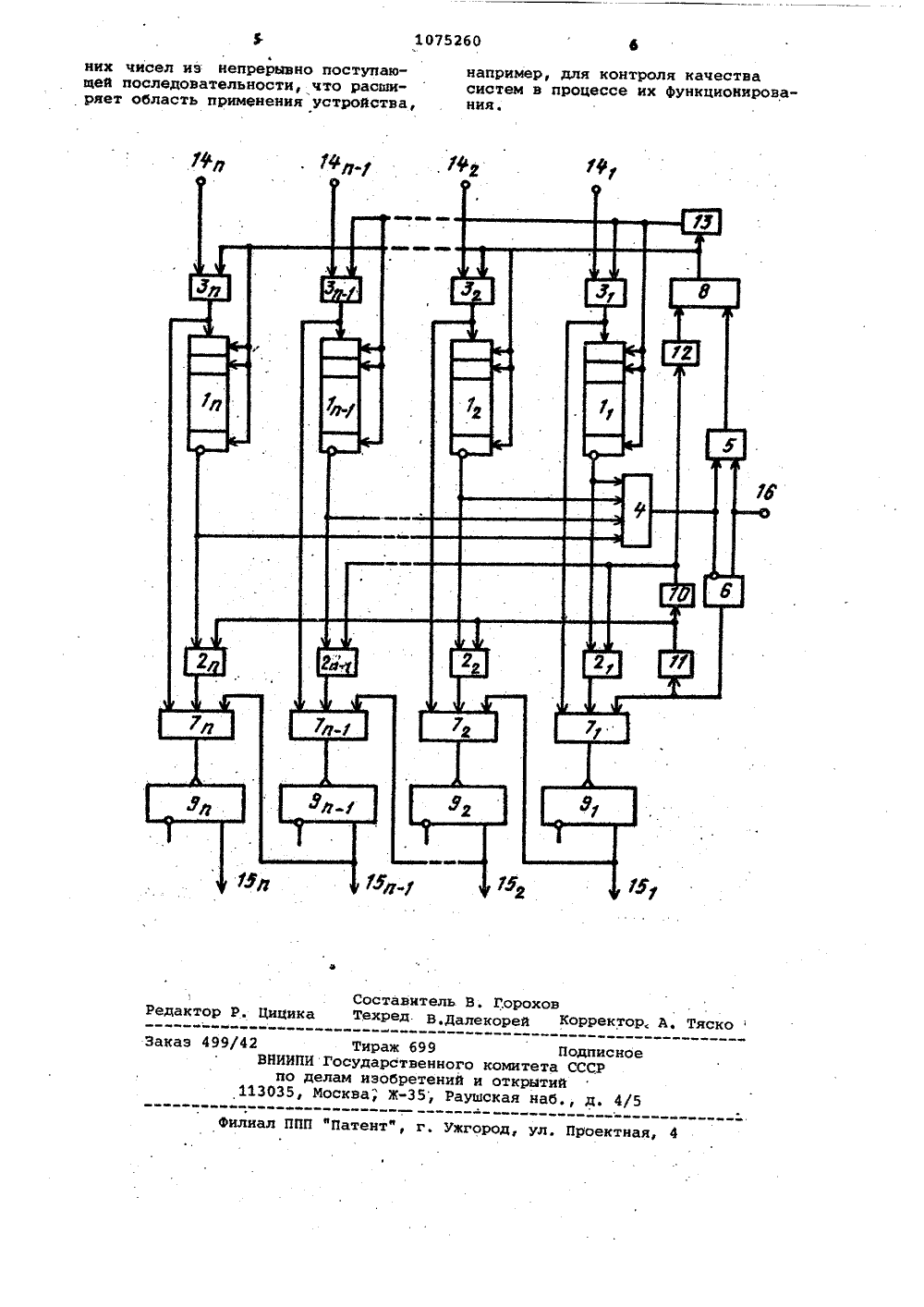

ройемен ГОСУДАРСТВЕННЫЙ КОМИТЕТ СС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬ(54) (57) УСТРОЙСТВО ДЛЯ СУИИИРОВАНИЯ в и-РАЭРЯДНЦХ ПОСЛЕДОВАТЕЛЬНО ПОСТУПИОЩИХ ЧИСЕЛ, содержащее группу из о счетных триггеров, первую группу из и элементов И, группу иэ и элементов ИЛИ.и первый элемент задержки, причем первые входы -х элементов И первой группы, где= 2,4 и, соединены между соб и с входом первого элемента задержки, выход которого соединен с первыми входами-1)-х элементов И первой группы, выход х-го элемента И первой группы, где 1=1,2,и, соединен с первым входом 1-го элемента ИЛИ группы, выход которого соединен с счетным входом 1-го счет ного триггера, единичный выход которого является 1-м выходом устройства и соединен с вторым входом (1+1)-го элемента ИЛИ группы,о тл и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей путем обеспечения вычисления суммы последних ш чисел из поступающей последовательности, ,оно содержит группу из а щ-разрядных сдвигающих регистров, вторую группу из и элементов И, первый.и второй элементы И, элемент запрета, элемент ИЛИ, второй, третий г чет, вертый элементы задержки, причем -й информационный вход устройства соединен с первым входом -го элемента И второй группы, выход кото, рого соединен с информационным входом 1-го сдвигающего регистра и третьим входом 1-го элемента ИЛИ группы, инверсный выход 1-го сдвигающего регистра соединен с вторым входом 1-го элемента И первой груп.пы и с -м входом первого элемента ; И, выход которого соединен с первым , входом второго элемента И и с инверсным входом элемента запрета, выход Й :которого соединен с первымвходом , первого элемента ИЛИ группы и вхоой ,домвторого элемента задержки, выход которого соединен с входом первого элемента задержки, выход которого соединен с входом третьего элемента задержки, выход которого.соединен с первым входом элемента ИЛИ, : выход которого соединен с входом четвертого элемента задержки, вторымивходами )-х элементов И вторбй груп,. пы и управляющими входами -х сдвига Мах регистров, тактовый вход уст ства соединен с прямым входом эл та запрета и вторым входом, второго ,элемента И, выход которого соединен вторым входом элемента ИЛИ, а выхбд четвертого элемента задержки соединен с вторыми входами -1)-х" элементов И второй группы и управляющими входами 15-1)-х сдвигающих регистров.40 45 50 55 60 65 Цель достигается тем, что в устройство для суммирования ш и-разрядных последовательно поступающих чисел, содержащее группу нз и счетных триггеров, первую группу из и эле-. ментов И, группу нз и элементов ИЛИ и первый элемент задержки, причем первые входы 1-х элементов И первой группы, где )=2,4. и соединены между собой и с входом первого элемента задержки, выход которого соединен с первыми входами (1-1)-х элементов И первой группы, выход -го элемента И первой группы, где х=1,2и, соединен с первым входом 1-го элемента ИЛИ ;руппы, выход которого соединен со Изобретение относится к вычислительной технике и может быть ис"пользовано в устройствах статистической обработки информации.Известно устройство для суммирования ш и-разрядных чисел, содержащее и суммирующих блоков, каждыйиз которых содержит Ь многовходовыходноразрядных сумматоров с сохранением переносов 113.Недостаток устройства - сложность и ограниченные функциональные возможности: при изменении хотябы одного из ш чисел массива необходимо вводить и суммировать весьмассив ш чисел, что затрудняетиспользование данного устройствадля статистической обработки непрерывно .поступающей последовательности чисел.Наиболее близким по техническойсущности к изобретению являетсяпараллельный накапливающий сумматор, содержащий в каждом разрядетриггер, элемент И и элемент ИЛИ,выход которого подключен к счетномувходу триггера соответствующегоразряда, а вход подключен к выходуэлемента И этого же разряда и единичному выходу триггера предыдуще-,го разряда сумматора, первые входыэлементов И подключены к информационным входам устройства, тактовыйвход устройства подключен к вторымвходам .элементов И четных разрядовсумматора непосредственно, а нечетных разрядов - через элемент задержки 2 3,Недостатком этого сумматора являются ограниченные функциональныевоэможности, так как этот сумматорвычисляет сумму всех поступившихна его входы чисел и не обеспечи вает вычисление суммы ш последнихпоступивших чисел,Целью изобретения является расширение функциональных возможностей устройства путем обеспечениявычисления суммы последних ш чиселиз.поступающей последовательности. 5 10 15 20 25 30 35 счетным входом -го счетного триггера, единичный выходкоторого являет ся -м выходом устройства и сое"динен с вторым входом (1+1)-го элемента ИЛИ группы, введены группа изп ш-разрядных сдвигающих регистров,вторая группа из п элементов И, первый и второй элементы И, элементзапрета, элемент ИЛИ, второй, третий и четвертый элементы задержки,причем 1-й информационный вход устройства соединен с первым входом-го элемента И второй группы, выход которого соединен с информационным входом -го сдвигающего регистра и третьим входом д-го элементаИЛИ группы, инверсный выход 1-госдвигающего регистра соединен свторым входом 1-го элемента И первой группы и с -м входом первогоэлемента И, выход которого соединенс первым входом второго элемента Ии с инверсным входом элемента запрета, выход которого соединен с первым входом первого элемента ИЛИгруппы и входом второго элементазадержки, выход которого соединенс входом первого элемента задержки,выход .которого соединен с входомтретьего элемента задержки, выходкоторого соединен с первым входомэлемента ИЛИ, выход которого соединен с входом четвертого элементазадержки, вторыми входами 1-х элементов И второй группы и управляющими входами 1-х сдвигающих регистров, тактовый вход устройства соединен с прямым входом элемента запрета и вторым входом второго элементаИ, выход которого соединен с вторым входом элемента ИЛИ, а выход четвертого элемента задержки соеди-. нен с вторыми входами (1-1)-х элементов И второй группы и управляющими .входами(1-1)-х сдвигающих регистров.На чертеже показана схема устройства.устройство содержит сдвигающие регистры 1-1, группы элементов И 2-2и 3-3, элементы И 4 и 5, элемент запрета б, группу элементов ИЛИ 7 -7, элемент ИЛИ 8, группусчетных триггеров 9-9, элементызадержки 10-13, информационные входы14-14 выходы 15-15 разрядов суммы, тактовый вход,16.Устройство работает следующим образом.В исходном состоянии в регистрах 1 -1 записаны нули, следовательно, йо одному входу открыт элемент И 5, триггеры 9-9 и - в нулевом состоянии. Первый импульс, посту пающий на тактовый вход 16 черезэлементы И 5 и ИЛИ 8, поступает навторые входы элементов И 3 -3 чет 2 Г 1ных разрядов, производит сдвиг врегистрах 1-1 четных разрядов и10 И 4 закрывается и открывается элемент запрета б. (ш+1)-й такто/вый импульс через элемент запретаб, элемент .ИЛИ 7 поступает на 155 счетный вход триггера 91, т.е. кмладшему разряду суммы, находящейся в триггерах 91-9 д, прибавляетсяединица. Этот же имйульс через элемент задержки 11 поступает на вто рые входы элементов И 2-2четныхразрядов и обеспечивает поступление четных разрядов первого числав обратном коде через элементы ИЛИ7-7 п на счетные входы триггеров 25 9 -9 и их сложение с суммой, находящейся в триггерах 9-9, Далееэтот же импульс через элементзадержки 10 поступает на первыевходы элементов И 2-2 нечетныхразрядов и обеспечивает поступление нечетных разрядов первого числа в обратном коде через элементыИЛИ 71-7 на счетные входы триггеров91-9нечетных разрядов и их сложение с суммой, находящейся втриггерах 9-9. Далее этот же сигнал через элемент задержки 12 посту 40 суммы ш последних чисел без необходимости постоянного пересчетасуммы всех.а чисел. Это позволяет запись четных разрядов первого чис- ность поступивших ш чисел, причемла в эти регистры, а также через в 1 т-х разрядах регистров 11-1,элементы ИЛИ 72-7 п - в триггеры где Е=1,2 ш, записывается9-9, Этот же имйульс через эле- (ш-к+1)-е число поступившей после"мент задержки 13 поступает на пер- довательности чисел. Если первоевые входы элементов И 3,-3 нечет-5 число из последовательности нульй-.1Уных разрядов, производит сдвиг вто на инверсных выходах всех регирегистрах 1 -1 . нечетных раэря- -тров единицы, элемент И 4.открытдов и запись нечетных разрядов пер.1 Л 4 я (ш+1)-й такт работы устройствавого числа в эти регистры, а также аналогичен предыдущим тактам. ЕсличеРез элементы ИЛИ 7, -7. - в тригге- :ке первое число не нуль, то элементры-9. . Следовательно, в первыхразрядах регистров 1 -1 п и в триггерах 9, -9 п записывается первое число из непрерывно поступающей последовательности чисел.Второй тактовый импульс черезэлементы И 5 и ИЛИ 8 поступает навторые входы элементов И 3 -3 четных разрядов, производит сдвиг в регистрах 1 -1 и запись четных разгрядов второго числа в эти регистры,а также обеспечивает их поступление через элементы ИЛИ 7-7 насчетные входы триггеров 92-9 четных разрядов. При поступлении четныхразрядов второго числа происходит.их сложение с четными разрядами первого числа, записанного в триггерах9-9 д следующим образом: при поступлений "О.ф состояние триггера не меняется, а при поступлении "1" состояние триггера изменяется на противоположное, причем при переходе триггера из единичного в нулевое состояние на единичном выходе этого триггера появляется сигнал переноса вследующий разряд, который суммируется со значением этого разряда, пает на первый вход элеменга ИЛИ 8и т.д. и производится запись следующегоЗатем второй тактовый импульс числа в регистры 1-1 и сложение счерез элемент задержки 13 поступа- суммой, находящейся в. триггерахет на вторые входы элементов И 34-3 91-9 и четных разрядов (ш+1)-го чиснечетных разрядов, производит сдвиг ла, а также их поступление черезв регистрах 1-1 нечетных раэря- элементы ИЛИ 7-7 п на счетные входыдов и запись нечетных разрядов вто- триггеров 92 -9 , и т.д. как описарого числа в эти регистры, а также нофобеспечивает их поступление через Таким образом, при поступленииэлементы ИЛИ 7 -7 днечетных раэ- (ш+2)-го тактового импульса изрядов на счетные входы триггеров суммы ш чисел вычитается .3-е из91-9 нечетньис разрядов и сложение поступающих чисел (путем сложенияс нечетными разрядами числа, запи суммы ш чисел с числом, дополнисанного в триггерах 9 1 -9 (по ана- льным к 2-му) и прибавляетсялогии со сложением четных разрядов), вновь поступившее (ш+1)-е число.Например, пусть в триггерах 9; -9 Следовательно, в триггерах 9-9 ййзаписано число 0111, а поступает всегда находится сумма ш последйихчисло 0011Тогда после первого 55 чисел из поступающей последовательсложения (четных разрядов) в триг- сигерах 91-9 запк:ывается числои1001, а после второго сложения Технико-экономический эффект(нечетных разрядов) - сумма 1010. изобретения заключается в расширеПри поступлении тактовых импуль .нии функциональных воэможностей:сов с третьего по ш-. й устройство устройство обеспечивает нахождениеработает аналогично. После ш-готактового импульса в триггерах 9-9изаписывается сумма ш чисел, а в регистрах 1-1- вся последователь оперативно вычислять сумму ш послед1075260 них чисел из непрерывно поступающей последовательности, что расширяет область примЕнения устройства,лСоставитель В. Горох Техред В,далекорей ректор, Ъ. ТяскоТираж 699 ИПИ Государственн о делам изобретен 5, Москва," Ж;фили ППП фПатентф, г. Ужгород, ул. Проектная,актор Р. Цицаз 499/42 например, для контроля качествасистем в процессе их функционирования. Подписного комитета СССРй и открытийаушская наб д. 4/

СмотретьЗаявка

3518603, 13.12.1982

ВОЙСКОВАЯ ЧАСТЬ 25840

ЕРОШКО ГЕННАДИЙ АНТОНОВИЧ, ШУБИНА НАТАЛЬЯ НИКОЛАЕВНА

МПК / Метки

МПК: G06F 7/50

Метки: последовательно, поступающих, разрядных, суммирования, чисел

Опубликовано: 23.02.1984

Код ссылки

<a href="https://patents.su/4-1075260-ustrojjstvo-dlya-summirovaniya-razryadnykh-posledovatelno-postupayushhikh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования -разрядных последовательно поступающих чисел</a>

Предыдущий патент: Сумматор-вычитатель по модулю

Следующий патент: Устройство для распределения заданий в сетях электронных вычислительных машин

Случайный патент: Роторный вагоноопрокидыватель