Устройство для управления памятью программ и данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

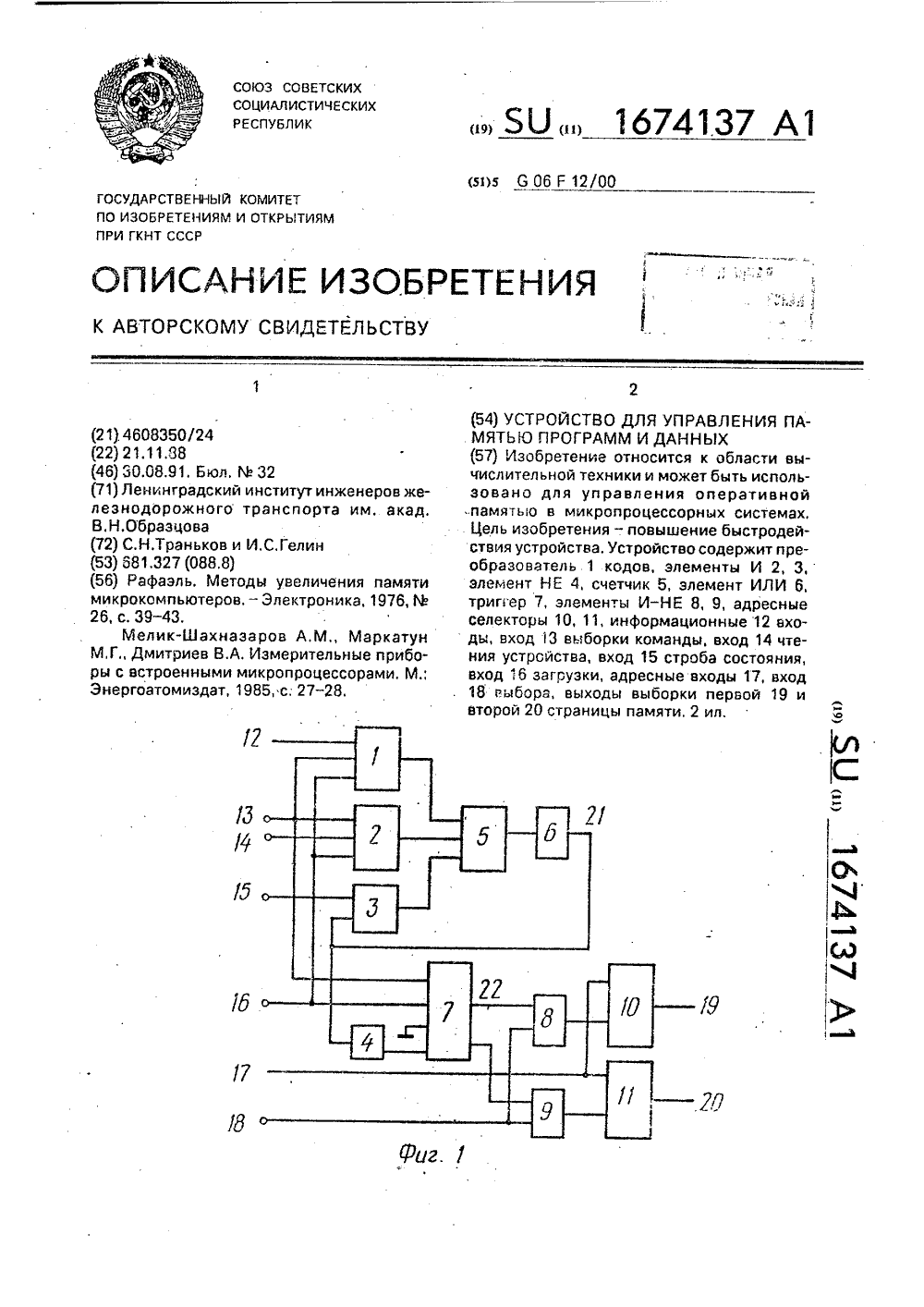

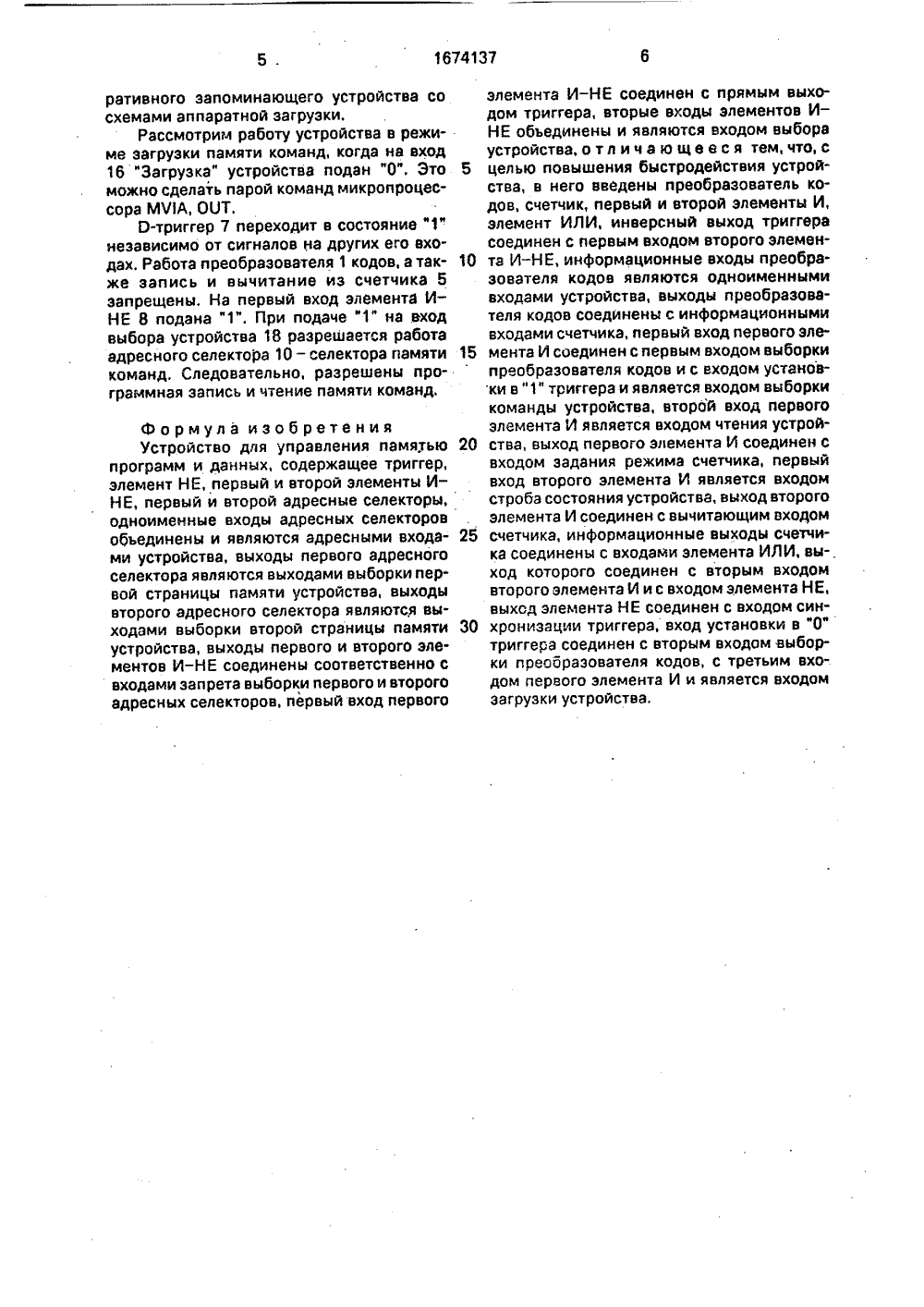

(91 ( 5)5 6 06 Г 12/О К АВТОРСКО ИДЕТЕЛ ЬСТВ нженеров жеа им. акад,Ге ичения памяти роника, 1976, М М., Маркатун ельные прибоцессорами. М,; 4 ь Ь 1 сэ сГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ИСАНИЕ ИЗОБ(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ ПРОГРАММ И ДАННЫХ(57) Изобретение относится к области вычислительной техники и может быть использовано для управления оперативной .памятью в микропроцессорных системах. Цель изобретения - . повышение быстродействия устройства, Устройство содержит преобразователь 1 кодов, элементы И 2, 3, элемент НЕ 4, счетчик 5, элемент ИЛИ 6, триггер 7, элементы И - НЕ 8, 9, адресные селекторы 10, 11, информационные 12 входы, вход 3 выборки команды, вход 14 чтения устройства, вход 15 строба состояния, вход 16 загрузки, адресные входы 17, вход 18 выбора, выходы выборки первой 19 и второй 20 страницы памяти, 2 ил.10 20 Изобретение относится к области вычислительной техники и может быть использовано для управления оперативнойпамятью в микропроцессорных системах.Цель изобретения - повышение быстродействия устройства.На фиг,1 приведена схема устройствадля управления памятью программ и данных; на фиг.2 - временная диаграмма работы устройства.На фиг.1 обозначены преобразователь1 кодов (может быть выполнен в виде постоянного запоминающего устройства), элементы И 2, 3, элемент НЕ 4, счетчик 5,элемент ИЛИ 6, триггер 7, элементы И-НЕ8, 9, адресные селекторы 10, 11, информационные входы 12, цхсд 13 выборки команды, вход 14 чтения 1,стройства, вход 15строба состояния, вход 16 загрузки, адресные входы 17 устройства, вход 18 выбораустройства, выходы выборки первой 19 ивторой 20.страницы памяти, выход 21 элемента ИЛИ, прямой выход 22 триггера.Информационные входы 12 устройстваподключены к шине данных микропроцессорной системы (на фиг,1 не показана), Входы устройства "Выборка команды" 13,"Чтение" 14, "Строб состояния" 15 подключены к выходам шины управления микропроцессорной системы М 1, ОВпч, ЗТВсоответственно. Вход 16 "Загрузка" устройства подключен к одному из разрядов выходного порта микропроцессорнойсистемы. Адресные входы устройства 17подключены к шине адреса микропроцессорной системы. Вход 18 выбора устройстваподключен к выходу "Обращение к памяти"шины управления микропроЦессорной системы, Выходы устройства "Выборка первойстраницы памяти" 19 и Выборка второйстраницы памяти" 20 подключены к входамвыборки кристаллов схем памяти команд ипамяти данных, соответственно схемы памяти на фиг.1 не показаны),В начальном состоян и входы 13-18 устройства и выходы 19, 20 устройства установлены в "0". Вход 16 устройстваустановлен в "1". Содержлмое счетчика 5 иО-триггера 7 равно нулю, В преобразователе 1 кодов по адресам, соответствующимкодам команд микропроцессора, записанадлина команды в бай 1-ах, апример для команды .НЮ по адресу 2 АН записан код 3,Рассмотрим работу устройства при выполнении микропроцессорной слстемнойкомандыНЮ. Временная диаграмма работы устройства представлена на фиг.2В первом машинном цикле на второмвходе элемента И 3 установлен "0", запрещая прохождение импульса с входа 15 25 30 35 40 45 ,Щ 55"Строб состоянля" устройства на вычитающлй вход счетчика 5. На входе 13 "Выборка команды" устройства устанавливается "1", разрешающая работу преобразователя кодов 1 и устанавливающая в "1" О-триггер 7. На первый вход элемента И-НЕ подается "1", подготавливая его работу, На вход выбора устройства 18 подается "1", На выходе элемента И-КЕ 8 устанавливается "0", разрешающий работу адресного селектора 10, т.е, выборку кода команды из памяти команд, Код команды НЮ 2 АН псступает на информационные входы 12 устройства, на выходе преобразователя кодов 1 устанавливается код 3. Задний фронт импульса на входе 14 "Чтение" устройства, проходя через подготовленный элемент И 2, инициирует запись кода 3 в счетчик 5, На выходе элемента ИЛИ 6 устанавливается "1", которая поступает на второй вход элемента И 3, подготавливая его работу. На входе 13 "Выборка команды" устройства устанавливает "О", запрещая работу преобразователя кодов 1 и запись в счетчик 5. На входе выбора устройства 18 устанавливается "О", запрещая работу схем памяти.Во втором и третьем машинных циклах импульс с входа 15 "Строб состояния" устройства через подготовленный элемент И 3 поступает на вычитающий вход счетчика 5. Содержимое счетчика 5 равно 2, а в третьем машинном цикле - 1. Состояние О-триггера 7 остается неизменным. Второй и третий байты кода команды последовательно выбираются из памяти команд.В четвертом машинном цикле импульс с входа 15 "Строб состояния" устройства через подготовленный элемент И 3 поступает на вычитающий вход счетчика 5. Содержимое счетчика 5 становится равным нулю. На выходе элемента ИЛИ 6 формируется заднлй фронт логического сигнала, который инвертируется на элементе НЕ 4 и переводлт О-триггер в состояние "О". На первом входе элемента И-НЕ 9 устанавливается значение "1", подготавливая его работу. На втором входе элемента К 3 устанавливается значение "О", запрещая последующие вычитания из счетчика 5. На вход выбора устройства 18 подается "1". На выходе элемента И-НЕ 9 устанавливается "0", разрешая работу адресного селектора 11, т.а, выборку данных из памяти данных. В конце машинного цикла на входе выбора устройства ,8 устанавливается "0", запрещая работу схем памяти.В пятом машинном цикле второй байт данных выбирается иэ памяти данных,Предполагается, что для устройства память команд выполнена в виде ПЗУ или опе 1674137ративного запоминающего устройства со схемами аппаратной загрузки,Рассмотрим работу устройства в режиме загрузки памяти команд, когда на вход 16 "Загрузка" устройства подан "0". Это 5 можно сделать парой команд микропроцессора МИА, ООТ.Р-триггер 7 переходит в состояние "1" независимо от сигналов на других его входах, Работа преобразователя 1 кодов, а так же запись и вычитание из счетчика 5 запрещены, На первый вход элемента ИНЕ 8 подана "1". При подаче "1" на вход выбора устройства 18 разрешается работа адресного селектора 10 - селектора памяти 15 команд. Следовательно, разрешены программная запись и чтение памяти команд. Формула изобретенияУстройство для управления памятью 20 программ и данных, содержащее триггер, элемент НЕ, первый и второй элементы ИНЕ, первый и второй адресные селекторы, одноименные входы адресных селекторов объединены и являются адресными входа ми устройства, выходы первого адресного селектора являются выходами выборки первой страницы памяти устройства, выходы второго адресного селектора являются выходами выборки второй страницы памяти 30 устройства, выходы первого и второго элементов И-НЕ соединены соответственно с входами запрета выборки первого и второго адресных селекторов, первый вход первого элемента И-НЕ соединен с прямым выходом триггера, вторые входы элементов И - НЕ обьединены и являются входом выбора устройства, о т л и ч а ю щ в е с я тем, что, с целью повышения быстродействия устройства, в него введены преобразователь кодов, счетчик, первый и второй элементы И, элемент ИЛИ, инверсный выход триггера соединен с первым входом второго элемента И - НЕ, информационные входы преобразователя кодов являются одноименными входами устройства, выходы преобразователя кодов соединены с информационными входами счетчика, первый вход первого элемента И соединен с первым входом выборки преобразователя кодов и с входом установки в "1" триггера и является входом выборки команды устройства, второй вход первого элемента И является входом чтения устройства, выход первого элемента И соединен с входом задания режима счетчика, первый вход второго элемента И является входом строба состояния устройства, выход второго элемента И соединен с вычитающим входом счетчика, информационные выходы счетчика соединены с входами элемента ИЛИ, вы-, ход которого соединен с вторым входом второго элемента И и с входом элемента НЕ, выход элемента НЕ соединен с входом синхронизации триггера, вход установки в "0" триггера соединен с вторым входом выборки преобразователя кодов, с третьим входом первого элемента И и является входом загрузки устройства.

СмотретьЗаявка

4608350, 21.11.1988

ЛЕНИНГРАДСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА ИМ. АКАД. В. Н. ОБРАЗЦОВА

ТРАНЬКОВ СЕРГЕЙ НИКОЛАЕВИЧ, ГЕЛИН ИГОРЬ САМУИЛОВИЧ

МПК / Метки

МПК: G06F 12/00

Метки: данных, памятью, программ

Опубликовано: 30.08.1991

Код ссылки

<a href="https://patents.su/4-1674137-ustrojjstvo-dlya-upravleniya-pamyatyu-programm-i-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для управления памятью программ и данных</a>

Предыдущий патент: Устройство для отладки программ

Следующий патент: Устройство адресации памяти

Случайный патент: Устройство для функционально-параметрического контроля логических элементов