Линейный интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

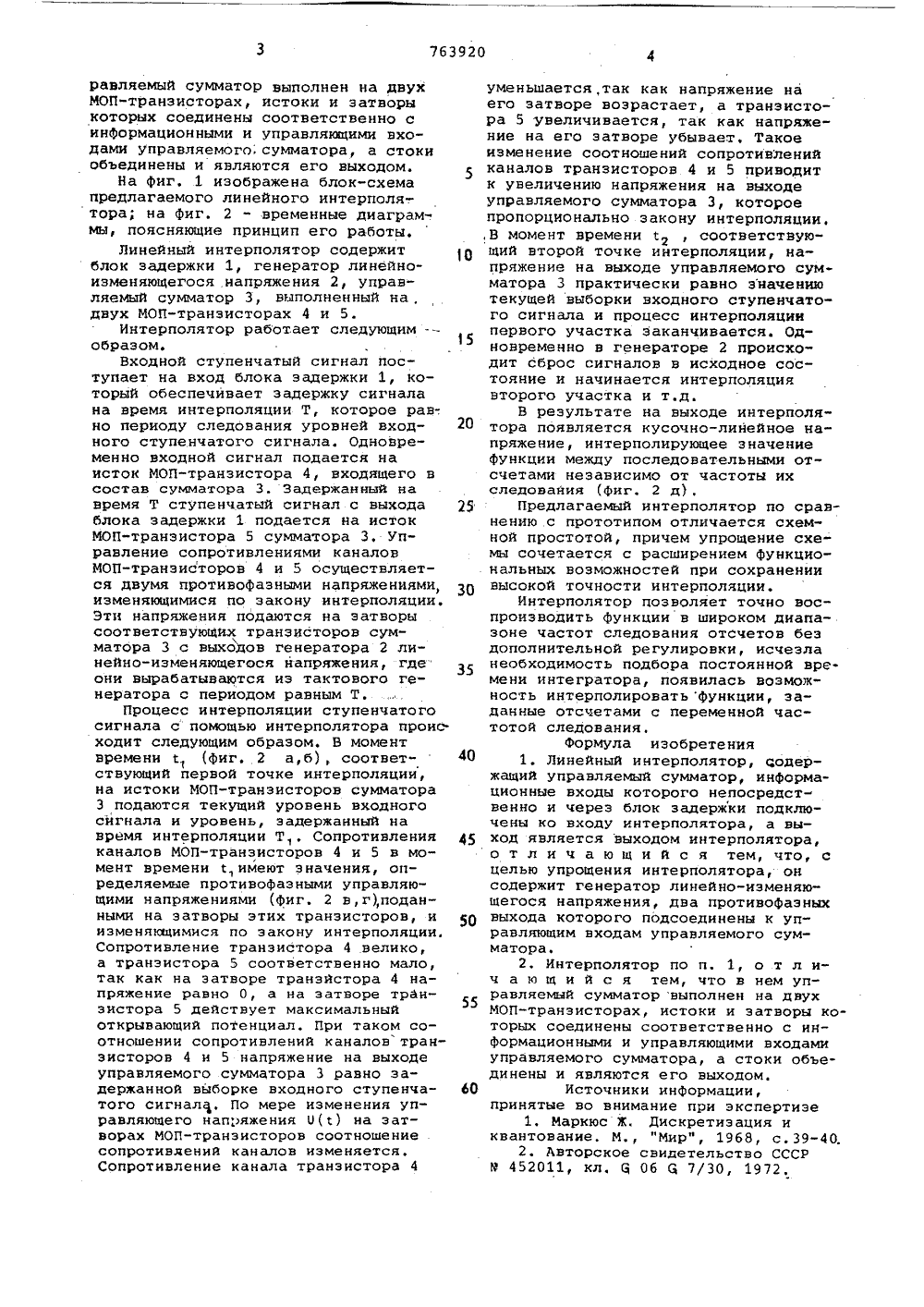

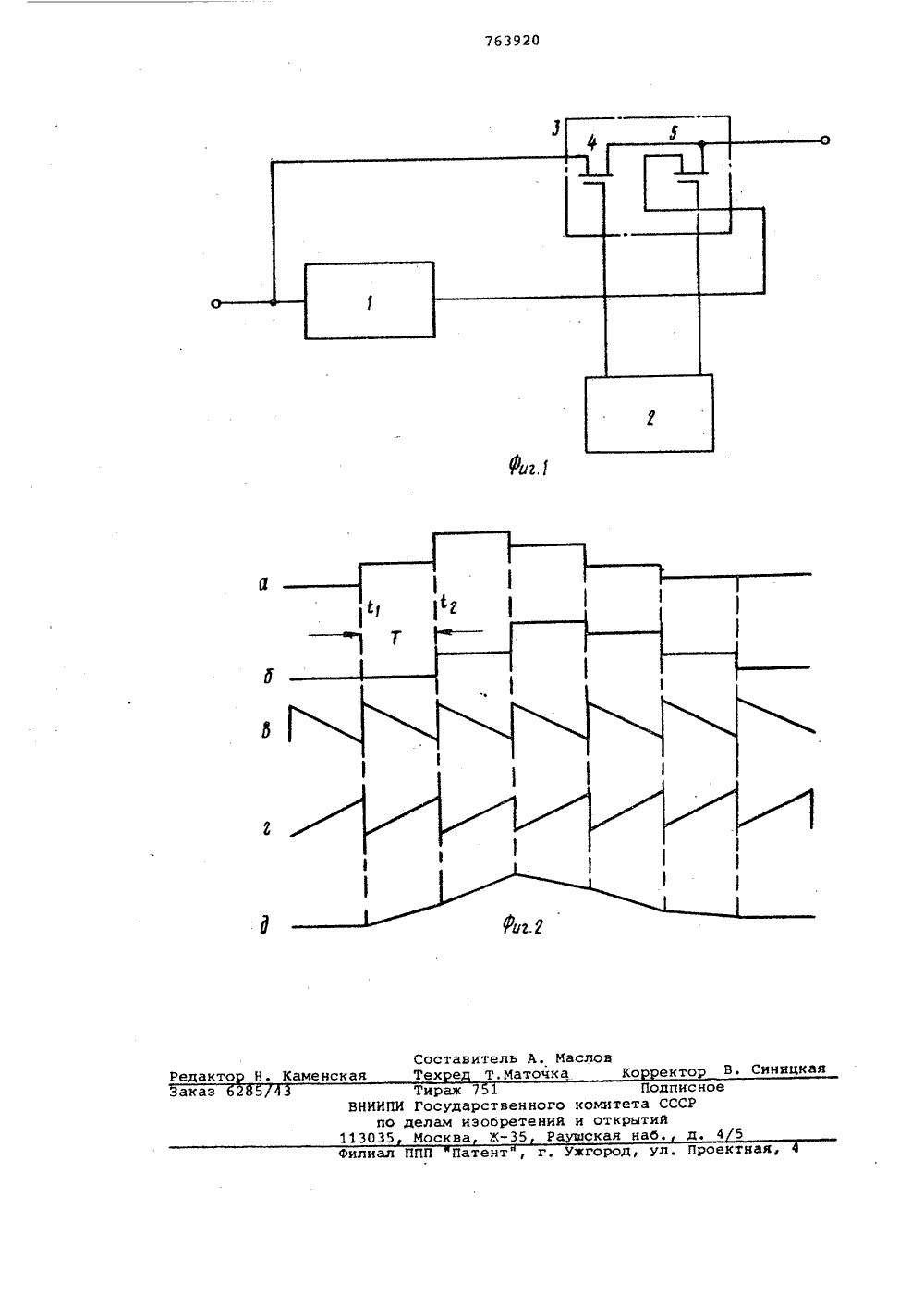

Союз Советскик Социалистических Республик(51) м. (, (3 06 6 7/30 Государственный комитет СССР но делам изобретений н открытий(54) ЛИНЕИНЫИ ИНТЕРПОЛЯТОР Изобретение относится к области вычислительной техники, а именно к устройствам для интерполяции Функций.5Для сглаживания ступенчатых сигналов наиболее эффективна линейная интерполяция, обеспечивающая высокую точность воспроизведения заданной кривой (Функции),при значительно более узкой полосе пропускания по сравнению с другими способами интерполяции, Фильтр, выполняющий операцию линейной интерполяции, имеет передаточную функциюНр)=-1- + "-3-в тр СИзвестен линейный интерполятор, содержащий для реализации такой передаточной функции блок задержки, сумматор и два интегратора 11 . Такая структура линейного интерполятора достаточна сложна и громоздка при реализации ее на практике.Наиболее близким по технической сущности к данному изобретению является линейный интерполятор, содержащий блок задержки, сумматор, интегратор и ключевую схему 2 . Такой линейный интерполятор позволяетдостаточно точно интерполировать значение Функций между последовательными отсчетами. Но для осуществленияпроцесса интерполяции с достаточновысокой степенью точности в таком интерПоляторе необходим точный подбор постоянной времени интегратора,соответствующей периоду следованияступенек входного сигнала.Весьма существеннюю недостаткомявляется также невозможность интерполирования функций, заданных.отсчетами с переменной частотой следования.Целью изобретения является упрощение интерполятора,Поставленная цель достигается тем,что линейный интерполятор, содержа"щий управляеьатй сумматор, информационные входы которого непосредственнои через блок задержки подключены ковходу интерполятора, а выход является выходом интерполятора, содержитгенератор лннейно-изменяющегося напряжения, два противофазных выходакоторого подсоединены к управляющимвходам управляемого сумматора, атакже тем, что в интерполяторе уп60 равляемый сумматор выполнен на двухМОП-транзисторах, истоки и затворыкоторых соединены соответственно синформационными и управляющими входами управляемого, сумматора, а стокиобъединены и являются его выходом.На фиг, 1 изображена блок-схемапредлагаемого линейного интерполя-.тора; на фиг. 2 " временные диаграммы, поясняющие принцип его работы,Линейный интерполятор содержитблок задержки 1, генератор линейноизменяющегося .напряжения 2, управляемый сумматор 3, выполненный на,двух МОП-транзисторах 4 и 5.Интерполятор работает следующим обраэом,Входной ступенчатый сигнал поступает на вход блока задержки 1, который обеспечивает задержку сигналана время интерполяции Т, которое рав-.но периоду следования уровней входного ступенчатого сигнала. Одновременно входной сигнал подается наисток МОП-транзистора 4, входящего всостав сумматора 3. Задержанный навремя Т ступенчатый сигнал с выходаблока задержки 1 подается на истокМОП-транзистора 5 сумматора 3. Управление сопротивлениями каналовМОП-транзисторов 4 и 5 осуществляется двумя противофазными напряжениями,изменяющимися по закону интерполяции,Эти напряжения подаются на затворысоответствующих транзисторов сумматора 3 с выходов генератора 2 линейно-изменяющегося напряжения, гдеони вырабатываются из тактового гЕнератора с периодом равным Т.Процесс интерполяции ступенчатогосигнала с помощью интерполятора происходит слецующим образом, В моментвремени с (фиг. 2 а,б), соответствующий первой точке интерполяции,на истоки МОП-транзисторов сумматора3 подаются текущий уровень входногосйгнала и уровень, задержанный навремя интерполяции Т Сопротивленияканалов МОП-транзисторов 4 и 5 в момент времени с имеют значения, определяемые противофазными управляющими напряжениями (фиг. 2 в,г),поданными на затворы этих транзисторов, иизменяющимися по закону интерполяции.Сопротивление транзистора 4 велико,а транзистора 5 соответственно мало,так как на затворе транэйстора 4 напряжение равно О, а на затворе транзистора 5 действует максимальныйоткрывающий поТенциал. При таком соотношении сопротивлений каналов транзисторов 4 и 5 напряжение на выходеуправляемого сумматора 3 равно задержанной выборке входного ступенчатого сигнала. По мере изменения управляющего напряжения Ц(с) на затворах МОП-транзисторов соотношение .сопротивлений каналов изменяется.Сопротивление канала транзистора 4 5 20 25 ЗО 35 40 45 50 55 уменьшается,так как напряжение наего затворе возрастает, а транзистора 5 увеличивается, так как напряжение на его затворе убывает, Такоеизменение соотношений сопротивленийканалов транзисторов 4 и 5 приводитк увеличению напряжения на выходеуправляемого сумматора 3, которое пропорционально закону интерполяцииВ момент времени, соответствующий второй точке интерполяции, напряжение на выходе управляемого сумматора 3 практически равно значениютекущей выборки входного ступенчатого сигнала и процесс интерполяциипервого участка заканчивается. Одновременно в генераторе 2 происхо"дит сброс сигналов в исходное состояние и начинается интерполяциявторого участка и т.д,В результате на выходе интерполятора появляется кусочно-линейное напряжение, интерполирующее значениефункции между последовательными отсчетами независимо от частоты ихследования (Фиг. 2 д).Предлагаемый интерполятор по сравнению с прототипом отличается схемной простотой, причем упрощение схемы сочетается с расширением функциональных возможностей при сохранениивысокой точности интерполяции.Интерполятор позволяет точно воспроизводить функции в широком диапазоне частот следования отсчетов бездополнительной регулировки, исчезланеобходимость подбора постоянной времени интегратора, появилась возможность интерполироватьфункции, заданные отсчетами с переменной частотой следования.Формула изобретения1. Линейный интерполятор, содержащий управляемый сумматор, информационные входы которого непосредственно и через блок задержки подключены ко входу интерполятора, а выход является выходом интерполятора,о т л и ч а ю щ и й с я тем, что, сцелью упрощения интерполятора, онсодержит генератор линейно-изменяющегося напряжения, два противофаэныхвыхода которого подсоединены к управляющим входам управляемого сумматора,2. Интерполятор по и. 1, о т л ич а ю щ и й с я тем, что в нем управляемый сумматор выполнен на двухМОП-транзисторах, истоки и затворы ко"торых соединены соответственно с информационными и управляющими входамиуправляемого сумматора, а стоки объединены и являются его выходом. Источники информации,принятые во внимание при экспертизе 1, Маркюс й. Дискретизация и квантование. М., "Мир", 1968, с.39-40. 2. Авторское свидетельство СССР Р 452011, кл, Я 06 6 7/30, 1972,763920 Составитель А. МасловТех ед Т.Маточка Ко ек Синицкая Каменск едак ак Подписно ета СССР ытий наб. д.13035 Проектная Тираж 7ВНИИПИ Государственного комит по делам изобретений и откр Москва ХРа скаяилиал ППП Патент , г. Ужгород

СмотретьЗаявка

2600641, 03.04.1978

ПРЕДПРИЯТИЕ ПЯ Р-6886

ШАТАЛИН ЮРИЙ ПАВЛОВИЧ, ШУСТОВ НИКОЛАЙ ПЕТРОВИЧ, МАТВЕЕВ ВЯЧЕСЛАВ ЛЬВОВИЧ, СЕРГЕЕВ НИКОЛАЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор, линейный

Опубликовано: 15.09.1980

Код ссылки

<a href="https://patents.su/3-763920-linejjnyjj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Линейный интерполятор</a>

Предыдущий патент: Функциональный преобразователь

Следующий патент: Устройство для решения операторных уравнений

Случайный патент: Способ ушивания культи бронха при пульмонэктомии