Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 439811

Авторы: Айтхожаева, Барашенков

Текст

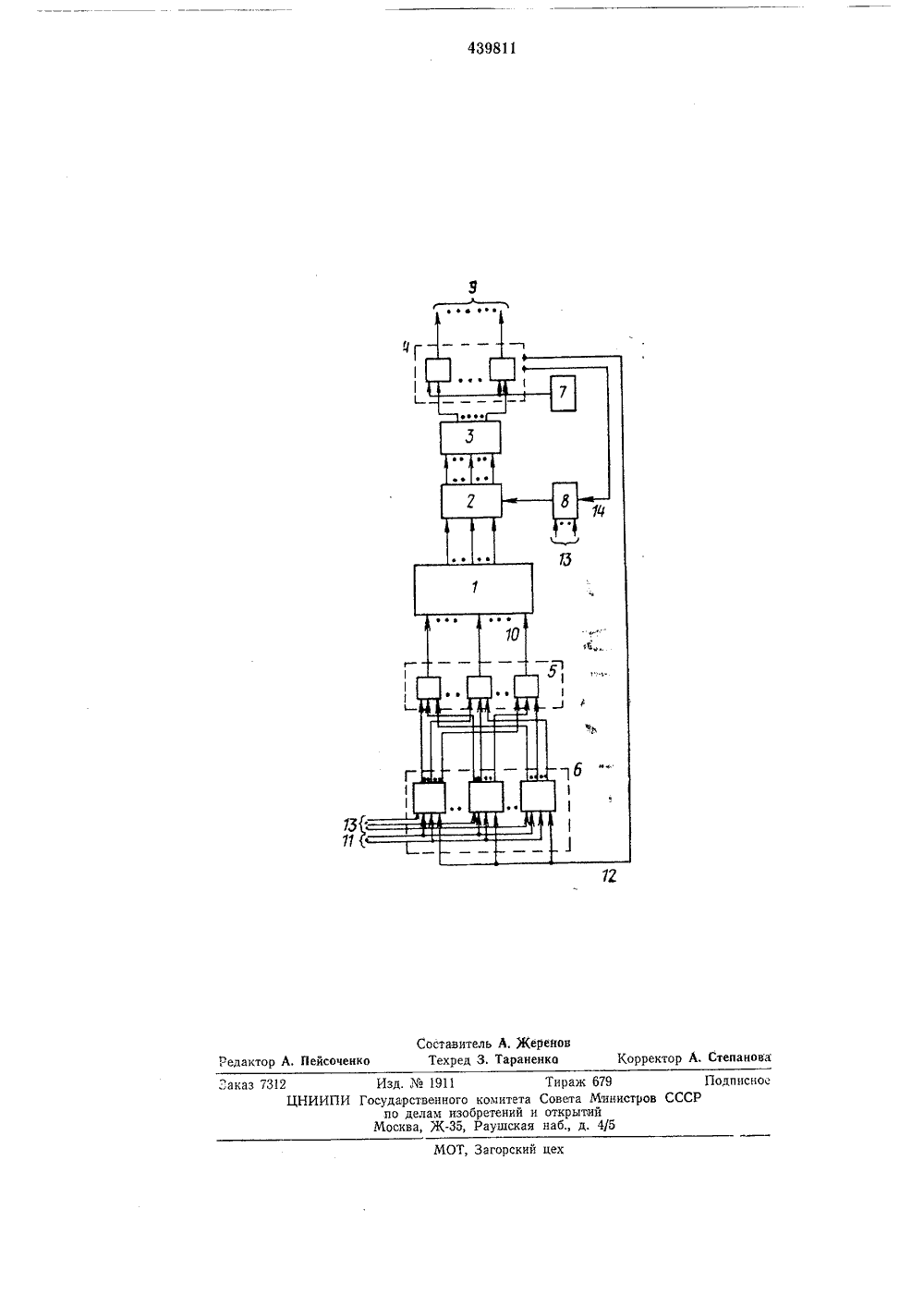

ОПИСАНИЕ 1 и 439811ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциал истиыескихРеспублик 61) Зависимое явт. свидетельств 22) Заявлено 03 72 (21) 176653318-2. С 061%16 51) с присоедииеиисм заявки Л Государстееииыи кометеСовета Министров СССРпо делам иаооретеиийи откритий.В,Б шенков н Заявитель нинградскии ордена Ленина электротехническин инсти им, В. И. Ульянова (Ленина) РОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИ Г 4 1Изобретение относится к области вычислительной теники.Известны микропрограммные устройства управления, при помощи которых осуществляется дифференциальное програътмирование, т. е. при записи очередной команды указываются только изменения в кодах операции и адресов по сравненио с предыдущей командой, содержащие регистр команды, регистр адреса для управления записью и считыванием из памяти, регистр для модификации адреса, входной-выходной регистр памяти и логический коъыутято 1, олокцруОщий передачу знаков из регистра ия. яти в регистр команды, когда данные знаки должны сохраняться от старой команды,Для сокращения оборудования и повышения оыстродействия в предлагаемое устройство введены сумматор и схема управления сумматором, первый вход которой соединен с первым выходом признаков блока ключей, Второй гыход признаков блока ключей подклочеи к управляющему входу логического коммутатора, первый вход которого соединес первим входом устройства. Второй вход устройства подклочен ко вторым входам логиеского коммутатора и сх.мь управления сумматором, выход которой соединен с первым входом суюатора. Второй вход сумматора подключен к выходу блока памяти, а выход сумматора сосдш.с. со входом дешифрагора.На чертеже представлена схема описываемого устройства.5 Уст 101 ство солеркит олок 1 пях 1 яти, сумматор 2, дешифратор 3, блок 4 клочей, блок 5 схемы ИЛИ, логический коммутатор 6, генератор 7 тактовых импульсов и схему 8 управления сумматором. Блок 1 памяти сое О дицеи с сумматором 2, который осуществляетсуммирование (вычитаие) кода, считанного из бпокя памяти, с кодом ирслыдущей, уже реализованной микрокомянды. Дешифратор 3 дешифртрует код микрокомаиды. Выходы 5 лсшп.рратора связаны с блоком 4 ключей, выполненным, например, в виде схем И - ИЛИ, через которые при помощи тактового импульса от генератора 7 с выхода 9 устройства выдается микрокоманда иа управ ляемые схемы. Выборка разностей кодов изблока 1 памяти осуществляется путем подачи сигнала от многовыходных последовательных схем логического коммутатора 6 через схемы ИЛИ блока 5 иа одну нз птиц 10 считыва ция, 1-1 а входы схем, управ,яопих выборкойкодов из блока памяти, по шинам, подключенным ко входу 11, поступяот признаки условных переходов, а по итиням 12 от схем И - ИЛИ блока 4 - признаки выполняю щихся микрокоманд. Поизиак выполнения3той или иной микропрограммы, поступающий по шинам, подключенным ко входу 13, выбирает для работы ту или иную схему коммутатора 6.Через схему 8 последние микрокоманды каждой микропрограммы устанавливают сумматор в нулевое состояние. Последние микро- команды поступают по шинам 14 от схем И - ИЛИ блока 4 и управляются признаком выполнения определеняой микропрограммы, поступающим на схему 8 по шинам, подключенным ко входу 13.Устройство работает следующим образом.Последней микрокомандой выполненной микропрограммы устройство устанавливается в исходное состояние. На выходе дешифратора, а следовательно, на выходе 9 и шинах 12 и 14 сигна,лы отсупствуют. Поступающий на вход 13 устройства признак выполнения определенной микропрограммы включает в работу соответствующую схему коммутатора 6, которая через схемы ИЛИ блока 5 выдает сигнал на одну из шин 10 считывания. Из блока 1 памяти считывается код первой микрокоманды, который подается на счетные входы триггеров сумматора 2, складывается с нулевым кодом, хранящимся на сумматоре, и с его выходапоступает на входы дещифратора 3. С приходом тактового импульса от генератора 7 микрокоманда с выходов блока 4 по шинам поступает с выхода 9 на управляемые схемы. Признаки выполняющихся микрокоманд с выхода блока 4 по шинам 12 поступают на коммутатор 6. На выходе коммутатора появляется сигнал, который по одной из шин 10 осуществляет считывание кода из блока памяти, представляющего собой разность между кодом выполняющейся микрокоманды и кодом следующей макрокоманды. Сумматор 2 осуществляет сложение (вычитание) и формирует код следующей микроюманды. Полученный код дешифруется, и после при. хода тактового импульса не выходе 9 появ. ляются управляющие сигналы. 4398114Такие процессы продолжаюгся до тех пор,пока на выходах блока 4 не появляются сигналы признаков последней микрокоманды, Они поступают на логическую схему 8, на уп 5 равляющие входы которой со входа 13 уст. ройства подается признак выполнения данноймикропрограммы. С выхода схемы 8 снимается сигнал уста 1 новюи су,мматора 2 в нулевое состояние. Число отличающихся разностей коО дов может быть при соответствующем кодировании микрокоманд достагочно малым, что дает возможность сократить объем памяти.Изменение мякропрограммы не сказывается на содержащуюся в блоке памяти информа 15 цию. Перестройка устройства на выполнениедругой микропрограммы требует только изменения внешних соединений.20 П р едм ет изобретенияМикропрограммное устройство управления, содержащее блок памяти, дешифратор, выход которого через блок ключей соединен 25 с выходом устройства, логический коммутатор, выходы которого через блок схем ИЛИ соединены со входами блока памяти, и генератор тактовых импульсов, соединенный выходом со входом блока ключей, отличающее ся тем, что, с целью сокращения оборудования и повышения быстродействия, в него введены сумматор и схема управления сумматором, первый вход которой соединен с первым выходом признаков блока ключей, второй вы ход признаков которого подключен к управляющему входу логического коммутатора, первый вход которого соединен с первым входом устройства, второй вход которого подключен ко вторым входам логического комму татора и схемы управления сумматором, выход которой соединен с первым входом сумматора, второй вход которого подключен к выходу блока памяти, а выход сумматора соединен со входом дешифратора.ейсоченко Изд.1911 Тираж 679осударственного комитета Совета Министров Спо делам изобретений и открытийМосква, Ж, Раушская наб д. 4/5 Подписное НИИПИ ОТ, Загорский цех Редактор А Заказ 7312 ставитель А. ЖереиовТехред 3, Тараненка Корректор А. Степанова

СмотретьЗаявка

1766533, 03.04.1972

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА ЛЕНИНА

БАРАШЕНКОВ ВАЛЕРИЙ ВИКТОРОВИЧ, АЙТХОЖАЕВА ЕВГЕНИЯ ЖЕМОЛХАНОВНА

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммное

Опубликовано: 15.08.1974

Код ссылки

<a href="https://patents.su/3-439811-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство обмена

Следующий патент: Устройство для прерывания программ

Случайный патент: Вращающийся разрядник