Устройство для моделировавания технологии программирования

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

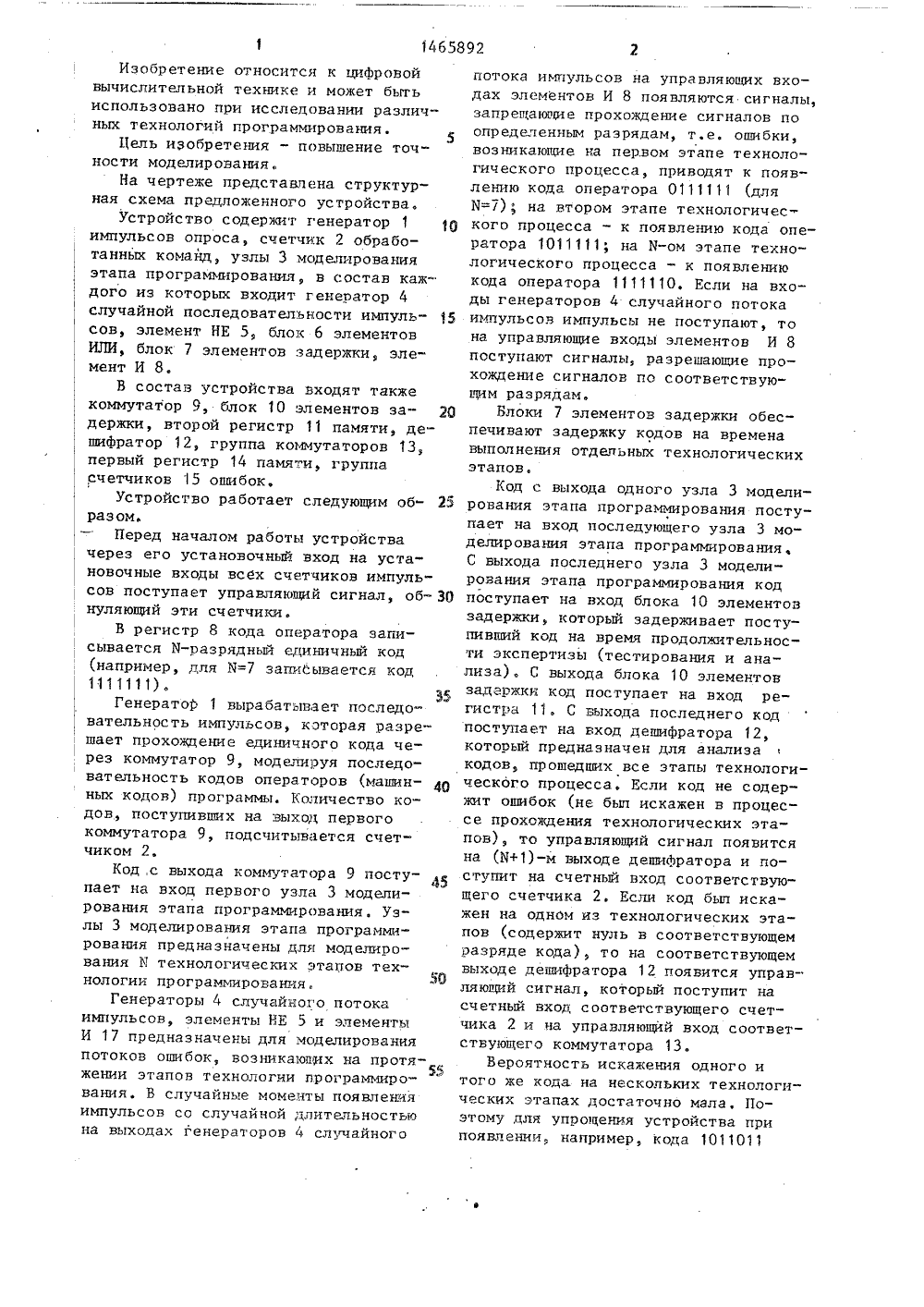

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 0 1465892 15/20 04 С ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ЗОБРЕТЕНИЯ ЬСТВУ МУ СВИ(54) УСТРОЙСТВО ДЛЯ МОДТЕХНОЛОГИИ ПРОГРАММИРОВАН(57) Изобретение относитсвой вычислительной техникизобретения - повышение тделирования технологии пр ство вания. Ус технологи и прогржит генератор 1счетчик 2 обрабо3 моделированияния, в состав кадит генератор 4 ул ва тво СССР20, 1986.о СССР20, 1987, ЕЛИРОВАНИЯИЯя к цифрое. Цельочности мо- ограммироельности импу ок 6 элемент тов задержки, устройства вх блок 10 элеме регистр 11 памяти, дешигруппа коммутаторов 13гистр 14 памяти, группошибок, 1 ил. ратор 12,первый ресчетчиков 1 ОПИСА Н АВТОРСНО для моделированияаммирования содеримпульсов опроса,таиных комаиц, узлыэтапа программироваждого из которых вхослучайной последоваьсов, элемент НЕ 5,в ИЛИ, блок 7 элеменлемент И 8. В составят также коммутатор 9,ов задержки, второйИзобретение относится к цифровойвычислительной технике и может бытьиспользовано при исследовании различных технологий программирования.5Цель иэобретения - повышение точности моделированияНа чертеже представлена структурная схема предложенного устройства,Устройство содержит генератор 1 10импульсов опроса, счетчик 2 обработанных команд, узлы 3 моделированияэтапа программирования, в состав каждого из которых входит генератор 4случайной последовательности имнульсов, элемент НЕ 5, блок 6 элементовИЛИ, блок 7 элементов задержки, элемент И 8,В состав устройства входят такжекоммутатор 9, блок 10 элементов за Одержки, второй регистр 11 памяти, дешифратор 12, группа коммутаторов 13,первый регистр 14 памяти, группасчетчиков 15 ошибок,Устройство работает следующим образом.- Перед началом работы устройствачерез его установочный вход на установочные входы всех счетчиков импульсов поступает управляющий сигнал, об- ЗОнуляющий эти счетчики.В регистр 8 кода оператора записывается И-разрядный ециничный код(например, для И=7 записывается код1111111) .Генератор 1 вырабатывает последовательность импульсов, которая разрешает прохождение единичного кода через коммутатор 9, моделируя последо"вательность кодов операторов (машин Оных кодов) программы. Количество кодов, поступивших на выход первогокоммутатора 9, подсчитывается счетчиком 2.Код,с выхода коммутатора 9 поступает на вход первого узла 3 моделирования этапа программирования. Узлы 3 моделирования этапа программирования предназначены для моделирования И технологических этапов технологии программирования,Генераторы 4 случайного потокаимпульсов, элементы НЕ 5 и элементыИ 17 предназначены для моделированияпотоков ошибок, возникающих на протяжении этапов технологии программиро 55вания. В случайнь.е моменты появленияимпульсов со случайной длительностьюна выходах генераторов 4 случайного потока импульсов на управляющих входах элементов И 8 появляются сигналы,запрещающие прохождение сигналов поопределенным разрядам, т. е. ошибки,возникающие на первом этапе технологического процесса, приводят к появлению кода оператора 0111111 (дляИ=7); на втором этапе технологического процесса - к появлению кода оператора 1011111; на И-ом этапе технологического процесса - к появлениюкода оператора 1111110. Если на входы генераторов 4 случайного потокаимпульсов импульсы не поступают, тона управляющие входы элементов И 8поступают сигналы, разрешающие прохождение сигналов по соответствующим разрядам,Блоки 7 элементов задержки обеспечивают задержку кодов на временавыполнения отдельных технологическихэтапов.Код с выхода одного узла 3 моделирования этапа программирования поступает на вход последующего узла 3 моделирования этапа программирования,С выхода последнего узла 3 моделирования этапа программирования кодпоступает на вход блока 10 элементовзадержки, который задерживает поступивший код на время продолжительности экспертизы (тестирования и анализа). С выхода блока 10 элементовзадержки код поступает на вход регистра 11. С выхоца последнего кодпоступает на вход дешифратора 12,который предназначен для анализакодов, прошедших все этапы технологического процесса. Если код не содержит ошибок (не бып искажен в процессе прохождения технологических этапов), то управляющий сигнал появитсяна (И+1)-и выходе дешифратора и поступит на счетный вход соответствующего счетчика 2, Если код был искажен на одном из технологических этапов (содержит нуль в соответствующемразряде кода), то на соответствующемвыходе дешифратора 12 появится управляющий сигнал, которыи поступит насчетный вход соответствующего счетчика 2 и на управляющий вход соответствующего коммутатора 13.Вероятность искажения одного итого же кода на нескольких технологических этапах достаточно мала, Поэтому,цля упрощения устройства припоявлении, например, кода 10110111465892 1 О 20 Формула и з о бр ет ения Корректор М. Пожо Заказ 1813 Тираж бб 9 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб д. ц/5 Производственноиздательский комбинат "Патент", г.ужгород у.з, Гагарина,101(для И=7) управляющий сигнал появится только на втором выходе дешифратора 12, т.е. код будет отправлен надоработку на второй технологическийэтап (на технологический этап с меньшим порядковым номером) . На информационные входы коммутатора 13 поступает исходный единичный код с выхода регистра 8 кода оператора. При появлении управляющего сигнала на управляющем входе одного из коммутаторов 13 на его выходе появляется единичный код, который поступит на второй вход соответствующего узла 3 этапа, Тем самым моделируется процесс возвращения ошибочных кодов на доработку на соответствующий технологический этап. Устройство для моделирования технологии программирования, содержащее 25 генератор импульсов опроса, выход которого соединен со счетным входом счетчика обработанных команд, группу счетчиков ошибок и И узлов моделирования этапа программирования(И - чис ло этапов программирования), каждый из которых состоит из блока элементов ИЛИ, генератора случайной последовательности импульсов, элемента НЕ, блока элементов задержки и элемента И, выходы блока элементов ИЛИ соединены соответственно с входами блока элементов задержки, выход генератора случайной последовательности импульсов в каждом узле моделирова ния этапа программирования через элемент НЕ соединен с первым входом элемента И своего узла моделирования этапа программирования, установочные входы всех счетчиков объединены и 45 являются установочным входом устрой" ства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования, оно дополнительно содержит первый регистр памяти, коммута 50 тор, группу коммутаторов и последоваСоставитель В. ФукаРедактор М, Келемеш Техред Л.Олийнык тельно соединенные блок элементов задержки, второй регистр памяти и дешифратор, причем разрядные входыпервого регистра памяти являются информационными входами устройства, аразрядные выходы первого регистра памяти соединены соответственно с информагвгонными входами коммутаторауправляющий вход которого подключенк выходу генератора импульсов опроса,а выходы коммутатора подключены соответственно к входам первой группыблока элементов ИЗПг первого узла моделирования этапа программирования,К-й выход блока элементов задержкиК-го узла моделирования этапа прог"раммирования (К=1, М) подключен квторому входу элемента И своего узламоделирования этапа программирования, остальные выходы блока элементовзадержки К-го узла моделирования этапа программирования и выход элементаИ К-гс узла моделирования этапа программирования подключены соответственно к входам первой группы блокаэлементов ИЛИ (К+1)-го узла моделирования этапа программирования, а остальные выходы блока элементов задержки К-го узла моделирования этапапрограммирования и выход элемента ИК-го узла моделирования этапа программирования подключены соответственно к входам бпока элементов задержки устройства, разрядные выходы первого регистра памяти соединены соответственно с информационными входамикоммутаторов группы, информационныевыходы которых подключены соответственно к входам второй группы блокаэлементов ИЛИ соответствующего узламоделирования этапа программирования,-й выход дешифратора (=1, И) соединен со счетным входом .-го счетчикаошибок группы и управляющим входом-го коммутатора группы, а (И+1)-йвыход дешифратора подключен к счетному входу (И+1)-го счетчика ошибокгруппы, вход разрешения записи первого регистра памяти является управляющим входом устройства,1лов

СмотретьЗаявка

4199452, 24.02.1987

В. П. Морозов, В. Н. Барулин, Я. С. Димарский и О. Е. Климова

МОРОЗОВ ВЛАДИМИР ПЕТРОВИЧ, БАРУЛИН ВАЛЕРИЙ НИКОЛАЕВИЧ, ДЫМАРСКИЙ ЯКОВ СЕМЕНОВИЧ, КЛИМОВА ОЛЬГА ЕВГЕНЬЕВНА

МПК / Метки

МПК: G06F 15/20

Метки: моделировавания, программирования, технологии

Опубликовано: 15.03.1989

Код ссылки

<a href="https://patents.su/3-1465892-ustrojjstvo-dlya-modelirovavaniya-tekhnologii-programmirovaniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделировавания технологии программирования</a>

Предыдущий патент: Устройство для анализа параметров графа

Следующий патент: Интерполятор

Случайный патент: Установка для обработки листового стекла в процессе его изготовления