Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

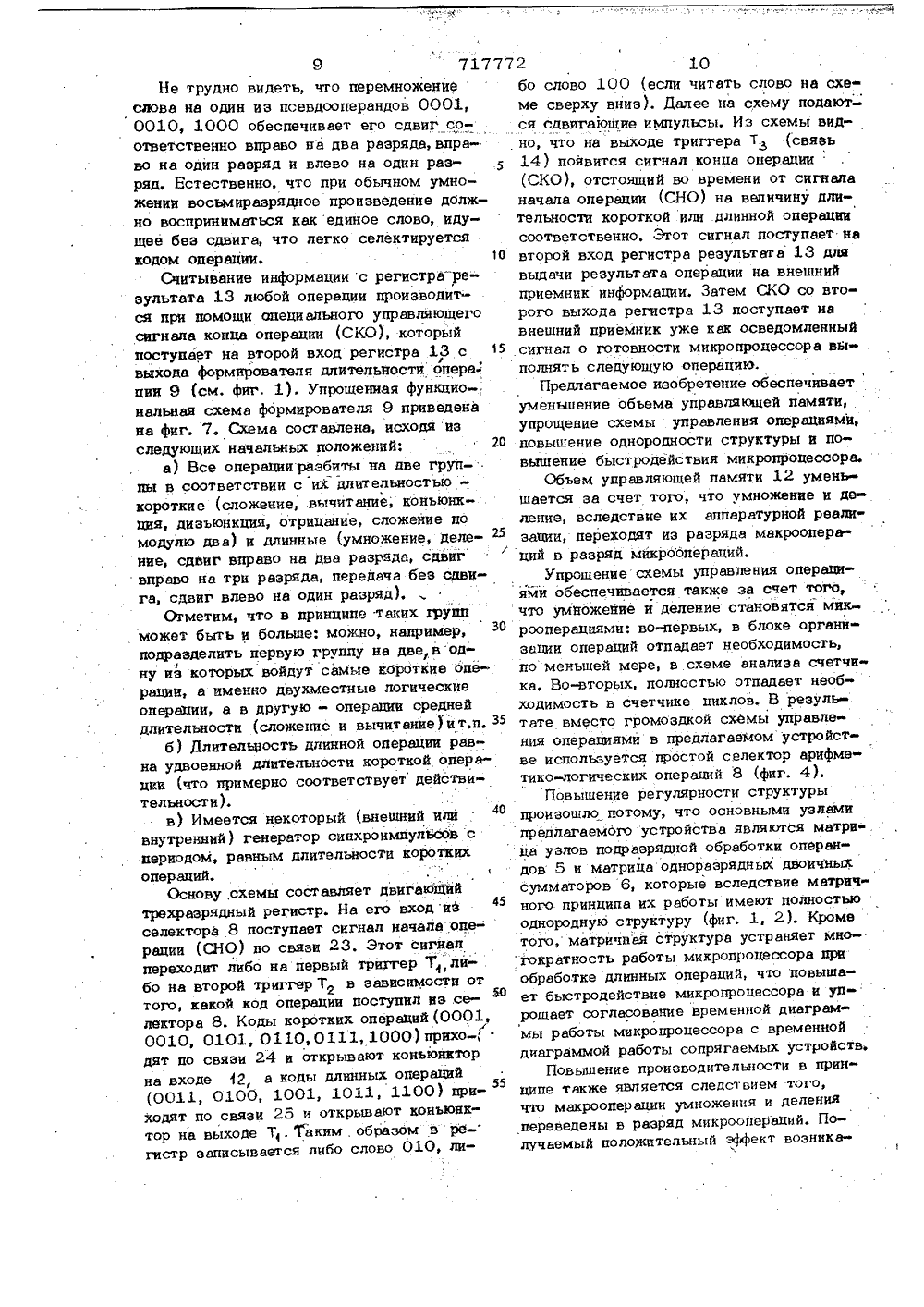

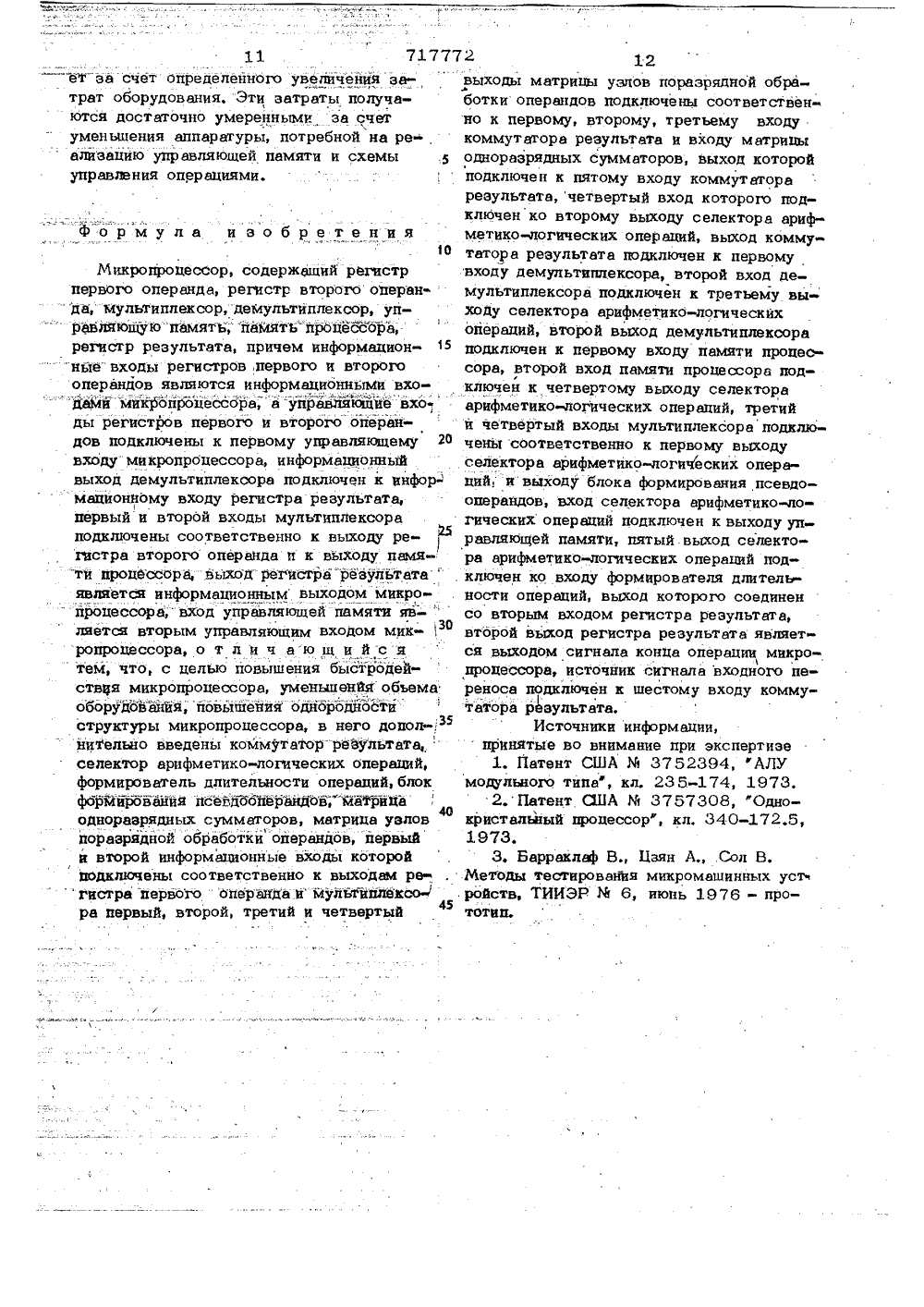

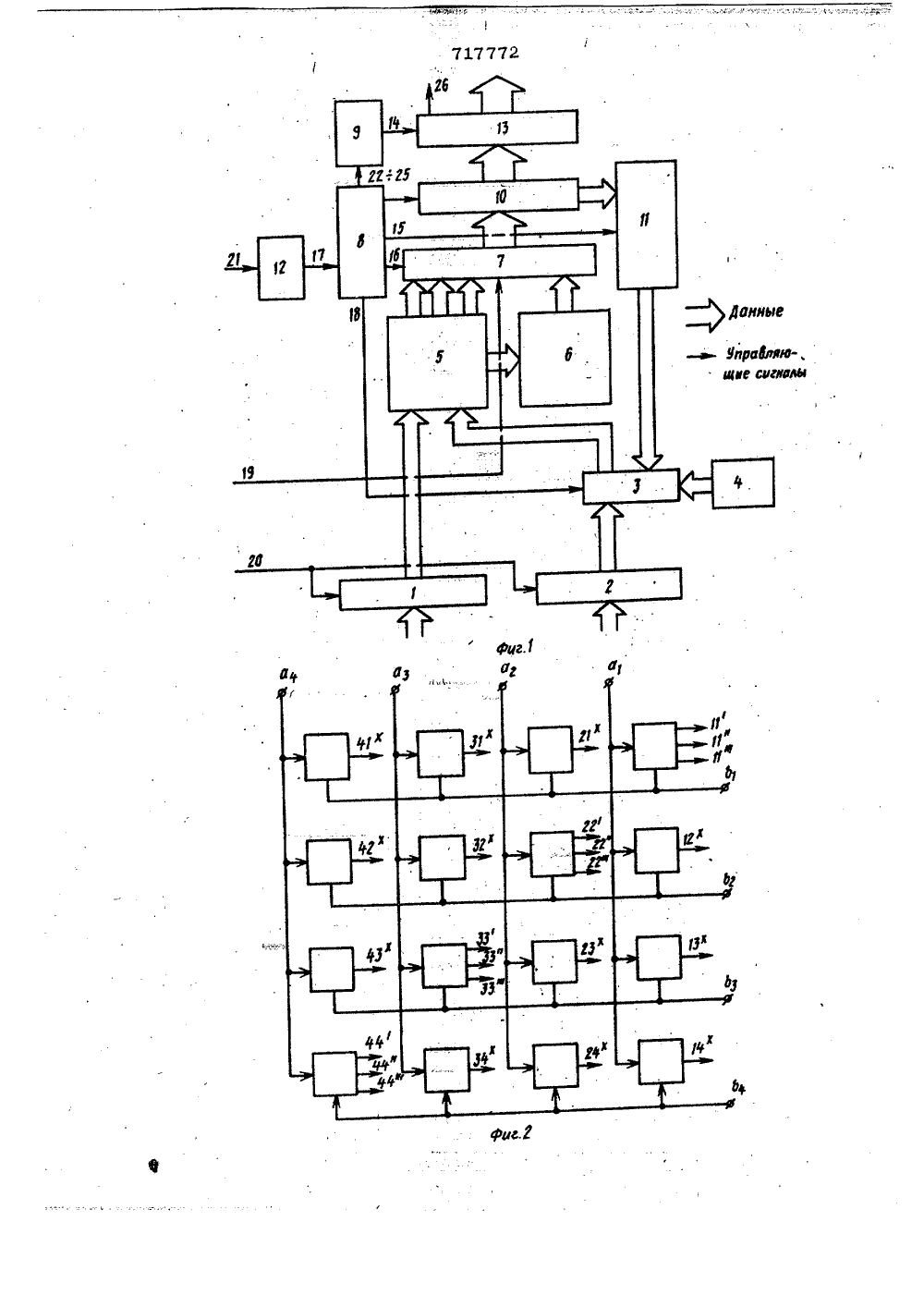

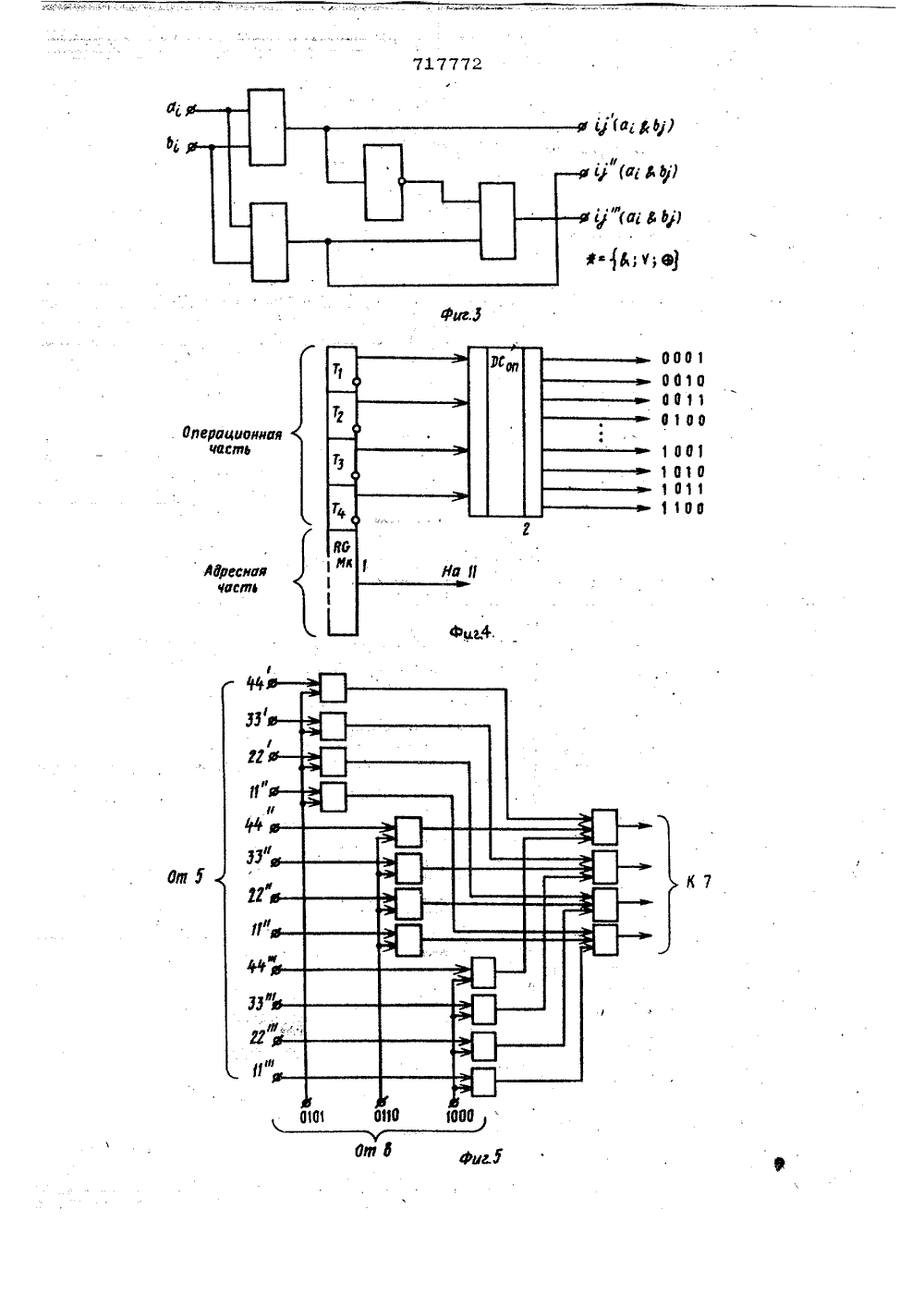

(11717772 Союз СоветсиииСоциалистическихреспублик ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(51)М. Кл, 6 06 Г 15/00 с присоединением заявки Маваударотвеинмй комитет СССР йа делам изобретений и открытийДата опубликования описания 28,02,80(71 ител МИКРОН РОЦЕСОЭР 2 Предлагаемое устройство относится к ботку операндов цри помощи аппаратурных области вычислительной техники и цифро- средств 21, Недостатками устройства яввой автоматики. Оно может использовать- лаются низкая производительность, сложся в алектронно-вычислительной машине ная схема управления операциями; в осо- (ЭВМ), вычислительных устройствах и при- бенности умножением и делением.борах цифровой автоматики для цифровой Наиболее близким техническим решениобработки данных, ем к данному предложению является микИзвестно устройство, выполненное в ропроцессор, содержащий регистр первого виде модуля и обеспечивающее алгебраи- операнда, регистр второго операнда, мульческое сложение при помощи вычитателей типлексор, демультиплексор, память прои схем параллельной выработки сигналов . цессора, управляющую память, регис р р 10 - 1ги 1 езаема а также лот ическую обработку опе- зультата, причем первый и второй входы рандов, Недостатками устройства являют- регистров первого операнре соединены со-ся низка производительность, отсутствие ответственно с источниками первого опе- средств управления, обеспечивающих ав" ранда и сигнала начала операции; первый тономность процессов обработки, а также и второй входы регистра второго операннерегулярность структуры, что затрудня да соединены соответственно с источникает использование при его реализации боль ми второго операнда и сигнала начала ших интегральных схем 13. операции; первый и второй входы мультиИзвестно также устройство, выполнен- О плексора соединены соответственно с вы,ное на одном полупроводниковом крис-ходом регистра второго операнда и с выталле, имеющее сумматор и средства уп- ходом памяти процессора;. вход управляю равления и обеспечивающее автономное ал- шей памяти соединен с источником кодов гебраическое сложение и логическую обрв- операций; первый вход регистра реэу та717772 Г. Решети Подписи 7 Тираж 751ЦНИИПИ Государственного комйо делам иаобретений и отк3035, Москва, Ж-З 5, Рауа аз 9849/6 ета аи наб., д. 4/5 л ППЙ фПатент", г. Ужгород ил ктная,дактор Э, Чубнйдквя Составитель Г, ЛамэинаТехред М. Келемеш Кор3 717772 4та соединен с первым вьаодом демульти-второй информационные входы которой подплексора, а первый выход этого "фегйстра -ключенысоответственно к вых дам реги соецйнейс прйемнйкомрезульгатв бйеа- " "ра первого операнда и мультиплексора,ции. Таким микропроцессор обеспечивает первый, второй, третий и четвертый выховыполнение алгебраического сложения и 5 ды матрицы узлов поразрядной обработкилогических операцйй йри помощи мйЪра-ойерандов"пбдключвны соответственно к Фурййх средств "в",также умйожейие"и-де-первому,втОрОМу, третьему входу коммуЛеййе ойбфЖдов" йй-"помощи программйых" татора результата и "входу Матрицы однои микропрограммных средств 31. разрядных сумматоров, выход которой подОперанды А и В поступают на регист-,О ключен кйятому входу коммутатора ре ры первого и второго, операйдов, приемзультата, четвертый вход которого подопэрвйдов пройэводится по сигналу иэ цент ключен к первому выходу селектора арифрального устройства управления. далееметико-логических операций; выход комму;1-й операнд подается на 1-й вход сумма- таторарезульФата"подключен к перв мутора, а второй операнд через мультиплек-входу демультиплексора, второй вход де-, " "сор подается на второй вход сумматора,мультиплекоора"подключен к третьему выгде йро звоФтся-короткие ойеращТйтакиеходу селектора арифметико-логиче кихквк, сложение, вычитание, конъюнкцйя, опервций, второй"выходдемультиплексораизъйЯЙция,"от Йцанйе;" сложеййе йо"мо= " подключен к первому вхоЬу памяти пр цес-"лю 2. Результат поступает в нвквпливв-Ф сора, второй вхЬдпав,ги процессора подющйй регистр и далее через "демультиплэк- ключен"к четвертому выходу селектора сор" йост пает в регистр результата. арифметико-логических операций, третийСдвигрезультата производится сдвига- и четвертый входы мультиплексора подтелем. Передача результатв на дальйей-, ключены к первому выходу селектора ариф.ш ю об аботк пройзводится с регистра , метико-"логических операций и выходу бло реэульгета"но сигналу центрального уст- ка 4 ормирования псевиоопервнд вройства управления, который поступаетственно; вход селектора врифметико-лол;- на упрввля уляющ ю память, При вьйолнениических операций подключен к выходу упй бвйизацйи опера; рввляющей памяти пятый выход селекторакоротких оиераций лок орган зций работает как дешифратор микрокоф м рокомвнд О врифметнко-логических операций подключенинных операций он рабо 4 ко входу формирователя длительности опетает в более сложном режиме, ко ежиме когда под- . раций, выходкоторого соединен со вторключается счетчик" ииклов и -регистр нако- входом регистра результата, второй выходпитель, который накапливает суливветмму части-регистра результата явлнется выходом сигных п изведений, Управление сдвигате-нала конца операции микропроцессора, втой выход селектора арифметико логичеслем, демультиплекжм, регистром накопи- рой выход се р р фтеля, памятью процесса, сумматором им"йьтиплексором осуществляется блокомкоммутатора результата.е таткамитр - -" тся - схема быстродействующего микропроцессое татками устРойства являю от"-"ра" прайагаемого в качестве иэобретеносительно низк прф 2 - структурная схема матриводительность Раф фввляющей памяти, сюж+ ния; на иг.опе вциями, особен- цы узлов пор б вбна ", Э -функциональная схемаопе вциями типаумножения дов; на фиг, - у4оСть ст кт ры,фиг. 4 - упрощенная структурная схемаейия относительно невысокая регу- устро сселектор рифмтизй) логично%1 61 щ)астояшего изобретения являетшение быст одействия мйкропро- ций; на иг, - уноммации" результатов двуместныхеньшение обьема оборудования, ла к имутлогических операций; на фиг. 6 - функцио ьнвя схема формирования суммы наео" но одности структуры.ная цель достигается тем, что ональнцесс фиг. 7- ощенная функпиональная схемацессо дополнительно содержит фиг. -упр щф - фо мирователя 3 Мтительности Опервции накоммут втор р уто ез льтата, селектор врифме- р, фо . фиг 8 - схема расположения битов перуопе вций, формирова-- стель длительности операций, блок форма- " "ного "операнда и ес в оопе видов, матрицу однораз. га.Микропроцессор содержит, регистр 1я ых с маторов, матрицу узлов порвемр дн умй и первого операнда, регистр 2,второго оце-.рядной обработки операндов, первы и72 6торого снижения однородности матрицу 5можно значительно упростить. Посколькувсе элементы матрицы нужны только придлинных операциях (умножении и делении),кргда матрица служит формирователем частичных произведений (сдвинутых кодов делителя) и каждый ее элемент выполняетроль одноразрядного умножителя, то естьконъюнктора, то можно по схеме на фиг. 3строить только те элементы матрицы 5,которые расположены на главной. диагонвли. матрицы (нв фиг. 2. эти узлы выделены жирной обводкой), а в качестве остальных элементов матрицы испольэовать обыкновенные конъюнкторы (см, фиг. 2). Вдальнейшем описании будем ориентироватмся именно на такую структуру матрицы,состоящей из полных элементов на главной диагонали и из вырожденных элементов (конъюнкторов) нв остальных позициР, Рях. Выходы полных элементов 11, 22,33 и 44 (см. фиг. 2 и 3 образуют первый групповой выход матрицы 5, которыйпоступает на первый групповой вход коммутатора результата 7 (см. фиг. 1). ВыР, с ф Гходы полных элементов 11, 22, 33 н44 образуют второй групповой выход матрицы 5, который поступает нв второй групповой вход коммутатора результата 7. ВыФ;/ Рходы полных элементов 11, 22, 33 иР44 образуют третий групповой выход матрицы 5, который поступает на третий групповой вход формирователя результата 7. На пятый вход коммутатора 7 поступает управляющий сигнал от селектора арифметико-логических операций 8. Управляющая схема селектора представлена на фиг. 4,Она,состоит из регистра микрокомвнд1 и дешифратора операций 2 (ВОиЭС, соответственно). Дешифратор 2 обеспечивает 16 выходов с двоичными номерами от 0000 до 1111, двенадцать из которых от 0001 до 1100 являются ко дами операций из ранеЕ принятого списка операций (коды 0000, 1101, 1110 и 1111 являются резервными). Пусть номера операцийсписке будут их кодами опе рвюий. Гаким образом, кодами операций конъюнкции, дизъюнкции и сложения по модулю два будут соответственно 0101, 0110, 1000, На фиг. 5 представлен узел коммутации результатов двухместных логических функций, являющийся частью коммутатора результатов 7. Нв двенадцать его входов поступают выходы с полых УПО сгруппированные по операциям; И,ФФ у 33, 22, 11, (конъюнкция): 44, 33 22 ф, 11, (диэъюнкция); 44, 33, 22 5 7177ранда, мультиплексор 3, блок формирвания псевдооперанда 4, матрицы 5 узлов поразрядной обработки операндов,матрицу 6 одноразрядных двоичных сумматоров, коммутатор результата 7, селектор 5врифметико-логических операций 8, формирователь длительности операций 9, демуль .типлексор 10, память процессора 11, управляющая память 12, регистр результата13, 14-;26 связи управляющих сигналов,1 ОПусть для определенности микропроцессор должен производить 12 операций изследующего списка (в случае необходимости список может быть либо расширен,.либо уменьшен):1) сложение алгебраическое;2) вычитание с учетом знака операндов;3) умножение;4) деление;5) конъюнкция (пораздельнвя);6) дизъюнкция (пораздельная);7) отрицание (пораздельное ) битов первого операнда;/8) сложение по модулю двв;9) сдвиг вправо на 1 разряд первогооперанда;10) сдвиг вправо на 2 разряда первого операнда;11) сдвиг влево на 1 разряд первогооперанда;12) передача первого операнда безсдвига.Первый операнд обозначим буквой А,35а второй - буквой В, Кроме того, для определенности описания схем, примем длину операндов равной четырем битам (на практике длина операндов быввет 2, 4,8, 16 битов в зависимости от степени интегрвции, что в свою очередь зввисиФот типа технологии, уровня развития прийятого типа технологии и от размеров крис- талла). Операнды по сигналу иэ централь ного устройства управления, приходящие по входу 20, поступают из регистров 1 и 2 на матрицу 5 (операнд В проходит нв матрицу 5 через мультиплексор 3), Структура матрицы 5 показана нв фиг. 2. В общем случае этв матрица состоит из оя одинаковых мементов - узел поразрядной обработки (УПО операндов, каждый из которых может обеспечить все три ло-.гические операции; конъюнкцию, диэъюнкцию и сложение по модулю двв. функциональфнвя схема одного элемента матрицы 5 приведенв на фиг. 3. В этомслучае матрица 5 получается полностью однородной, но избыточной по оборудованию, Зо счетнеко7 71777211 щ (сложение по модулю два), При пода;, разрядной обработки 5, В операции участче селектора арифметико-логичежих опе- вуют все элементы матрицы 5 - как полраций 8 одного из кодов: 0101, 0110,ные, так и вырожденные (конъюнкторы),1000 - на первый вход демультиплексо- так как матрица 5 в данном случае являра 10 (см. фиг. 1) поступит результат .5 ется формирователем частных проиэведепораэрядной койъюнкции, или диэъюнкции, ний. Частичные произведения поступаютили сложения по модулю два соответствен на четвертый выход матрицы 5 и далеено. Далее результата поступает на выход- на вход матрицы одноразрядных сумматоной регистр 13. ров 6, В результате суммирования частич-Рассмотрим порядок выполнении алгеб 0 ных произведений на выходе матрицы 6раического сложения, Начальная фаза вы- формируетси полное произведение, котороеполненйя совпадает с соответствующей фа- " поступает На четвертый вход коммутатозой выйолнеииядвухместных логическихра 7. Далее,под воздействием управляюопераций. В ней участвуют регистры 1 и щего сигнала, поступающего, на пятый вход2, мультиплексор 3, обеспечивающий пере коммутатора 7, со второго выхода селек-,дачу второго операнда,из регистра 2 на- тора 8 произведение пропускается на дематрипу 5, и полные элементы матрицы мультиплексор 10 и выходной регистр 13,5. Управляющий сигйал, поступающий по В реализации всех этих операций участ"связи 16 со второго выходаселектора 8 вует блок формирования псевдоопервндана пятый вход коммутатора 7, обеспечи 4. При выполнении отрицания блок 4 вырайI гоЮвает подачу полусуммы 44, 33, 22, батывает псевдооперанд, состоящий из од 11" и полупереносов 44, 33, 22, 11 них единиц 1111, который прн помощии ходного переноса Р на формирователь, мультиплексора 3 и селектора 8 подаетсясуммы, являющийся частью коммутатора ,:.:,на матрипу 5 вместо второго операнда.результата 7, Функциональная схема фор-.Матрица 5 настраивается при помощи семирователя суммы представлена на фиг. 6. ; лектора 8 на выполнение сложения по моПри подаче селектора кодов 0001 и 0010душо два. В результате сложения по мо(порядок выполнениявьяитаййя юлйобФыо" дулю два первого операнда А-О 40,0 а,аналогичен порядку выполнения сложевйЯ: и псевдооперанда 1111 осуществляетсяотличие заключается только,в дополни-.З 0 поразрядное отрицание первого операнда.тельной микр операции обрайенйя второгоО 4,ОЬО 2 Ооперанда, которая выполняется мультиплек . 1 1 1сором 3 под воздействием управляйщего,: а О 0 б 4сигнала с селектора 8, проходящйМо ппо Что и требовалось получитьсвязи 18, по связи 16 (см. фиг. 1 и 6) Реализация операций сдвига произво 55полусуммы, полупереиосы и входной нерв". дится при помощи узлов, обеспечивающихнос поступают на формирователь суМмьЬ: умножение, и блока формирователя псевсостоящийиз четырех полусумаФОРов и че- дооперандов , который вырабатывает слетырех дизъюнкторов. На выходе формиро- . дующйе псевдооперанды:вателя образуется четырехразрядная сум а) 0001 - для сдвига операнда А впра 40ма 63 б 5 и выходной перенос ,Ред,ко во на два разряда;торые поступают "через общий выход ом- б) 0010 - для сдвига операнда Амутатора 7 на первый вход демультиплек. вправо на один разряд;сора и далее на выходной регистр 13.в). 0100 -.дли передачи операнда Арассмотрим порядок выполнения умно 4 беэ сдвига:45жения. Деление выполняется в значйтель . г) 1000 - для,сдвига операнда Аной степени ьналогичйдпб методике, раз-. влево на один разряд,работанной и описанной в атв. св. СССР .Действительно, если условиться выдвМ 129390, кл.42, 14 . Июлл изобр.вать короткий (четырехраэрядный) резульй 12, 1960 (см. Карцев М. А."Устрой тат по средним цепям восьмиразрядногоство для умножения;С.В умножейии участ-,:выхода коммутатора - формирователя 7вуют (см. фиг. 1): регистры 1 и 2, муль 1 Ц 6, Ц 5, Ц 4, ЦЗ, то появление такого ретиплексор 3, матрицы 5, матрица 6, ком- зуйьтата, например:мутатор 7, селектор 8, Результатпереде в цешй Ц 7, Ц 6, Ц 5, Ц 4, будет восется на выход через демультиплексор 10 йриниматься как сдвиг слова влево на .55и выходной регистр 13. Умножение осу один разрящществлиется матричным методом. Оэмно - в цепях Ц 5, Ц 4, ЦЗ, Ц 2 - как сдвиг.жители поступают на матрипу узлов по- вправо на один разряд (см. фиг, 8),10бо слово 100 (если читать слово на схеме сверху вниз). Далее на схему подвкися сдвигающие импульсы. Из схемы видно, что на выходе триггера Тз (связь14) появится сигнал конца операции(СКО), отстоящий во времени от сигналаначала операции (СНО) на величину длительности короткой или .длинной операциисоответственно. Этот сигнал поступает навторой вход регистра результата 13 длявыдачи результата операции на внешнийприемник информации. Затем СКО со второго выхода регистра 13 поступает нввнешний приемник уже как осведомленныйсигнал о готовности микропроцессора выносят ь следующую операцию.Предлагаемое изобретение обеспечиваетуменьшение объема управляющей памяти,упрощение схемы управления операциями,повышение однородности структуры и повышение быстродействия микропроцессора.Объем управляющей памяти 12 уменьшается за счет того, что умножение и деление, вследствие их вппвратурной реализации, переходят из разряда мвкроопервций в разряд микроопераций.Упрощение схемы управления операциями обеспечивается также зв счет того,что умножение и деление становятся микроопервциями: во-первых, в блоке организации операций отпадает необходимость,поменьшей мере, в схеме анализа счетчика, Во-вторых, полностью отпадает необходимость в счетчике циклов. В результате вместо громоздкой схемы управления операциями в предлагаемом устройстве используется простой селектор врифметико-логических операций 8 (фиг. 4).Повышение регулярности структурыпроизошло потому, что основными узлами предлагаемого устройства являются мвтрицв узлов подразрядной обработки операндов 5 и мвтрица одноразрядных двоичныхсумматоров 6, которые вследствие мвтрич. ного принципа их работы имеют полностью однородную структуру (фиг. 1, 2). Кроме того, матричная структурв устраняет мно гокрвтность работы микропроцессора при обработке длинных опервций, что повышает быстродействие микропроцессора и упрощает согласование временной диаграммы работы микропроцессора с временной диаграммой работы сопрягвемых устройств.Повышение производительности в принципе.также является следствием того, что макроопервции умножения и деления переведены в разряд микроопервций. Получаемый положительный зффект возникв 40 9 7177Не трудно видеть, что перемножениеслова на один из псевдооперандов 0001,0010, 1000 обеспечивает его сдвиг соответственно вправо нв два разряда, вправо на один разряд и влево на один разряд, Естественно, что при обычном умножении восьмиразрядное произведение должно восприниматься как единое слово, идущее без сдвига, что легко селектируетсякодом операции.Считывание информации с регистра результата 13 любой операции производится при помощи специального управляющегосигнала конца операции (СКО), которыйпоступает на второй вход регистра 13 свыхода формирователя длительности опера-ции 9 (см. фиг, 1). Упрощенная функциональная схема формирователя 9 приведенана фиг. 7, Схема составлена, исходя изследующих начальных положений; 20а) Все операции разбиты на две группы в соответствии с их длительностьюкороткие (сложениевычитвние, конъюнкция, дизъюнкция, отрицание, сложение помодулю двв) и длинные (умножение, деление, сдвиг вправо на двв разряда, сдвигвправо нв три разряда, передача без сдвига, сдвиг влево на один разряд),Отметим, что в принципе таких группможет быть и больше: можно, например,подразделить первую группу на две,в одну иэ которых войдут самые короткие операции, а именно двухместные логическиеоперации, а в другую - операции среднейдлительности (сложение и вычитание) ит.п. З 5б) Длительность длинной операции равна удвоенной длительности короткой операции (что примерно соответствует действительности).в) Имеется некоторый (внешний нливнутренний) генератор синхроимпулЬсов с-периодом, равным длительности короткихопераций,Основу схемы составляет двигающийтрехраэрядный регистр. На его вход из45селектора 8 поступает сигнал начала"опе-рации (СНО) по связи 23. Этот сигналпереходит либо на первый триггер Т 4,либо нв второй триггер Т в зависимости отЯтого, какой код опервцйи поступил из .селектора 8, Коды коротких операций (0001,0010, 0101, 0110,0111, 1000) прихо-, .дят по связи 24 и открывают конъюнкторнв входе 12, в коды длинных операций(0011, 0100, 1001, 1011, 1100) приходят по связи 25 и открывают конъюнктор на выходе Т. Таким, образом в ре-гистр записывается либо слово 010, лиизобретения формула 10 Микропроцессор, содержвщий регистр первого операнда, регистр второго операн да, мультиплексор, демультиплексор, упрюляющупамять,- пайать" процессора, регистр результата, причем информащион "ныевходы регистров первого и второго операндов являются информационными вхо " "джей "микропроцессора, а управляющие вхо-ды регистров первого и второю операндов подключены к первому управляющему 20входу микропроцессора, информационныйвыход демультиплексорв подключен к Информвцйонному входу регистра результата,первый и второй входы мультиплексораподключены соответственно к выходу регистра второго операнда и к выходу памя- ти процессора, вьаод регистра "результатаявляется информационным выходом микро" процессора вход управляющей памяти является вторым управляющим входом микропроцессора, о т л и ч в ю щ и й с ятем, что, с целью повышения быстродействия микропроцессора, уменьшенйа объемаоборудоввйия," "йовышения одяородйостиструктуры микропроцессора, в него допол-,знительно введены коммутатор "результата, "селектор арифметико-логических операций,формирователь длительности операций, блокф 6 рмйроввния псегдбб 1 йрйщов,Яатрйцаодноразрядных сумматоров, матрица узловпоразрядной обработки операндов, первыйи второй информационные входы которойподключены соответственно к выходам регистра -первого операнда имулвгиплексо-рв первый, второй, третий и четвертый45 11 71777 еТ эа счет бпределейного увеличейия затрат оборудования, Эти затраты получаются достаточно умеренными за счет уменьшения аппаратуры, потребной на реалйзвцию управляющей памяти и схемы управления операциями. 12выходы матрицы узлов поразрядной обработки операндов подключены соответственно к первому, второму, третьему входукоммутатора результата и входу матрицыодноразрядных сумматоров, выход которойподключен к пятому входу коммутаторарезультата,четвертый вход которого подключен ко второму выходу селектора арифметико-логических операций, выход коммутатора результата подключен к первомувходу демультиплексора, второй вход демультиплексора подключен к третьему выходу селектора арифметико-логическихопераций, второй выход демультиплексораподключен к первому входу памяти процессора, второй вход памяти процессора подключей к четвертому выходу селектораарифметико логических операций, третийи четвертый входы мультиплексора подключены соответственно к первому выходуселектора арифметико-логических операций ивыходу блока формирования псевдооперандов, вход селектора арифметико-логических операций подключен к выходу управляющей памяти, пятый. выход селектора арифметико-логических операций подключен ко входу формирователя длительности операций, выход которого соединенсо вторым входом регистра результата,второй выход регистра результата является выходом сигнала конца операции микропроцессора, источник сигнала входного переноса подключен к шестому входу коммутатора результата.Источники информации,принятые во внимание при экспертизе1, Патент США3752394 фАЛУмодульного типа, кл. 235-174, 1973.2.Патент США3757308, "Однокристальный процессор", кл. 340-172.5,1973.3. Барраклвф В., Бзян А.Сол В,Методы тестирования микромвшинных устройств, ТИИЭР6, июнь 1976 - прототип.

СмотретьЗаявка

2490420, 01.06.1977

ПРЕДПРИЯТИЕ ПЯ М-5339

АСЦАТУРОВ РУБЕН МИХАЙЛОВИЧ, ЛЫСИКОВ БОРИС ГРИГОРЬЕВИЧ, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 25.02.1980

Код ссылки

<a href="https://patents.su/10-717772-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для адресации буферной памяти

Следующий патент: Микропрограммный процессор

Случайный патент: Устройство для управления инвертором