Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

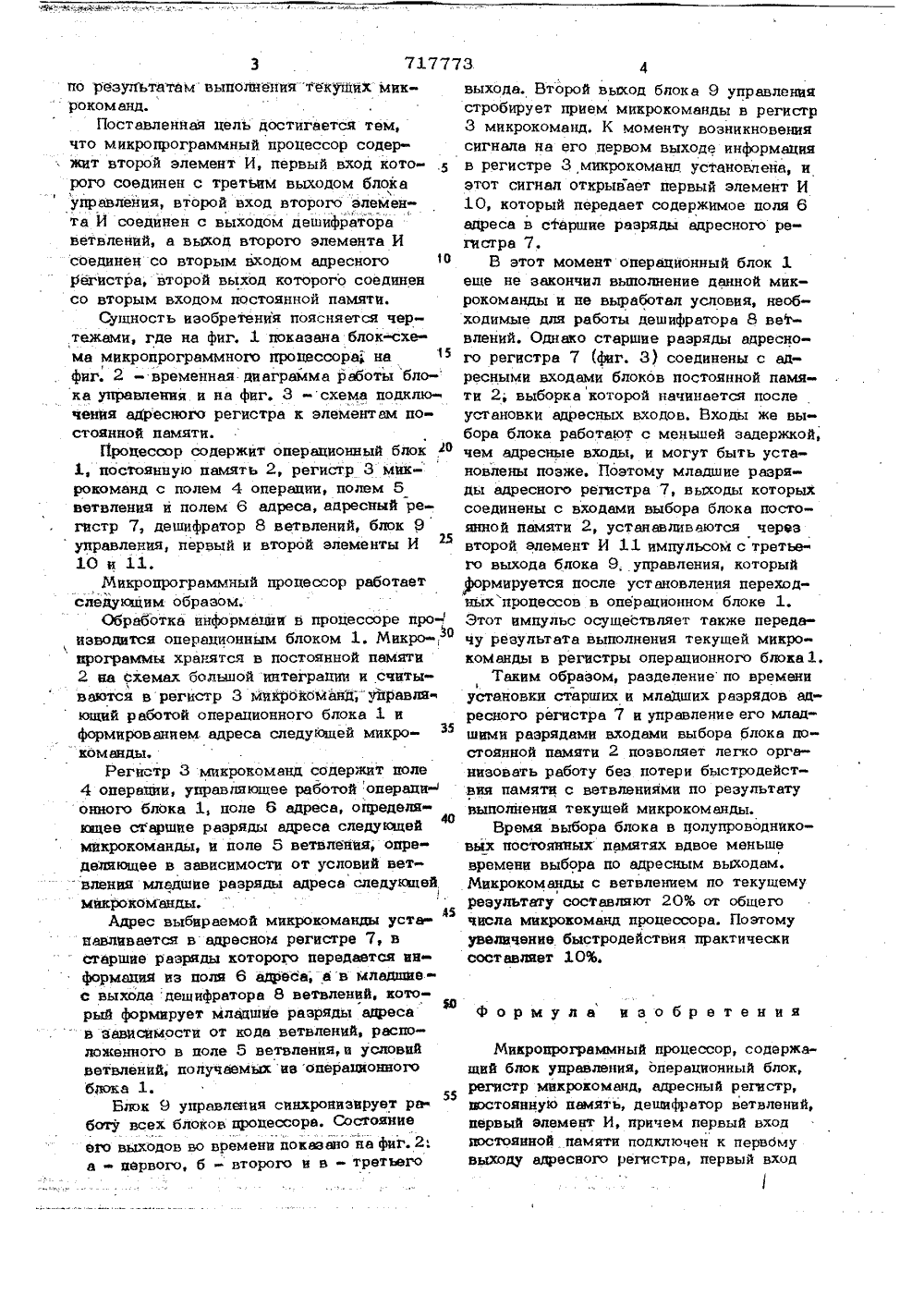

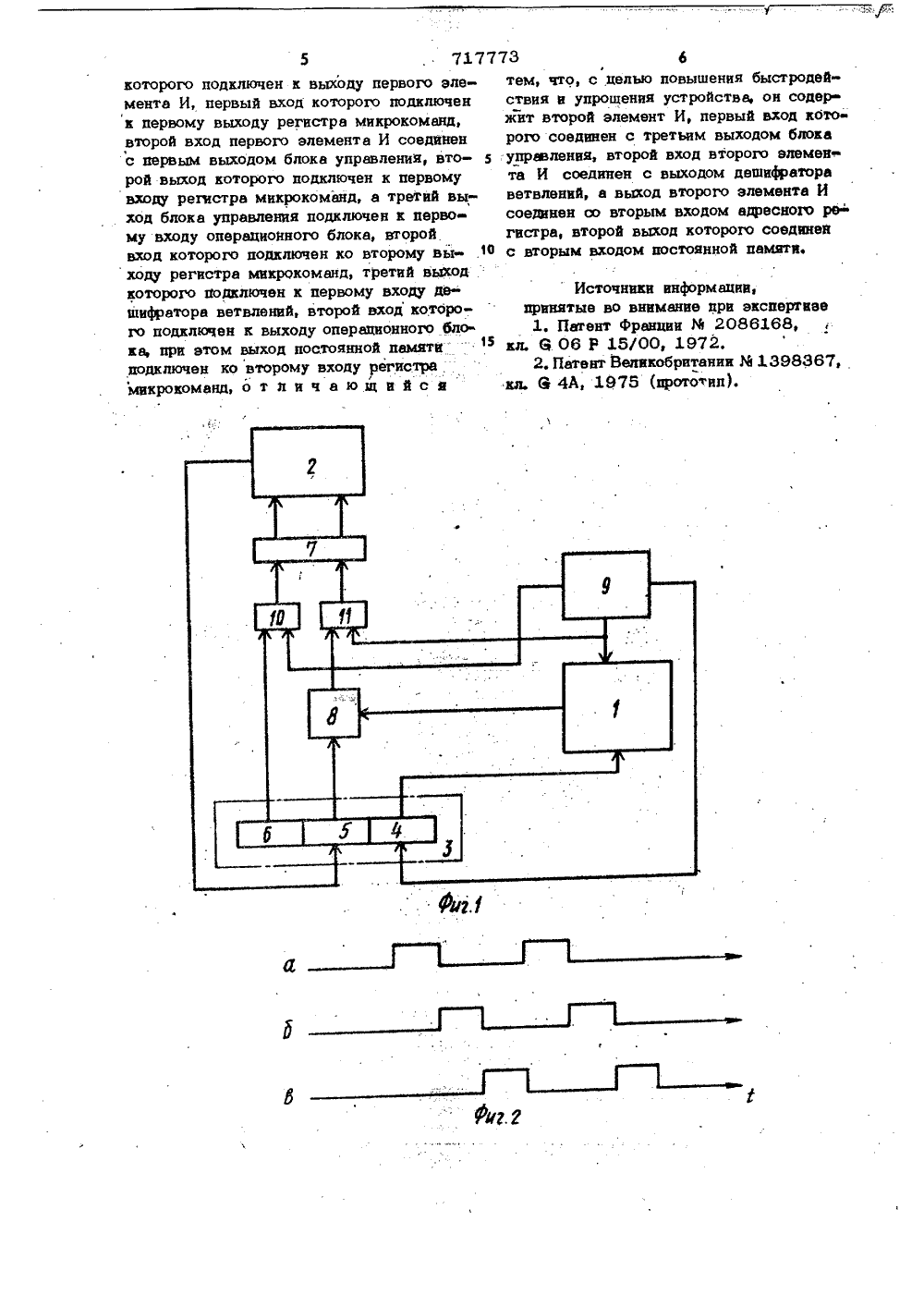

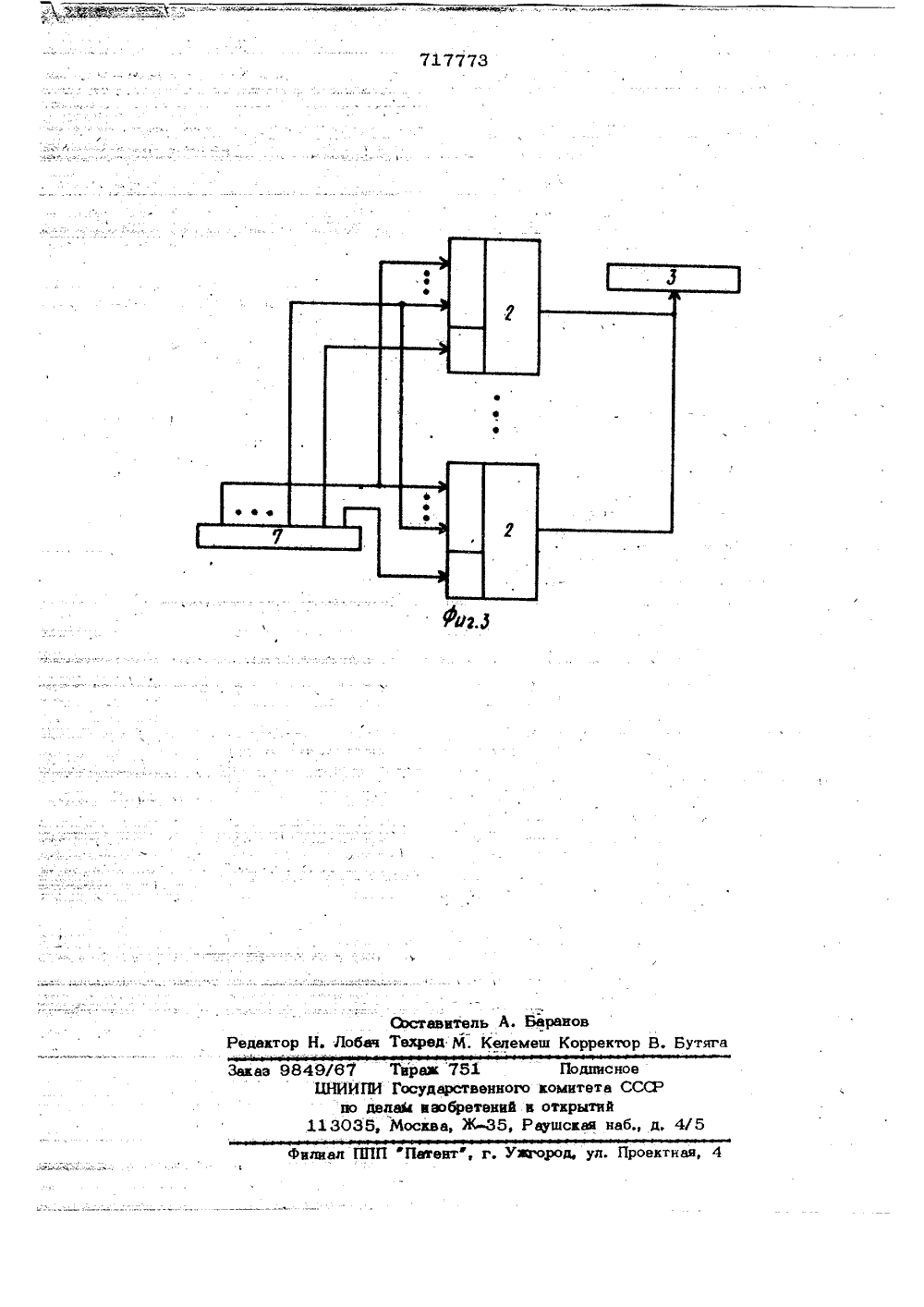

ОП ИСАНИЕИ ЗОВУЕТЕ Н ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоциалистическихРеспублик п 717773 61) Дополнительное к авт, свид-вугФ 22) Заявлено 01,12. 77 (21) 2550316/18-24с присоединением заявки РЙ(51)М. Кд. 6 06 Р 15/00 умрственМ кемнтет ВС.ФР.Дата опубликован авам зебретен н втервпнй(72) Авторы изобретени В. М. Долкарт, Р. Р. Пурэ и В. Н. Степанов Заявитель ИКРОПРОГРАММНЫЙ ПРОЦЕССОР вания,Целью ся упро стродей Изобретение относится к вычислительной технике и, в частности, к проектйро-" ванию микропрограммных процессоров;Известен микропрограммный процессор,содержмций операционный блок, постоянную память на схемах большой интегра 5 ции, регистр микрокоманд, адресный регистр и блок управления и синхронизацииШ.Однако такое устройство имеет низкое1 О быстродействие.Наиболее близким по технической сущности к предложенному является мйкропрограммный процессор, содержащий блок управления, операционный блок, регистр микрокоманд, адресный регистр, постоянную память, дешифратор ветвлений, пер- вый элемент И, причем первый вход пос- тоянной памяти подключен к первому выходу адресного регистра, первый вход которого подключен к выходу первого элемента И, первый вход которого подключен к первому выходу регистра микрокоманд второй вход первого элемента И соедин 2с первым выходом блока управления, второй выход которого подключен к первому входу регистра макрокоманд, а третий выход блока управления подключен к первому входу операционного блока, второй вход которого подключен ко второму выходу регистра микрокоманд, третий выход которого подключен к первому входу дещифратора ветвлений, второй вход которого подключен к выходу операционного блока,при этом выход постоянной памятй подключен ко второму входу регистра микрокомандЮ.Недостатком известною устройства яв ляется необходимость параллельного чтения нескольких микрокоманд из постоянной памяти для быстрою выполнения условных переходов (ветвлений) по результату выполнения текущей микрокоманды, Это существенно увеличивает затраты оборудонастоящего изобретения являет- ение устройства и ловышение бывия при выполнении ветвлений717773 4выхода. Второй выход блока 9 управлениястробирует прием микрокоманды в регистр3 микрокоманд. К моменту возникновениясигнала на его первом выходе информацияо- .5 в регистре 3 микрокоманд установлена, иэтот сигнал открывает первый элемент И10, который передает содержимое поля 6адреса в старшие разряды адресного регистра 7.В этот момент операционный блок 1ен еще не закончил выполнение данной микрокоманды и не выработал условияу необр- ходимые для работы дешифратора 8 веге- влений. Однако старшие разряды адресного регистра 7 (фиг. 3) соединены с адло- ресными входами блоков постоянной памялю ти 2, выборка которой начинается послепо- установки адресных входов. Входы же выбора блока работают с меньшей задержкой,окчем адресные входы, и могут быть уста .лоновлены позже. Поэтому младшие разряды адресного регистра 7, выходы которыХРе- соединены с входами выбора блока постоР янной памяти 2, устанавливаются черезИ второй элемент И 11 импульсом с третьего выхода блока 9, управления, которыйет формируется после установления переходнйхпроцессов в операционном блоке 1,про- Этот импульс осуществляет также передаро-, О чу результата выполнения текущей микрон команды в регистры операционного блока 1.ы- Таким образом, разделение по времени1,лящ установки старших и младших разрядов адресного регистра 7 и управление его младшими разрядами входами выборе блока постоянной памяти 2 позволяет легко оргале низовать работу без потери быстродейсти- вия памяти с ветвлениями по результатуля- выполнения текущей микрокоманды.ей4 ОВремя выбора блока в цолупроводникое вых постоянных памятях вдвое меньшет времени выбора по адресным выходам.ей, Микрокоманды с ветвлением по текущемурезультату составляют 20% от общегота- числа микрокоманд процессора. ПоэтомуИувеличение быстродействия практическиин составляет 10%. по результатам выполнения т"екающих микроком анд.Поставленная цель достигается тем,что микропрограммный процессор содержит второй элемент И, первый вход котрого соединен с третьим выходом блокауправления, второй вход второго элемента И соединен с выходом дешифратораветвлений, а выход второго элемента Исоединен со вторым входом адресногорегистра, второй выход которого соединсо вторым входом постоянной памяти,Сущность изобретения поясняется четежами, где на фиг, 1 показана блок-схма микропрограммного процессора; нафиг. 2 - временная диаграмма работы бка управления и на фиг. 3 -схема подкчения пресного регистра к элементамстоянной памяти.Процессор содержит операционный бл1, постоянную память 2, регистр 3 микрокоманд с полем 4 операции, полем 5ветвлении и полем 6 адреса, адресныйгистр 7, дешифратор 8 ветвлений, блокуправления, первый и второй элементы10 и 11.Микропрограммный процессор работаследующим образом.Обработка информапйи в процессоре, изводится операционным блоком 1. Микпрограммы хранятся в постоянной памят2 на схемах большой интеграции и считвеются в регистр 3 микрокбмйнд,уйравющий работой операционного блока 1 иформированием адреса следующей микрокоманды,Регистр 3 микрокоманд содержит но4 операции, управляющее работой операцонного блока 1, поле 6 адреса, опредеющее старшие разряды адреса следующмйкрокоманды, и поле 5 ветвления, оардепяющее в зависимости от условий ве"вления младшие разряды адреса следукщмикрокоманды.Адрес выбираемой микрокоманды уснавливается в адресном регистре 7, встаршие разряды которого передаетсяформация из поля 6 адреса, ав младщиес выхода дешифратора 8 ветвлений, котоФОрый формирует младшие разряды адресав зависимости от кода ветвлений, расположенного в поле 5 ветвления, и условийветвлений, получаемых из операционногоблока 1,55Блок 9 управления синхронизирует работу всех блоков процессора. Состояниеего выходов во времени показано на фиг. 2:а - первого, б - второго и в - третьего Формула изобретения Микропрограммный процессор, содержащий блок управления, операционный блок, регистр микрокоманд, адресный регистр, постоянную память, дещифратор ветвлений, первый элемент И, причем первый вход постоянной памяти подключен к первому выходу адресного регистра, первый вход5 717773 6Фкоторого подключен к выходу первого эле- тем, что, с целью повышения быстродеймента И, первый вход которого подключен ствия и упрошения устройства, он содер к первому выходу регистра микрокоманд, жит второй элемент И, первый вход кото- второй вход первого элемента И соединен рого соединен с третьим выходом блока с первым выходом блока управления, вто- з -упрюления, второй вход второго элемен. рой выход которого подключен к первому та И соединен с выходом дешифратора входу регистра микрокоманд, а третий вы- ветвлений, а выход второго элемента И ход блока управления подключен к перво соединен со вторым входом адресного ре му входу операционного блока, второй гистра, второй выход которого соединеи вход которого подключен ко второму вы .10 с вторым входом постоянной памяти, ходу регистра микрокоманд, третий выходкоторого подключен к первому входу де - Источники информации,шифратора ветвлений, второй вход которо-принятые во внимание при экспертее ю подключен к выходу операционного бло. Патент Франции М 2086168, ка, при этом выход постоянной памятикл, 6 06 Р 16/00, 1972.подключен ко второму входу регистра 2. Патент Великобритании М 1398367, микрокоманд, о т л и ч а ю щ и й с я кл. 9 4 А, 1978 (прототип).филиал ППП Патент, г, Уагород, ул. Проектная, 4 аэ 9849/67 Тиран 781 Подпи ИНИЙПИ Государственного омите о делМ иэобретений в откры 113038, Москва, Ж 38, Раушсквн

СмотретьЗаявка

2550316, 01.12.1977

ПРЕДПРИЯТИЕ ПЯ Г-4128

ДОЛКАРТ ВЛАДИМИР МИХАЙЛОВИЧ, ПУРЭ РУДОЛЬФ РОБЕРТОВИЧ, СТЕПАНОВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 25.02.1980

Код ссылки

<a href="https://patents.su/4-717773-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Микропроцессор

Следующий патент: Устройство для синхронизации вычислительной системы

Случайный патент: Способ погрузки сыпучих материалов в крытые железнодорожные вагоны с боковыми люками