Устройство для умножения чисел с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1280624

Авторы: Евстигнеев, Кошарновский, Маркин

Текст

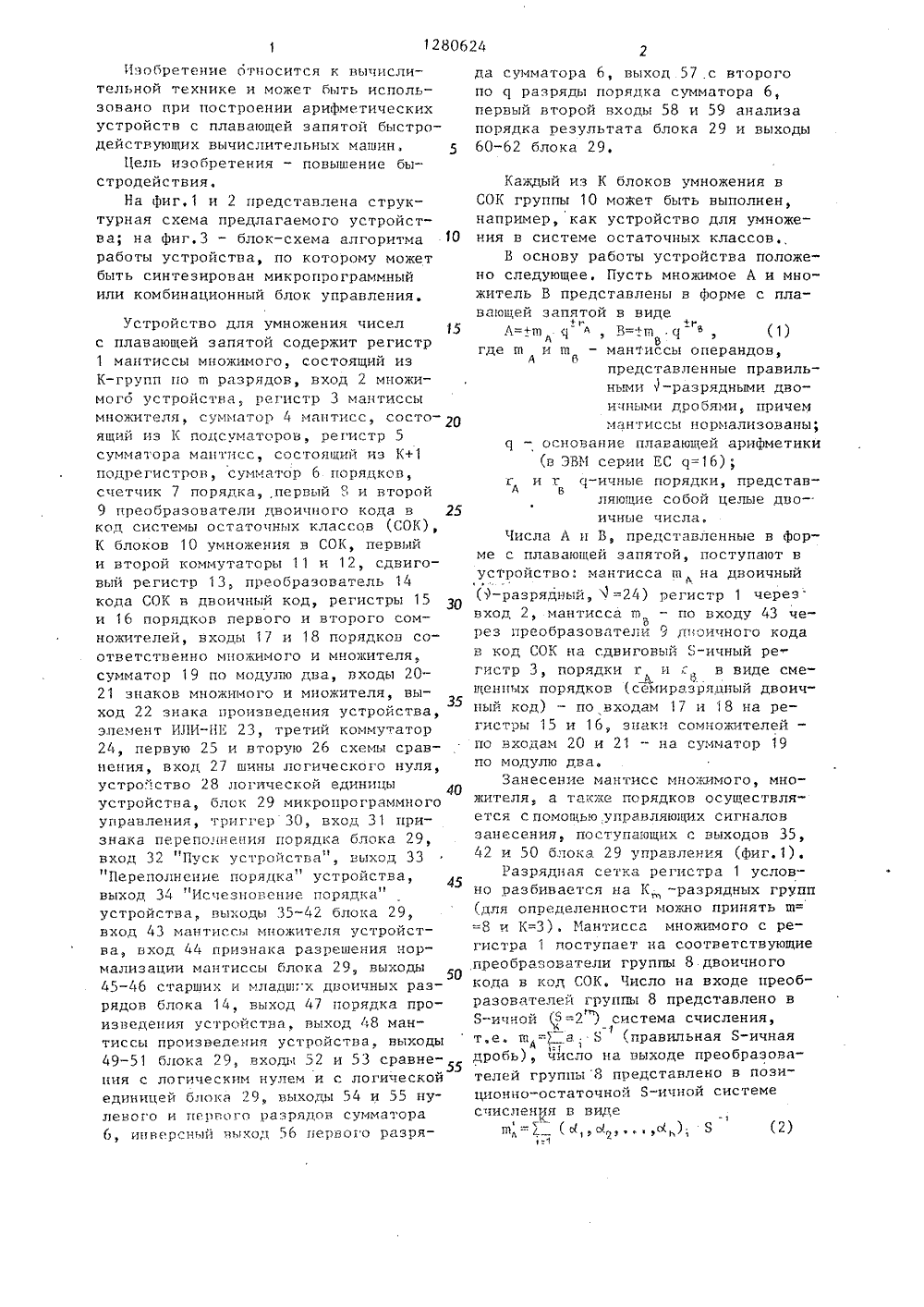

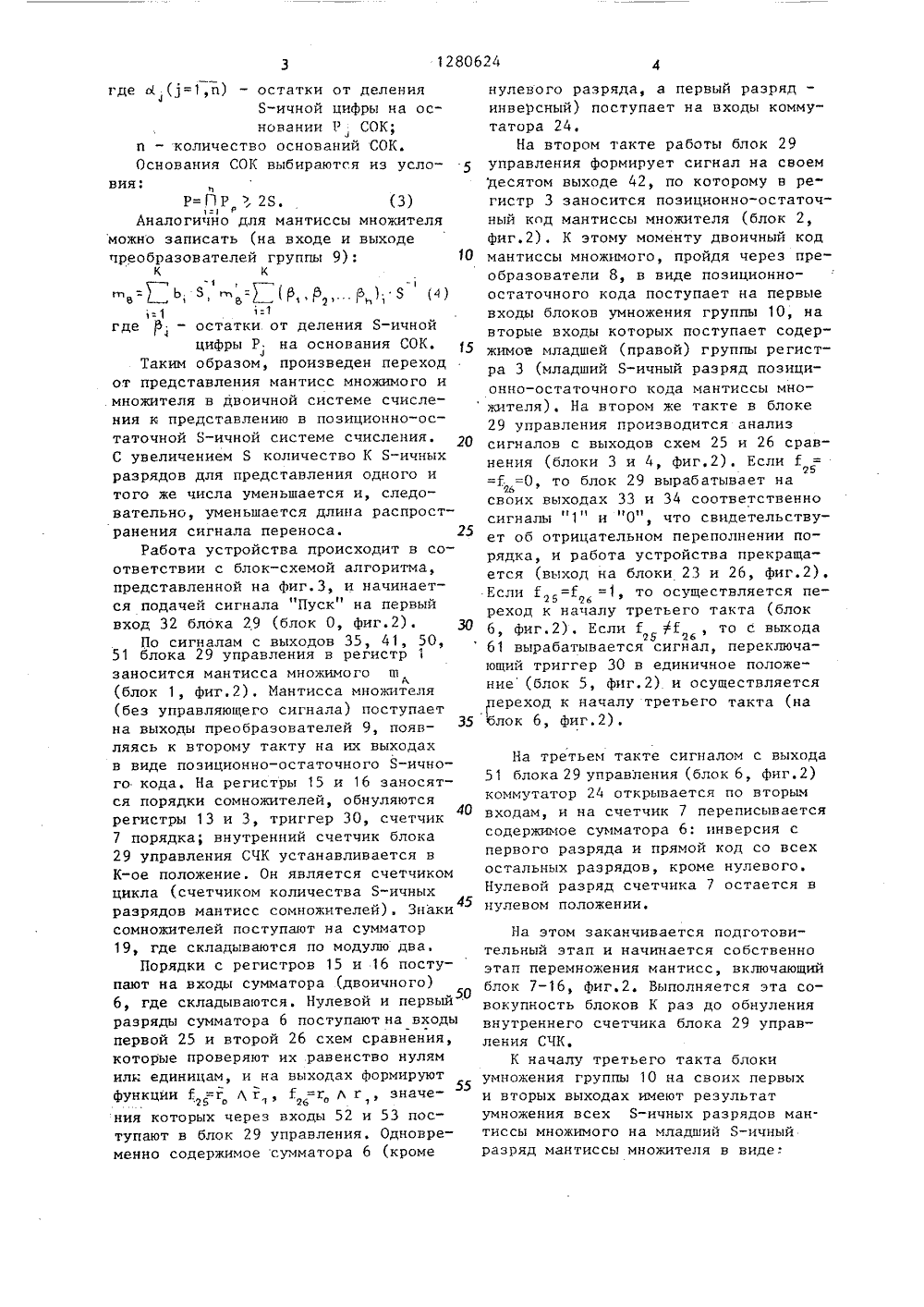

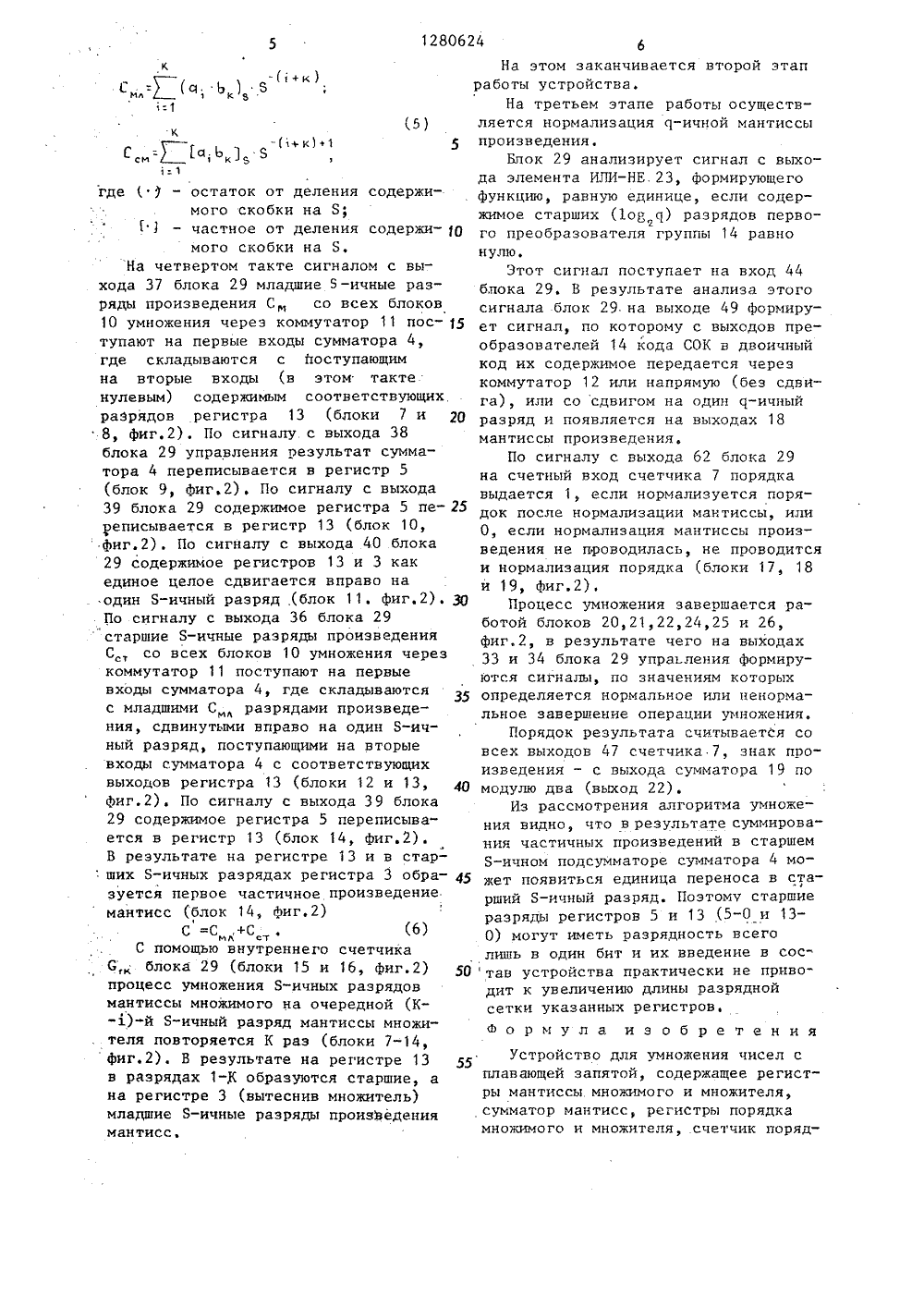

СОЮЗ СОБЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН д 511 4 С 06 Е 7/72 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНЯТИЙОПИСАНИЕ ИЗОБРЕТЕН(56) Каган Б.М. Электронные вычислительные машины и системы. М.: Энергия, 1979, с. 229, рис. 6-17.(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ 1 ИСЕЛС ПЛАВИОЩЕИ ЗАПЯТОЙ(57) Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих арифметических устройств современных ЭВМ, Цель изобретения - повышение быстродействия. Заявляемое устроиство содержит регистры мантиссмножимого и множителя, состоящее изК групп по ш разрядов; первую и втор ло группы из К преобразователей двоичного кода в код СОК, группу из Кблоков умножения, три коммутатора,сумматор мантисс, состоящий из подсумматоров; регистр сумматора мантисс, состоящий иэ К+1 групп; сдвиговый регистр, состоящий иэ К+1 подрегистров; группу иэ 2 К преобразователей кода СОК в двоичный код; элементИЛИ-НЕ, блок микропрограммного управ"пения, регистры порядков мноймогои множителя, сумматор по модулю два,сумматор порядков, две схемы сравне- ания, триггер и счетчик порядка. 2 ил.Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств с плавающей запятой быстродействующих вычислительных машин, 5Цель изобретения - повышение быстродействия,На Фиг,1 и 2 представлена структурная схема предлагаемого устройства; на Фиг.3 - блок-схема алгоритма 10 работы устройства, по которому может быть синтезирован микропрограммный или комбинационный блок управления. да сумматора 6, выход 57 с второгопо Ч разряды порядка сумматора 6,первый второй входы 58 и 59 анализапорядка результата блока 29 и выходы60-62 блока 29. Каждый из К блоков умножения вСОК группы 10 может быть выполнен,например, как устройство для умножения в системе остаточных классов.,В основу работы устройства положено следующее. Пусть множимое А и множитель В представлены в Форме с плавающей запятой в виде+А+в Ч д, В+ш Ч (1)Вгде ш и ш - мантиссь операндовА Вьпредставленные правильными -разрядными двоичными дробями, причеммантиссы нормализованы;основание плавающей арифметики(в ЗВМ серии ЕС 9=16);г и т Ч-ичные порядки представАляющие собой целые двоичные числа,Числа А и В, представленные в Форме с плаваюпей запятой, поступают вустройство: мантисса шна двоичный-разрядый, ) =-24) регистр 1 черезвход 2, мантисса ш - по входу 43 через преобразователй 9 двоичного кодав код СОК на сдвиговьй Б-ичный регистр 3, порядки г и ;., в виде смеиенцых порядков (семиразрядный двоичный код) - по входам 17 и 18 на регистры 15 и 16, знаки сомножителейпо входам 20 и 21 - на сумматор 19по модулю два.Занесение мантисс множимого, множителя, а также порядков осуществляется спомощью управляющих сигналовзанесения, поступающих с выходов 35,42 и 50 блока 29 управления (фиг.1).Разрядная сетка регистра 1 условно разбивается на К -разрядных групп(для определенности можно принять ш==8 и К=3). Мантисса мцожичого с регистра 1 поступает на соответствующиепреобразователи группы 8 двоичногокода в код СОК, Число на входе преобразователей группы 8 представлено вБ-инной Р =-2 ) система счисления,т,е. ш =Е. а Б ,правильная Б-ичная4дробь), число на выходе преобразователей группы Я представлено в позиционно-остаточной Б-ичной системесчисления в видеЬ. - (дюсь) Б (2)1280624 На этом заканчивается второй этапработы устройства.На третьем этапе работы осуществляется нормализация с 1-ичной мантиссыпроизведения.Блок 29 анализирует сигнал с выхо,ца элемента ИЛИ-НЕ. 23, формирующегофункцию, равную единице, если содержимое старших (1 о 8 с 1) разрядов первого преобразователя группы 14 равнонулю.Зтот сигнал поступает на вход 44блока 29. В результате анализа этогосигнала блок 29 на выходе 49 формирует сигнал, по которому с выходов преобразователей 14 кода СОК в двоичныйкод их содержимое передается черезкоммутатор 12 или напрямую (без сдвига), или со сдвигом на один с(-ичныйразряд и появляется на выходах 18мантиссы произведения.По сигналу с выхода 62 блока 29на счетный вход счетчика 7 порядкавыдается 1, если нормализуется порядок после нормализации мантиссы, илиО, если нормализация мантиссы произведения не проводилась, не проводитсяи нормализация порядка (блоки 17, 18и 19, фиг.2),Процесс умножения завершается работой блоков 20,21,22,24,25 и 26,фиг.2, в результате чего на выходах33 и 34 блока 29 упраьления формируются сигналы, по значениям которыхопределяется нормальное или ненормальное завершение операции умножения,Порядок результата считывается совсех выходов 47 счетчика 7, знак произведения - с выхода сумматора 19 помодулю два (выход 22).Из рассмотрения алгоритма умножения видно, что в результате суммирования частичных произведений в старшемБ-ичном подсумматоре сумматора 4 может появиться единица переноса в старший Б-ичный разряд, Поэтому старшиеразряды регистров 5 и 13 (5-0 и 13 О) могут иметь разрядность всеголишь в один бит и их введение в сос тав устройства практически не приводит к увеличению длины разряднойсетки указанных регистров,(5) где (- остаток от деления содержимого скобки на Б;частное от деления содержимого скобки на Б,На четвертом такте сигналом с выхода 37 блока 29 младшие Б -ичные разряды произведения См со всех блоков10 умножения через коммутатор 11 поступают на первые входы сумматора 4,где складываются с поступающимна вторые входы (в этом такте.нулевым) содержимым соответствующих,разрядов регистра 13 (блоки 7 и 208, фиг.2). По сигналу с выхода 38блоха 29 управления результат сумматора 4 переписывается в регистр 5(блок 9, фиг,2). По сигналу с выхода39 блока 29 содержимое регистра 5 переписывается в регистр 13 (блок 10,фиг.2), По сигналу с выхода 40 блока29 содержимое регистров 13 и 3 какединое целое сдвигается вправо наодин Б-ичный разряд (блок 11. фиг.2). 3 ОПо сигналу с выхода 36 блока 29старшие Б-ичные разряды произведенияС со всех блоков 10 умножения черезкоммутатор 11 поступают на первыевходы сумматора 4, где складываютсяс младшими С разрядами произведения, сдвинутыми вправо на один Б-ичный разряд, поступающими на вторыевходы сумматора 4 с соответствующихвыходов регистра 13 (блоки 12 и 13, 40фиг.2). По сигналу с выхода 39 блока29 содержимое регистра 5 переписывается в регистр 13 (блок 14, фиг.2)В результате на регистре 13 и в стар:ших Б-ичных разрядах регистра 3 образуется первое частичное произведениемантисс (блок 14, фиг.2)С =С,+С (6)С помощью внутреннего счетчикаС, блока 29 (блоки 15 и 16, фиг.2) 50процесс умножения Б-ичных разрядовмантиссы множимого на очередной (К-)-й Б-ичный разряд мантиссы множителя повторяется К раз (блоки 7-14,фиг,2). В результате на регистре 13 55в разрядах 1"К образуются старшие, ана регистре 3 (вытеснив множитель)младшие Б-ичные разряды произведениямантисс. КС,с(О,Ь), В Формула изобретения Устройство для умножения чисел с плавающей запятой, содержащее регистры мантиссы.множимого и множителя, сумматор мантисс, регистры порядка множимого и множителя, .счетчик порядков, сумматор по модулю два, блок микропрограммного управления.,регистр сумматора мантисс, причем вход регистра мантиссы множимого является входом множимого устройства, первый и второй входы сумматора по модулю два являются входами знаков множимого и множителя устройства, выход сумматора по модулю два является выходом знака произведения устройства, выход сумматора мантисс соединен с информационным входом регистра сумматора,; мантисс, о т л и ч а ю щ е е с я тем, что, с целью повышения быстро;., действия, в него введены два преобра зователя двоичного кода в код системы остаточных классов, преобразователь кода системы остаточных классов в двоичный код, К блоков умножения в системе остаточных классов, где К - 20 разрядность сомножителей, три коммутатора, регистр сдвига, .элемент ИЛИНЕ , сумматор порядков, две схемы сравнения и триггер, причем первый и второй выходы блока микропрограммного 5 управления являются выходами соответственно переполнения порядка и исчезновения порядка устройства, третий выход блока микропрограммного управления соединен с входом разрешения 30 записи регистра мантиссы множимого, выход которого соединен с входом пер-. вого преобразователя двоичного кода в код системы остаточных классов, -й выход которого (где ь=1,К) со- З 5 единен с первым входом -го блока умножения в системе остаточных классов, второй входкоторого соединен с выходом К-го разряда регистра мантиссы множителя, информационный вход 1-го разряда которого соединен с выходом 1-го разряда второго преобразователя двоичного кода в код остаточных классов, вход которого является входом множителя устройства, выходы младших и старших разрядов 1-го блока умножениясоединены с первым и вторым информациойными входами соответственно первого коммутатора, первый и второй управляющие входы которого соединены 50 с четвертым и пятым выходами соответственно блока микропрограммного управления, -й выход первого коммутатора соединен с первым информационным вхо,дом ь-го разряда сумматора мантисс, второй информационный вход которогосоединен с выходом 1-го разряда регистра сдвига и входом д-го разрядапреобразователя кода системы остаточных классов в двоичный код, вход 1-го разряда которого (где=К+1, К+2,2 К) соединен с выходом ь-го разряда регистра мантиссы множителя, выход -го разряда сумматора мантисс соединен с информационным входом 1-го разряда регистра сумматора мантисс, информационный вход нулевого разряда которого соединен с выходом переноса сумматора мантисс, шестой выход блока микропрограммного управления соединен с входом разрешения записи регистра сумматора мантисс, выход которого соединен с информационным входом регистра сдвига, вход разрешения записи которого соединен с седьмым выходом блока микропрограммного управления, восьмой и девятый выходы которого соединены с входами разрешения сдвига и сброса соответственно регистров сдвига и мантиссы множителя, десятый выход блока микропрограммного управления соединен с входом разрешения записи регистра мантиссы множителя, выход (ь)-го разряда регистра сдвига соединен с информационным входом сдвига -го разряда регистра сдвига, выход К-го разряда которого соединен с информационным входом сдвига регистра мантиссы множителя, выход -го разряда которого соединен с информационным входом сдвига (1+ +1)-го разряда регистра мантиссы множителя, выходы младших двоичных разрядов 1-го Б-ичного разряда, (где 1= =1,22 К, Я -основание системы остаточных классов) преобразователя кода системы остаточных классов в двоичный код с первым информационным входом 1-го разряда второго коммутатора, вход управления которого соединен с одиннадцатым выходом блока микропрограммного управления, выход старших двоичных разрядов ш-го Б-ичного разряда (где ш=2,32 К) соединен с вторым информационным входом (ш)-го разряда второго коммутатора, информационный вход (2 К)-го разряда которого соединен с шиной логического нуля устройства, выход старших двоичных разрядов первого 5 в ично разряда преобразователя кода системы остаточных классов в двоичный код соединен с входом элемента ИЛИ-НЕ, выход которого соединен с входом признака разрешения нормализации мантиссы блока микропрограммного управления, двенадцатый выход которого соединен с входами разрешения записи ре 1280 б 24 10регистров порядка множимого и множителя, информационные входы которыхсоединены соответственно с входамипорядка множимого и.множителя устройства, выходы регистров порядка множимого и множителя соединены соответственно с первым и вторым входами сумматора порядков, выходы нулевого ипервого разрядов которого соединеныс первыми входами первой и второй щсхем сравнения, выходы которых соединены соответственно с входами сравнения с логическим нулем и логическойединицей блока микропрограммногоуправления, тринадцатый выход которого соединен с первым управляющим входом третьего коммутатора, вторые входы первой и второй схем сравнениясоединены соответственно с нинами логического нуля и логической ециницы 20устройства, инверсный выходпервого разряда сумматорапорядков соединен с вторым управляющим входом третьего коммутатора, информационные входы которого соединены с выходами р-х разрядов.сумматора порядков (где р=2 п, имаксимальная разрядность сумматорапорядков), выход третьего коммутатора соединен с информационным входомсчетчика порядков, выходы первого ивторого разрядов которого соединеныс первым и вторым входами анализапорядка результата блока микропрограммного управления, четырнадцатыйвыход которого соединен с входамиустановки нуля счетчика и триггера,выход которого соединен с входом признака переполнения порядка блока микропрограммного управлення, пятнадцатый и шестнадцатый выходы которогосоединены соответственно с входамиустановки в единицу триггера и счетным входом счетчика соответственно,выход второго коммутатора являетсявыходом мантиссы произведения устройства, выход счетчика порядков является выходом порядка произведенияустройства, 12806241280624 5,91 И 7 Редак ежнин Тираж 67 Зак Подписно ул. Проектная, 4 изводственно-полиграфическое предприятие, г, Ужг 7067/54 ВНИИПИ Госу по дел 113035, Москвоставителв Н,МаркеловаехредЛ,Олейник Корректор М,демчи енного комитета СССРбретений и открытий5, Раушская наб., д. 4

СмотретьЗаявка

3919186, 01.07.1985

ПРЕДПРИЯТИЕ ПЯ А-7638, МОСКОВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ЕВСТИГНЕЕВ ВЛАДИМИР ГАВРИЛОВИЧ, КОШАРНОВСКИЙ АЛЕКСАНДР НИКОЛАЕВИЧ, МАРКИН АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: запятой, плавающей, умножения, чисел

Опубликовано: 30.12.1986

Код ссылки

<a href="https://patents.su/9-1280624-ustrojjstvo-dlya-umnozheniya-chisel-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел с плавающей запятой</a>

Предыдущий патент: Дифференцирующее устройство

Следующий патент: Устройство для умножения комплексных чисел в модулярной системе счисления

Случайный патент: Совмещенная электромашинная трехфазно-пятифазная обмотка