Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

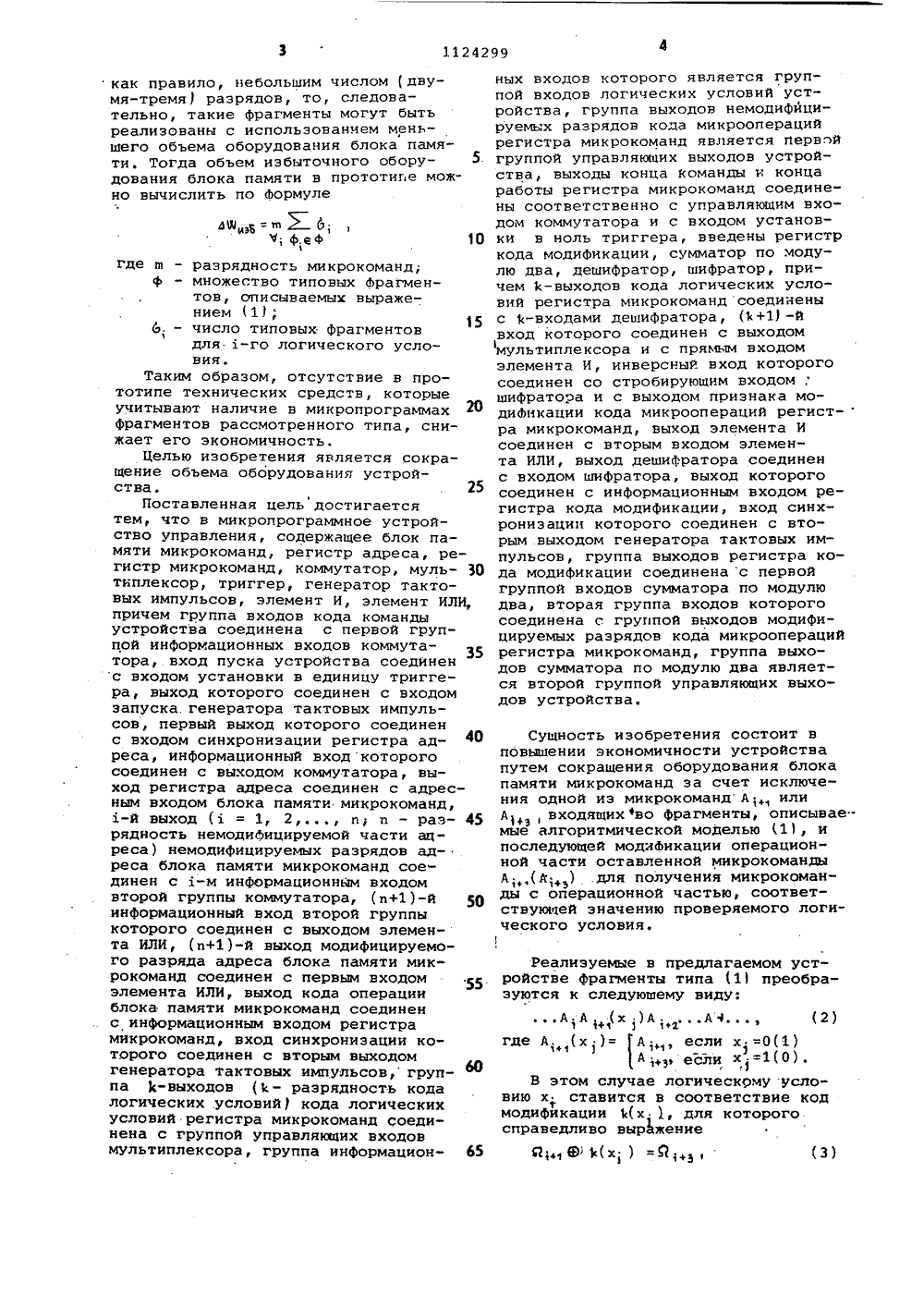

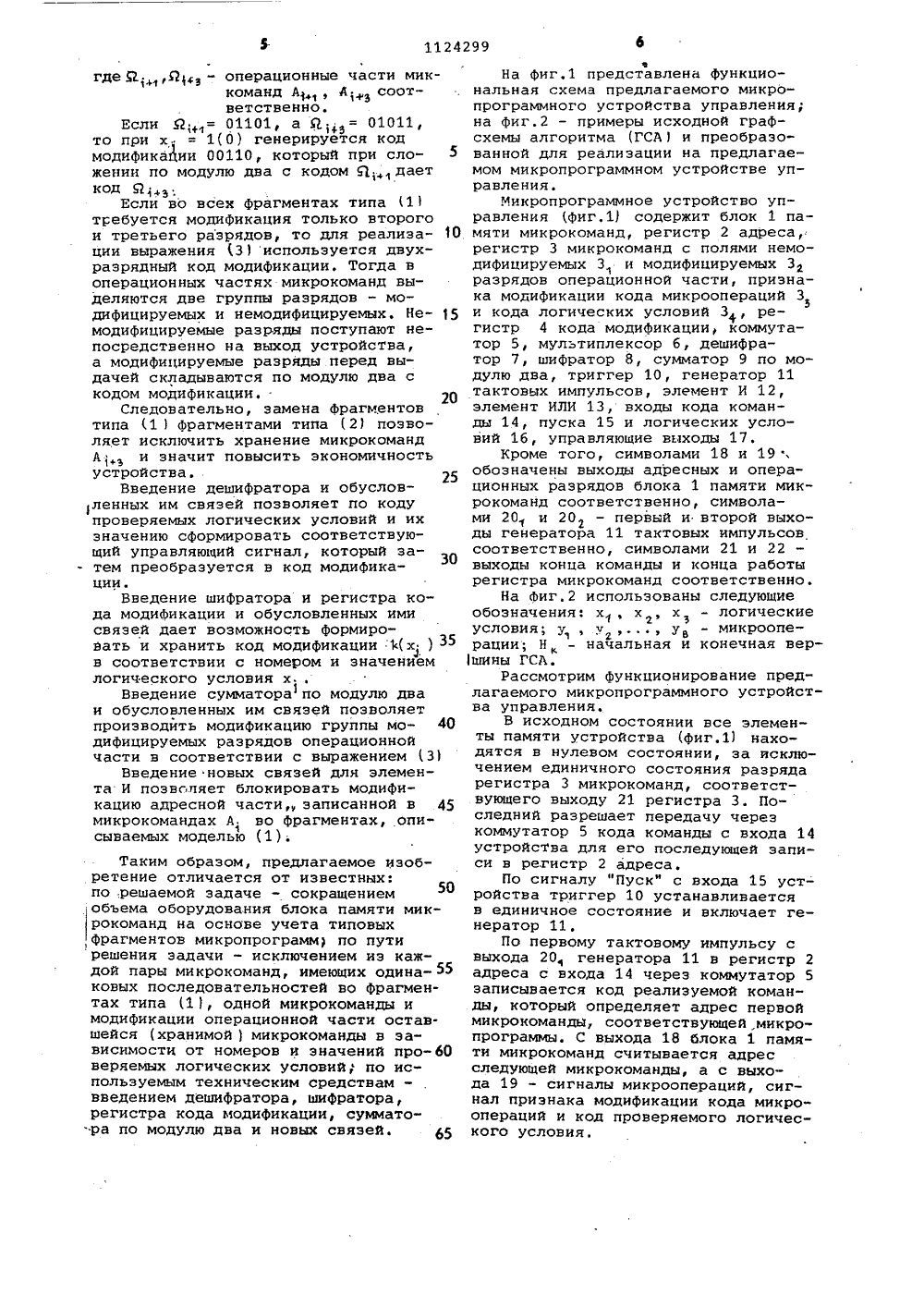

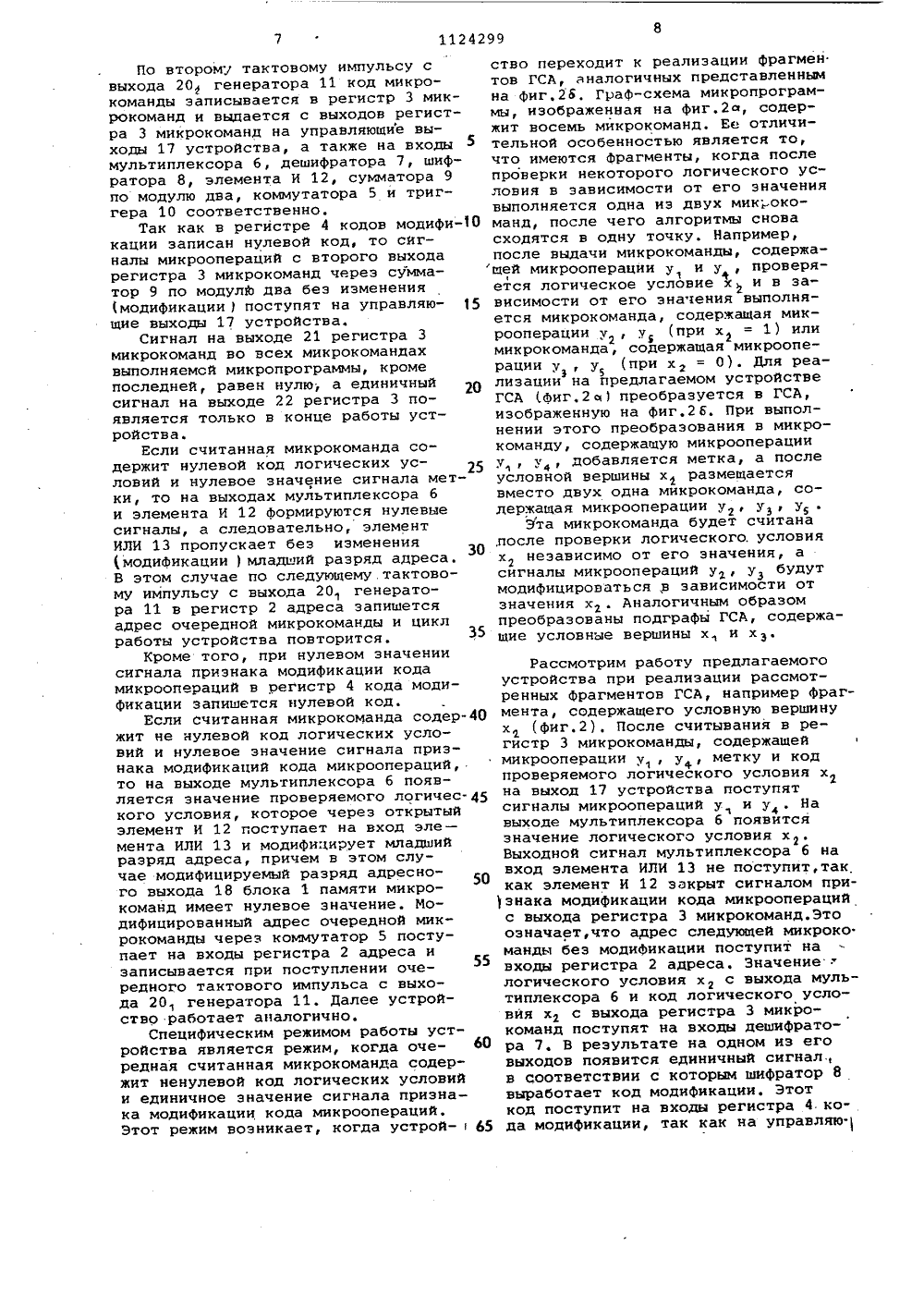

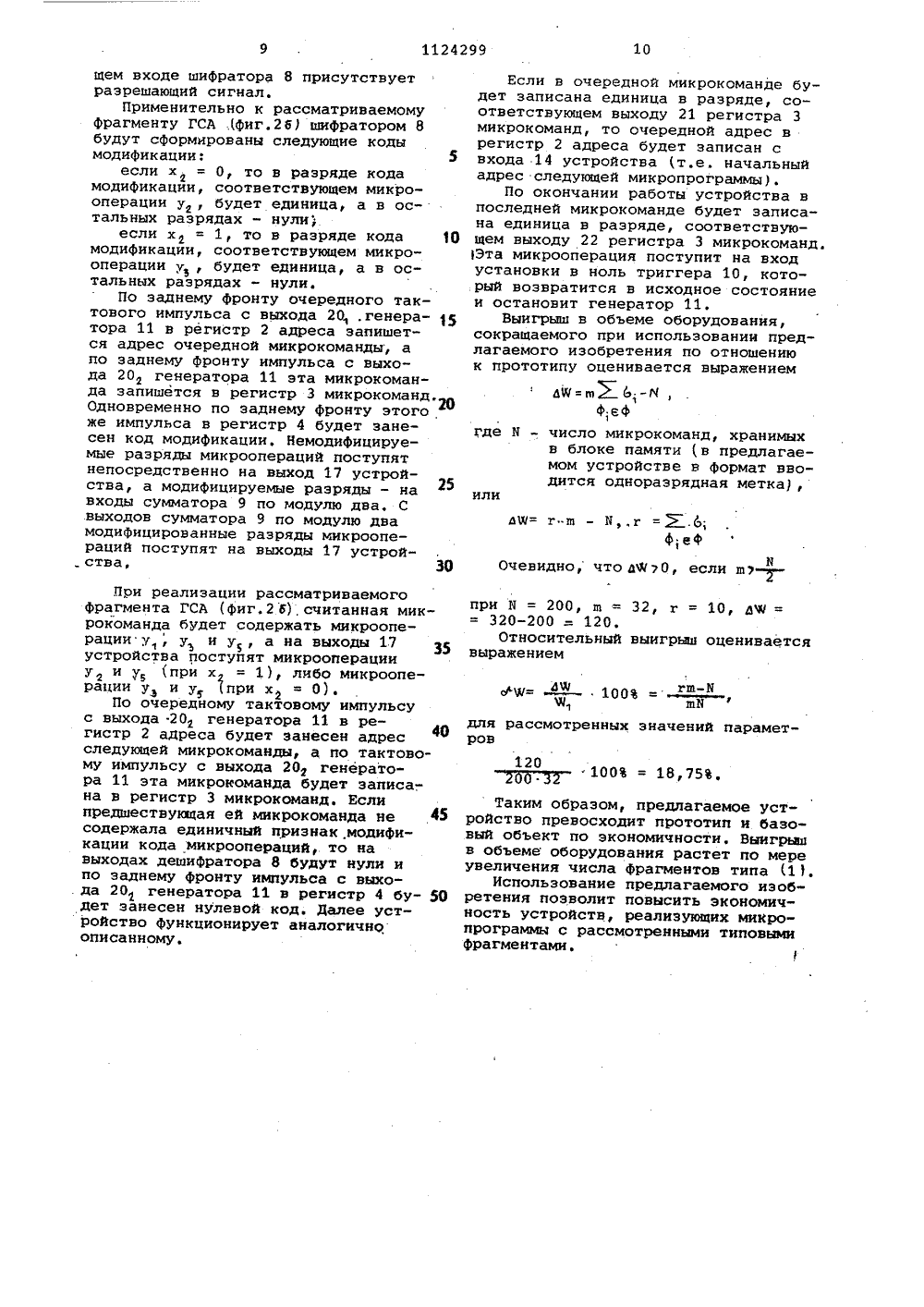

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 11% (11) ЗСЮ С 06 Р 9 22 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее блок памятимикрокоманд, регистр адреса, регистр микрокоманд, коммутатор, мультиплексор, триггер, генератор тактовЫх импульсов, элемент И, элемент ИЛИ, причем группа входов кодакоманды устройства соединена с первой группой информационных входовкоммутатора, вход пуска устройствасоединен с входом установки в единицу триггера, выход котсрого соединен с входом запуска генераторатактовых импульсов, первый выходкоторого соединен с входом синхронизации регистра адреса, информационный вход которого соединен с выходомкоммутатора, выход регистра адресасоединен с адресным входом блока памяти микрокоманд, 1-й выход ( 1=1,2п,п - разрядность немодифицируемой части адреса) немодифицируемых разрядов адреса блока памятимикрокоманд соединен с 1-м информационным входом второй группы коммутатора, (и + 1)-й информационныйвход второй группы которого соединенс выходом элемента ИЛИ, (и + 1)-йвыход модифицируемого разряда адреса блока памяти микрокоманд соединенс первым входом элемента ИЛИ, выходкода операции блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, вход синхронизации которого соединен с вторым выходом генератора тактовых импульсов, группа 1-выходов (Ъ- разрядность кода логических условий ) кода логических условий регистра микрокоманд соединена с группой управляющих входов мультиплексора, группа информационных входов которого является группой входов логических условий устройства, группа выходов немодифицируемых разрядов кода микро- операций регистра микрокоманд является первой группой управляющих выходов устройства, выходы конца команды и конца работы регистра микро- команд соединены соответственно сЩ управляющим входом коммутатора и с входом установки в ноль триггера, о т л и ч а ю щ е е с я тем, что, с целью сокращения объема оборудования, устройство содержит регистр кода модиФикации, сумматор по модулю два, дешиФратор, шифратор, причем М-выходов кода логических условий регистра микрокоманд соединены сМ-входами дешифратора, ( + 1)-йвход которого соединен с выходоммультиплексора и с прямым входомэлемента И, инверсный вход которого соединен со стробирующим входомшифратора и с выходом признака модификации кода микроопераций регистра микрокоманд, выход элемента Исоединен с вторым входом элемента ИЛИ, выход дешифратора соединенс входом шифратора, выход которогосоединеч с информационным входомрегистра кода модиФикации, входсинхронизации которого соединен свторым выходом генератора тактовыхимпулвсов, группа выходов регистракода модификации соединена с первойгруппой входов сумматора по модулюдва, вторая группа входов которбгосоединена с группой выходов модифицируемых разрядов кода микроопера1124299 йий регистра микрокоманд, группавыходов сумматора по модулю два яв 1Изобретение относится к цифРовойвычислительной технике и может бытьиспользовано при проектировании микропрограммных устройств управлениядля ЭВМ и вычислительных систем. 5Известно микропрограммное устройство управления, содержащее блок памяти. микрокоманд, регистр адреса,регистр микрокоманд, блок синхронизации, формирователь адреса, буферный регистр, элементы И, ИЛЙ 1,Недостатхом указанного устройстваявляется низкая экономичность, обусловленная наличием избыточности воперационных частях микрокоманд.Известно микропрограммное устройство управления, содержащее регистры адреса и микрокоманд, блокпамяти микрокоманд, генератор тактовых импульсов, триггер управления,блок формирования адреса, элементы И, ИЛИ, дешифратор 23,Недостатком этого устройства является низкое быстродействие, вызванное тем, что формирование очередной операционной микрокоманды 25осуществляется после считывания базовой микрокомандЫ путем циклического сдвига кода на заданное числоразрядов,Наибопее близким к изобретению 30по технической сущности и достигаемому положительному эффекту является микропрограммное устройство управления, содержащее лок памятимикрокоманд, регистры адреса и микрокоманд, триггер пуска, генератортактовых импульсов, коммутатор,мультиплексор и элемент И, причемвход пуска, устройства и выход конца работы регистра микрокоманд соединены соответственно с единичными нулевым входами триггера пуска,выход которого соединен с входомгенератора тактовых импульсов, первый и второй выходы которого соединены с входами синхронизации регистров адреса и микрокоманд соответственно, выход конца команды регистра микрокоманд и вход кода операцииустройства соединены соответственнос управляющим и первым информационным входами коммутатора, выход которого соединен с информационным входом регистра адреса, выходкоторого соединен с входом блока-памяти микрокоманд, первый выход 55которого соединен с информационным ляется второй группой управляющихвыходов устройства. 2входом регистра микрокоманд, второйи третий выходы блока памяти микрокоманд соединены с вторым информационным входом коммутатора и первымвходом элемента ИЛИ соответственно,выход которого соединен с третьиминформационным входом коммутатора,выходы микроопераций и кода логических условий регистра микрокоманди вход логических условий устройства соединены соответственно с выходом микроопераций устройства, адресным и информационным входами мультиплексора, выход которого соединенс вторым входом элемента ИЛИЭ.Недостатком указанного устройства является низкая экономичность,обусловленная избыточностью оборудования блока памяти микрокоманд, вызванной тем, что структура устройства и имеющиеся технические средства недостаточно учитывают типовыефрагменты, встречающиеся в микропрограммах, реализуемых устройством,Примером такого типового фрагмента является фрагмент, описываемыйследующей логической схемой алгоритма:А;х. 1 А. ЙА А 1 ФАш Ф (1)А+ , АМ - микрокомандц;.х - логическое условие, от которогоосуществляетсяпереход к микрокомандам А;,(при х=1 илиА+ (при х =О);мз - тождественйо ложное логическоеусловие, которое обеспечивает безусловный .переход от микрокомандц А;, к микрокоманде А 1+гОптимальной особенностью данйоготипового фрагмента является то, чтомикрокоманды, следующие в микропрограмме за ветвлением, имеют общегопоследователя. Следовательно, такиемикрокоманды имеют одинаковые адресные части и идентичное содержимоеполей кода логических условий и отличаются только операционными частями. Поскольку операционные части указанных микрокоманд отличаются,как правило, небольшим числом (двумя-тремя) разрядов, то, следовательно, такие фрагменты могут бытьреализованы с использованием меньшего объема оборудования блока памяти. Тогда объем избыточного сбору.дования блока памяти в прототипе можно вычислить по формуле 4 физБ щ-)М; феф 10где щ - разрядность микрокоманд,ф - множество типовых фрагментов, описываемых выражением (1);6. - число типовых фрагментовдля -го логического условия.Таким образом, отсутствие в прототипе технических средств, которыеучитывают наличие в микропрограммах 20фрагментов рассмотренного типа, снижает его экономичность,Целью изобретения является сокращение объема оборудования устройства. 25Поставленная цель достигаетсятем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, коммутатор, мультиплексор, триггер, генератор тактовых импульсов, элемент И, элемент ИЛИ,причем группа входов кода командыустройства соединена с первой группой информационных входов коммутатора, вход пуска устройства соединен35с входом установки в единицу триггера, выход которого соединен с входомзапуска. генератора тактовых импульсов, первый выход которого соединенс входом синхронизации регистра адреса, информационный вход которогосоединен с выходом коммутатора, выход регистра адреса соединен с адресным входом блока памяти микрокоманд,-й выход ( = 1, 2 и; п - разрядность немодифицируемой части адреса) немодифицируемых разрядов адреса блока памяти микрокоманд соединен с -м информационным входомвторой группы коммутатора, (и+1)-й 50информационный вход второй группыкоторого соединен с выходом элемента ИЛИ, (и+1)-й выход модифицируемого разряда адреса блока памяти микрокоманд соединен с первым входомэлемента ИЛИ, выход кода операции55блока памяти микрокоманд соединенс информационным входом регистрамикрокоманд, вход синхронизации которого соединен с вторым выходомгенератора тактовых импульсов, груп фпа М-выходов (М- разрядность кодалогических .условий) кода логическихусловий регистра микрокоманд Соединена с группой управляющих входовмультиплексора, группа информацион ных входов которого является группой входов логических условий устройства, группа выходов немодифицируемых разрядов кода микрооперацийрегистра микрокоманд является первойгруппой управляющих выходов устройства, выходы конца команды и концаработы регистра микрокоманд соединены соответственно с управляющим входом коммутатора и с входом установки в ноль триггера, введены регистркода модификации, сумматор по модулю два, дешифратор, шифратор, причем М-выходов кода логических условий регистра микрокоманд соединеныс %-входами дешифратора, (1+1) -йвход которого соединен с выходоммультиплексора и с прямым входомэлемента И, инверсный вход которогосоединен со стробирующим входом ;шифратора и с выходом признака модификации кода микроопераций регистра микрокоманд, выход элемента Исоединен с вторым входом элемента ИЛИ, выход дешифратора соединенс входом шифратора, выход которогосоединен с информационным входом регистра кода модификации, вход синхронизации которого соединен с вторым выходом генератора тактовых импульсов, группа выходов регистра кода модификации соединена с первойгруппой входов сумматора по модулюдва, вторая группа входов которогосоединена с группой выходов модифицируемых разрядов кода микрооперацийрегистра микрокоманд, группа выходов сумматора по модулю два является второй группой управляющих выходов устройства. Сущность изобретения состоит в повышении экономичности устройства путем сокращения оборудования блока памяти микрокоманд за счет исключения одной из микрокоманд А;+1 или А 1, входящих 1 во фрагменты, описываемые алгоритмической моделью (1), и последующей модификации операционной части оставленной микрокоманды А;(А;+ ) .для получения микрокоманды с ойерационной частью, соответствующей значению проверяемого логического условия,Реализуемые в предлагаемом устройстве фрагменты типа (1 преобразуются к следующему виду:А.А (х ) АА Ч, (2) где А,.(х )= А; если х =0(1)1+э если х =1(0).В этом случае логическому условию х ставится в соответствие код модифйкации %(х )., для которого справедливо выражение141)( Х )13 (3)где Р,. й)с - операционные части миккоманд А), А;+ соответственно.Если Я; = 01101, а Ц) = 01011, то при х. = 1(0) генерируется код модификации 00110, который при сло женин по модулю два с кодом Ядает код Я,з.Если во всех фрагментах типа (1) требуется модификация только второго и третьего разрядов, то для реализа- )О ции выражения (3) используется двухраэрядный код модификации, Тогда в операционных частях микрокоманд выделяются две группы разрядов - модифицируемых и немодифицируемых, Не- )5 модифицируемые разряды поступают непосредственно на выход устройства, а модифицируемые разряды перед выдачей складываются по модулю два с кодом модификации, . 20Следовательно, замена Фрагментов типа (1 ) Фрагментами типа (2) позволяет исключить хранение микрокоманд А и значит повысить экономичность устройства, 25Введение дешифратора и обуслов)ленных им связей позволяет по коду проверяемых логических условий и их значению сформировать соответствующий управляющий сигнал, который затем преобразуется в код модификации.Введение шифратора и регистра кода модификации и обусловленных ими связей дает возможность Формировать и хранить код модификации %(х ) 354 в соответствии с номером и значением логического условия хВведение сумматора по модулю два и обусловленных им связей позволяет производйть модификацию группы мо дифицируемых разрядов операционной части в соответствии с выражением (3)Введение новых связей для элемента И позволяет блокировать модификацию адресной части, записанной в 45 микрокомандах А во Фрагментах, описываемых моделью (1).Таким образом, предлагаемое изобретение отличается от известных: по,решаемой задаче - сокращением объема оборудования блока памяти микрокоманд на основе учета типовых ,фрагментов микропрограмм) по пути решения задачи - исключением из каждой пары микрокоманд, имеющих одина новых последовательностей во фрагментах типа (1 ), одной микрокоманды и модификации операционной части оставшейся (хранимой ) микрокоманды в зависимости от номеров и значений проверяемых логических условий; по используемым техническим средствам - введением дешифратора, шифратора, регистра кода модификации, суммато.ра по модулю два и новых связей. 65 На фиг,1 представлена функциональная схема предлагаемого микропрограммного устройства управления;на фиг.2 - примеры исходной графсхемы алгоритма (ГСА) и преобразованной для реализации на предлагаемом микропрограммном устройстве управления.Микропрограммное устройство управления (фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 адреса,:регистр 3 микрокоманд с полями немодифицируемых 3 и модифицируемых 32разрядов операционной части, признака модификации кода микроопераций 3и кода логических условий 3, ре 5гистр 4 кода модификации, коммутатор 5, мультиплексор б, дешифратор 7, шиФратор 8, сумматор 9 по модулю два, триггер 10, генератор 11тактовых импульсов, элемент И 12,элемент ИЛИ 13, входы кода команды 14, пуска 15 и логических условий 1 б, управляющие выходы 17.Кроме того, символами 18 и 19обозначены выходы адресных и операционных разрядов блока 1 памяти микрокоманд соответственно, символами 20 и 20 - первый и второй выхо 2ды генератора 11 тактовых импульсовсоответственно, символами 21 и 22выходы конца команды и конца работырегистра микрокоманд соответственно.На Фиг,2 использованы следующиеобозначения: х, х , х - логические2 Уусловия; у , у у - микроопе 1 "гффрации; Н - начальная й конечная вершины ГСА,Рассмотрим функционирование предлагаемого микропрограммного устройства управления,В исходном состоянии все элементы памяти устройства (фиг.1) находятся в нулевом состоянии, за исключением единичного состояния разрядарегистра 3 микрокоманд, соответствующего выходу 21 регистра 3. Последний разрешает передачу черезкоммутатор 5 кода команды с входа 14устройства для его последующей записи в регистр 2 адреса,По сигналу "Пуск" с входа 15 устройства триггер 10 устанавливаетсяв единичное состояние и включает генератор 11,По первому тактовому импульсу свыхода 20 генератора 11 в регистр 2адреса с входа 14 через коммутатор 5записывается код реализуемой команды, который определяет адрес первоймикрокоманды, соответствующей, микропрограммы. С выхода 18 блока 1 памяти микрокоманд считывается адресследующей микрокоманды, а с выхода 19 - сигналы микроопераций, сигнал признака модификации кода микроопераций и код проверяемого логического условия.По второму тактовому импульсу с выхода 20 генератора 11 код микро- команды записывается в регистр 3 микРокоманд и выдается с выходов регистра 3 микрокоманд на управляющие выходы 17 устройства, а также на входы мультиплексора б, дешифратора 7, шифратора 8, элемента И 12, сумматора 9 по модулю два, коммутатора 5 и триггера 10 соответственно.Так как в регистре 4 кодов модификации записан нулевой код, то сигналы микроопераций с второго выхода регистра 3 микрокоманд через сумматор 9 по модулю два без изменения (модификации 1 поступят на управляю щие выходы 17 устройства.Сигнал на выходе 21 регистра 3 микрокоманд во всех микрокомандах выполняемсй микропрограммы, кроме последней, равен нулю; а единичный сигнал на выходе 22 регистра 3 появляется только в конце работы устройства.Если считанная микрокоманда содержит нулевой код логических условий и нулевое значение сигнала метки, то на выходах мультиплексора 6 и элемента И 12 формируются нулевые сигналы, а следовательно, элемент ИЛИ 13 пропускает без изменения модификации )младший разряд адреса. В этом случае по следующему.тактовому импульсу с выхода 201 генератора 11 в регистр 2 адреса запишется адрес очередной микрокоманды и цикл работы устройства повторится.Кроме того, при нулевом значении сигнала признака модификации кода микроопераций в регистр 4 кода модификации запишется нулевой код.Если считанная микрокоманда содержит не нулевой код логических условий и нулевое значение сигнала признака модификаций кода микроопераций, то на выходе мультиплексора б появляется значение проверяемого логического условия, которое через открытый элемент И 12 поступает на вход эле - мента ИЛИ 13 и модифицирует младший разряд адреса, причем в этом случае модифицируемый Разряд адресного выхода 18 блока 1 памяти микро- команд имеет нулевое значение. Модифицированный адрес очередной микрокоманды через коммутатор 5 поступает на входы регистра 2 адреса и записывается при поступлении очередного тактового импульса с выхода 20 генератора 11. Далее устройство работает аналогично.Специфическим режимом работы устройства является режим, когда оче редная считанная микрокоманда содержит ненулевой код логических условий и единичное значение сигнала признака модиФикации кода микроопераций, Этот режим возникает, когда устрой-65 ство переходит к реализации Фрагмен тов ГСА, аналогичных представленным на Фиг,2. Граф-схема микропрограммы, изображенная на фиг,2 а, содержит восемь микрокоманд, Ее отличительной особенностью является то, что имеются фрагменты, когда после проверки некоторого логического условия в зависимости от его значения выполняется одна из двух мик;-окоманд, после чего алгоритмы снова сходятся в одну точку. Например, после выдачи микрокоманды, содержащей микрооперации у, и у , проверяется логическое условие хи в зависимости от его значения выполняется микрокоманда, содержащая микрооперации у , у (при х = 1) или микрокоманда, содержащая микрооперации у , у (при х = О). Для реализации на йредлагаемом устройстве ГСА (Фиг,2 ) преобразуется в ГСА, изображенную на фиг,2 6. При выполнении этого преобразования в микро- команду, содержащую микрооперации У, У , добавляется метка, а после условйой вершины х размещается вместо двух одна микрокоманда, содержащая микрооперации уузуЭта микрокоманда будет считана ,после проверки логического. условия х независимо от его значения, а 2сигналы микроопераций у, уз будут модифицироваться в зависимости от значения х. Аналогичным образом преобразованы подграфы ГСА, содержащие условные вершины х и хз.Рассмотрим работу предлагаемого устройства при реализации рассмотренных Фрагментов ГСА, например Фрагмента, содержащего условную вершину х (Фиг,2)После считывания в регйстр 3 микрокоманды, содержащей микрооперации у у , метку и код проверяемого логического условия х на выход 17 устройства поступят сигналы микроопераций у и у . На выходе мультиплексора 6 появйтся значение логического условия х. Выходной сигнал мультиплексора б на вход элемента ИЛИ 13 не поступит,так как элемент И 12 закрыт сигналом при 1 знака модификации кода микроопераций с выхода регистра 3 микрокоманд.Это означает,что адрес следующей микроко. манды без модификации поступит на входы регистра 2 адреса. Эначениелогического условия х с выхода мультиплексора 6 и код логического условия х с выхода регистра 3 микро- команд поступят на входы дешифратора 7. В результате на одном из его выходов появится единичный сигнал., в соответствии с которым шифратор 8 выработает код модификации. Этот код поступит на входы регистра 4. кода модификации, так как на управляю.щем входе шифратора 8 присутствует разрешающий сигнал.Применительно к рассматриваемому фрагменту ГСА Лфиг,26) шифратором 8 будут сформированы следующие коды модификации: 5если х = О, то в разряде кода2модификации, соответствующем микро- операции у, будет единица, а в остальных разрядах - нули;если х = 1, то в разряде кода 10 модификацйи, соответствующем микро- операции у , будет единица, а в остальных разрядах - нули.По заднему фронту очередного тактового импульса с выхода 20 генера тора 11 в регистр 2 адреса запишется адрес очередной микрокоманды, а по заднему Фронту импульса с выхода 20 генератора 11 эта микрокоманда зайишется в регистр 3 микрокоманд. Одновременно по заднему фронту этого же импульса в регистр 4 будет занесен код модификации. Немодифицируемые разряды микроопераций поступят непосредственно на выход 17 устройства, а модифицируемые разряды - на входы сумматора 9 по модулю два, С .выходов сумматора 9 по модулю два модифицированные разряды микроопераций поступят на выходы 17 устройства, 30 При реализации рассматриваемого фрагмента ГСА (фиг.2 6),считанная микрокоманда будет содержать микрооперации у, у и у , а на выходы 17 устройства постуйят микрооперации у и у (при х = 1), либо микрооперации у и у при х = О).По очередному тактовому импульсу с выхода 20 генератора 11 в регистр 2 адреса будет занесен адрес следующей микрокоманды, а по тактовому импульсу с выхода 20 генератора 11 эта микрокоманда будет записа-. на в регистр 3 микрокоманд. Если предшествующая ей микрокоманда не .45 содержала единичный признак,модификации кода микроопераций, то на выходах дешифратора 8 будут нули и по заднему фронту импульса с выхо.да 20 генератора 11 в регистр 4 бу дет занесен нулевой код. Далее устройство функционирует аналогично описанному. Если в очередной микрокоманде будет записана единица в разряде, соответствующем выходу 21 регистра 3 микрокоманд, то очередной адрес в регистр 2 адреса будет записан с входа 14 устройства т.е. начальный адрес следующей микропрограммы).По окончании работы устройства в последней микрокоманде будет записана единица в разряде, соответствующем выходу 22 регистра 3 микрокоманд. Эта микрооперация поступит на вход установки в ноль триггера 10, который возвратится в исходное состояние и остановит генератор 11.Выигрыш в объеме оборудования, сокращаемого при использовании предлагаемого изобретения по отношению к прототипу оценивается выражениемд 19: в,Е Й-ЙФ;ефгде И - число микрокоманд, хранимыхв блоке памяти в предлагаемом устройстве в формат вводится одноразрядная метка),илийЮ= г-а М,.г = .Е.6; Ф;еФ М Очевидно, что а%0, если ш-упри Б = 200, а = 32, г = 10, аа =320-200 : 120.Относительный выигрыш оцениваетсявыражениемФащ 100йВ гш-Бч)1 щБдля рассмотренных значений параметров100 = 18,75.120Таким образом, предлагаемое устройство превосходит прототип и базовый объект по экономичности. Выигрыш в объеме оборудования растет по мере увеличения числа фрагментов типа (1 ).Использование предлагаемого изобретения позволит повысить экономичность устройств, реализующих микропрограммы с рассмотренными типовыми фрагментами.1124299 Составитель Ю.Ланцоведактор М;Недолуаенко ТехредТ. Дубинчак Коррек илипенко агород, ул ектна аэ 8281/38Тир ВНИИПИ Государстпо делам иэоб 113035, Москва, Ж-ЗюФ ЮФАН% филиал ППП фПатентф, гам 698 Подписиенного комитета СССРетений и открытийРаушская наб., д. 4/5

СмотретьЗаявка

3577579, 15.04.1983

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.11.1984

Код ссылки

<a href="https://patents.su/8-1124299-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Процессор с микропрограммным управлением

Следующий патент: Устройство для динамического преобразования адреса

Случайный патент: Состав для изготовления древесно-волокнистых плит