Устройство для вычисления функций в модулярном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

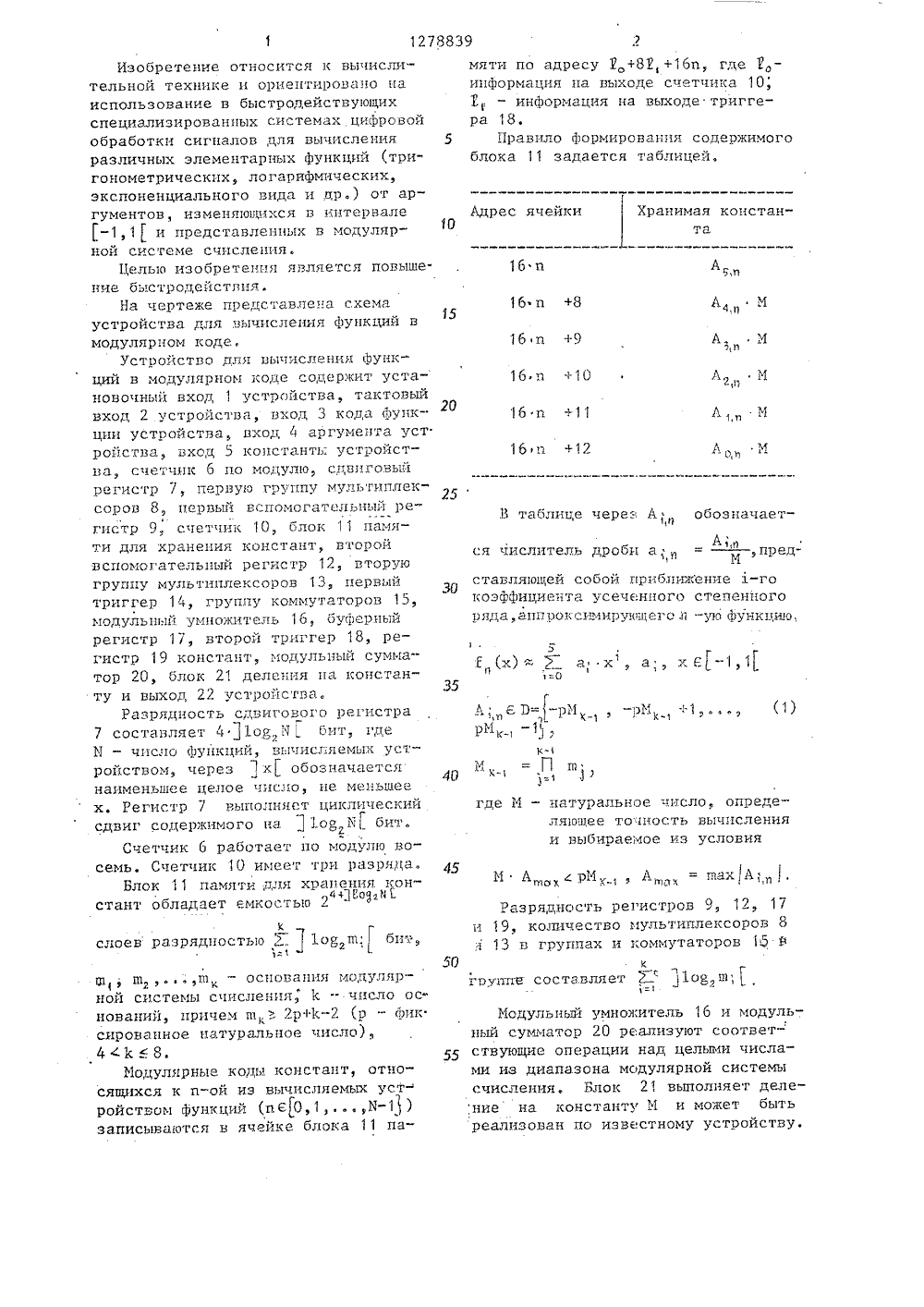

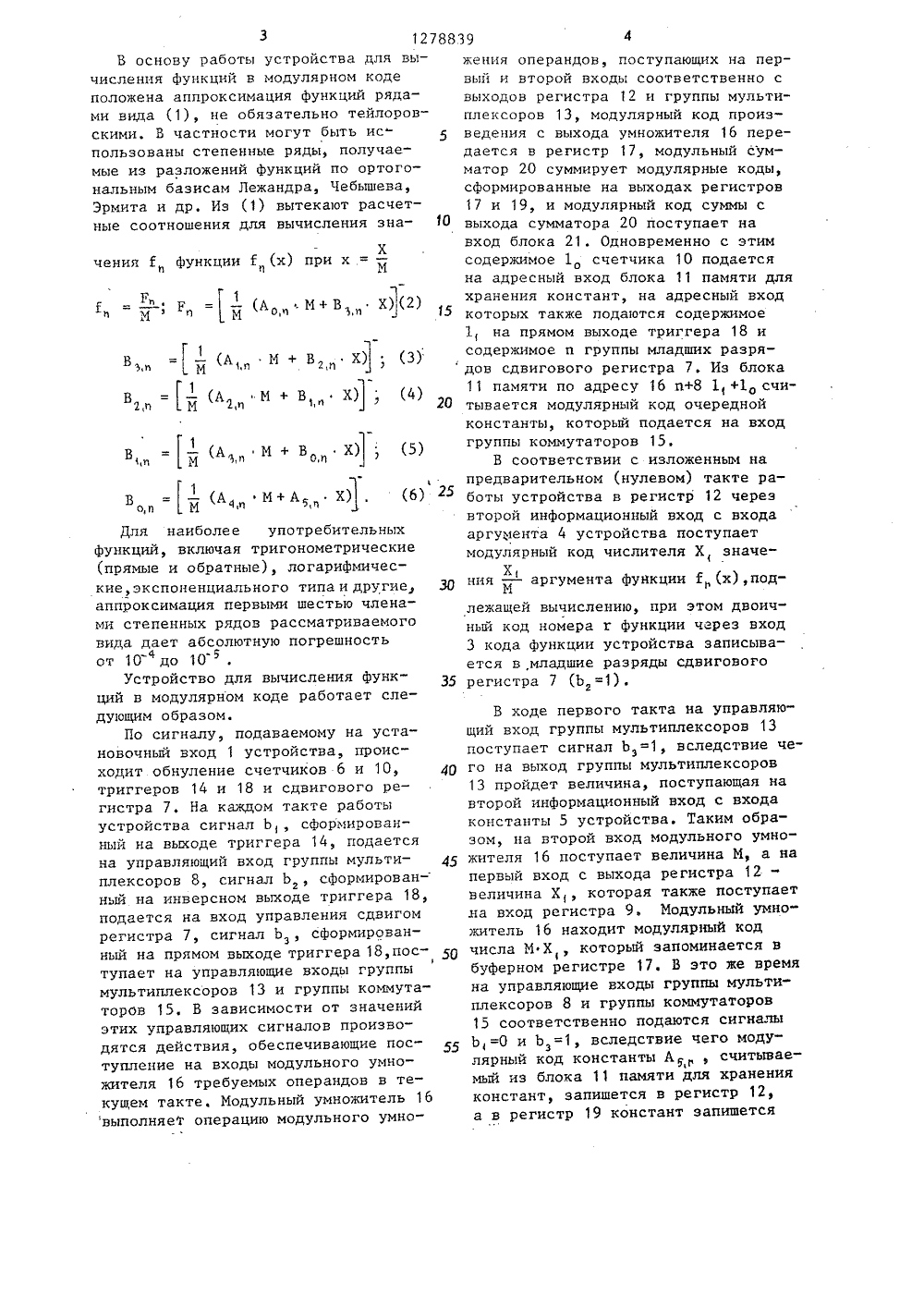

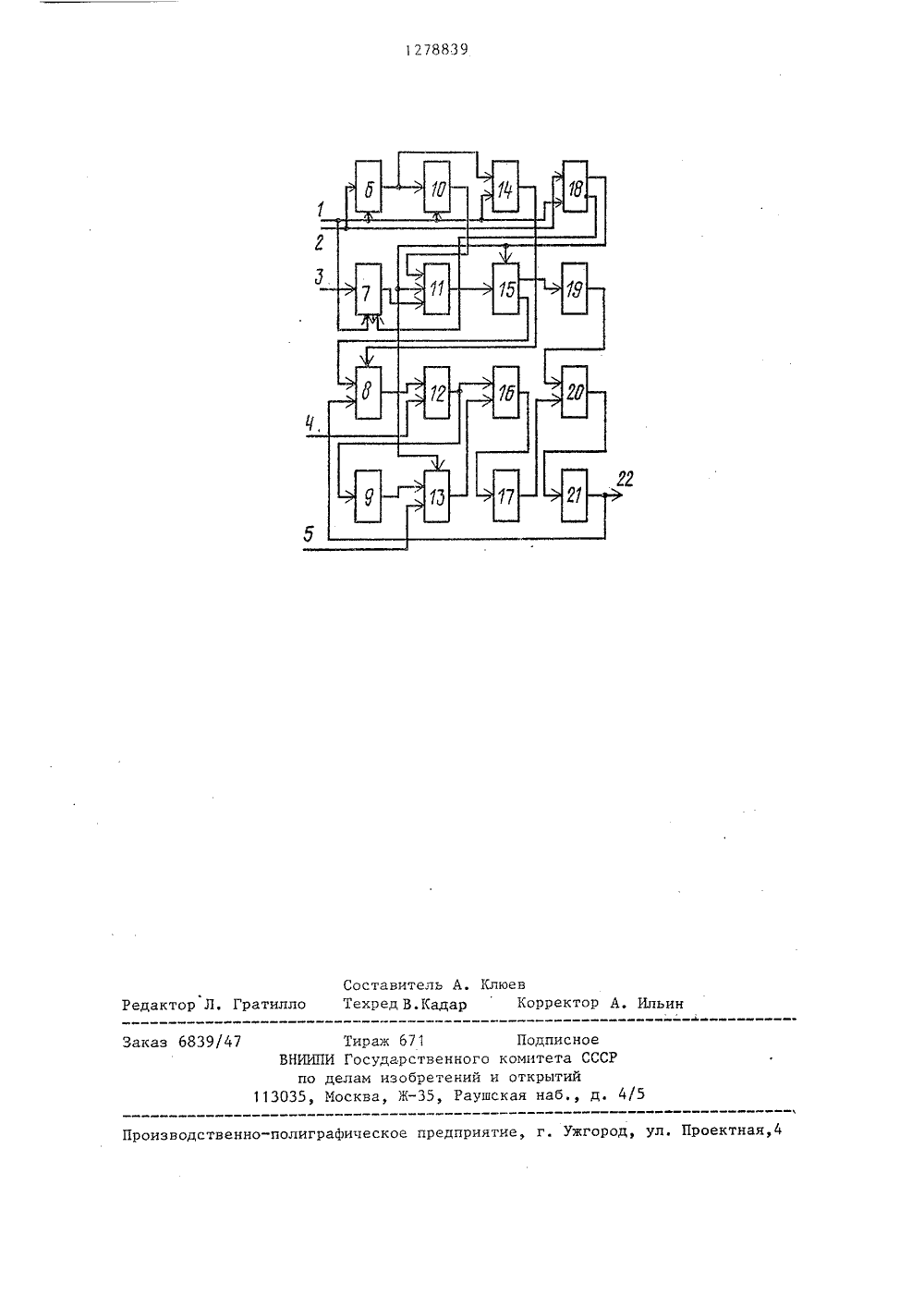

(72) А,А. М.Ю. Селян (53) 681.3 (56) Автор Бд 1103225Авторск У 983707,(54) УС ЦИИ В М (57) Из лительн использ связями ГОСУДАРСТВЕННЫЙ НОМ ПО ДЕЛАМ ИЗОБРЕТЕНИЙ АВТОРСКОМУ С(088.8)ское свидетельство СССРкл. С 06 Р 7/544, 1980.ое свидетельство СССРкл. С 06 Р 7/544, 1981. РОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКДУЛЯРНОМ КОДЕбретение относится к вычисй технике и ориентировано навание в быстродействующих вЯОпи 1278839 А 1 специализированных системах цифровой обработки сигналов для вычисления различных элементарных функций(тригонометрических, логарифмических, экспоненциального вида и других) от аргументов, представленныхв модулярной системе счисления. Цельизобретения состоит в повышениибыстродействия. Поставленная цельдостигается тем, что устройство, содержащее сдвиговый регистр, блок памяти для хранения констант, регистрконстант, модульный умножитель, модульный сумматор, группу коммутаторов, счетчик по модулю, два триггераи буферный регистр, содержит счетчикдве группы мультиплексоров и блокделения на константу с соответствую1278839 мяти по адресу 7 +82, +16 и, где 7,5 - информация ца выходе счетчика 10;1 - информация на выходе триггера 18.5 Иравило формирования содержимогоблока 11 задается таблицей. Изобретение относится к вычислительной технике и ориентироие 1 но ца использование в быстродействующих специализированных системах цифровой обработки сигналов для вычисления различных элементарных функций (тригонометрических, логарифмических, экспоненциального вида и др.) от аргументов, изменяющихся в интервале -1, 11 и представленных в модулярной системе счисления.Цель 1 о изобретеепЕя является повыше. ние быстродействия.На чертеже представлена схема устройства для вычисления функций в модулярцом коде.Устройство для вычисления функций в модулярном коде содер 5 кит установочный вход 1 устройства, тактовый вход 2 устройства, вход 3 кода функции устройства вхоее, 4 аргумента уст. ройства, вход 5 константь; устройства счетче 1 к 6 по модулю, сдвиговый регистр 7, первую группу мулЕтип 51 ексоров 8, первый вспомогательный регистр 9, счетчик 10, блок 11 памяти для хранения констант, второй вспомогательный регистр 12, вторую группу мультиплексоров 13, первый триггер 14, группу коммутатороЕз 15, мопульный умножитель 16, буферный регистр 17, второй триггер 18, регистр 19 констант, модульный сумматор 20, блок 21 деления па конс.танту и выход 22 устройства.Разрядность сдвигового регистраи7 составляет 41 О 8 к 1 бит, где И - число функций, вычисляемых устройством, через 1 х( обозначается наименьшее целое число, це меньшее х. Регистр 7 выполняет циклический сдвиг содержимого ца 1 оя К Г бит.Счетчик 6 работает по модулю восемь. Счетчик 10 имеет три разряда.Блок 11 памяти для храпения кон 14 Боу ЕЕ(. стант обладает емкостью 2 Адрес ячейки10 Хранимая констан- та ААМ 16 и +8 16 и +9 16 и +10 16 и +11 16 и +12 А, М А, М А М А 15,и 2513 таблице через А,ц обозначаетА 1,п, предся числитель дроби а;ставляющей собой приближение 1-гокоэффициента усеченного степенногоряда,аппрокскмирую 1 цего,11 -ую 115 ункцию,А, Я Т).=(-рМ , -рМ +1,рМ., -",КМ, = П шгде М - натуральное число, определяющее то:Еность вычисления и выбираемое из условия АглаяхрМ"1Ап,чк шах ( Разряцность регистров 9, 12, 17 и 19, количество мультиплексоров 8 4 13 в группах и коммутаторов 1 О в слоев разрядностью1 оя п 1, би:,50сгруппе составляет)1 ов,ш; ЕЕЕП 1в е 111ОСЕОВНЕ 1 И 51 МОДУЛЯР2кной системы счисления, 1 с - число оснований, причем тк 2 р+1-2 (р - фик. сированное натуральное число),4(1 с 8.Моцул 51 рные кОд 1)1 константу Относящихся к и-ой иэ вычисляемых уст- ройством функций (пей,1, И) записыьаются в ячеике блока 11 паМодульный умножитель 16 и модульный сумматор 20 реализуют соответ ствующие операции над целыми числами иа диапазона модулярной системысчисления. Блок 21 выполняет деле,ние на константу М и может бытьреализован по известному устройству,3 1278839В основу работы устройства для вычисления Функций в модулярном кодеположена аппроксимация функций рядами вида (1), не обязательно тейлоровскими. В частности могут быть использованы степенные ряды, получаемые из разложений функций по ортогональным базисам Лежандра, Чебышева,с Эрмита и др, Из (1) вытекают расчет ные соотношения для вычисления зна в регистра 7 (Ь =1). 35 40 45 50 55 Х чения Г Функции 1 (х) при х = -и П Мп(Аон М+В Х)(2)Р, 11 В = - (А, М + В Х) (3) Для наиболее употребительных Функций, включая тригонометрические (прямые и обратные), логарифмические,экспоненциального типа и другие аппроксимация первыми шестью членами степенных рядов рассматриваемого вида дает абсолютную погрешность от 10 до 10Устройство для вычисления функций в модулярном коде работает следующим образом.По сигналу, подаваемому на установочный вход 1 устройства, происходит обнуление счетчиков 6 и 10, триггеров 14 и 18 и сдвигового регистра 7. На каждом такте работы устройства сигнал Ь, сформированный на выходе триггера 14, подается на управляющий вход группы мультиплексоров 8, сигнал Ь сформированный на инверсном выходе триггера 18, подается на вход управления сдвигом регистра 7, сигнал Ь , сформированный на прямом выходе триггера 18,поступает на управляющие входы группы мультиплексоров 13 и группы коммутаторОв 15. В зависимости от значений этих управляющих сигналов производятся действия, обеспечивающие поступление на входы модульного умно- жителя 16 требуемых операндов в текущем такте. Модульный умножитель 16 выполняет операцию модульного умноения операндов, поступающих на перый и второй входы соответственно сыходов регистра 12 и группы мультилексоров 13, модулярный код произедения с выхода умножителя 16 переается в регистр 17, модульный суматор 20 суммирует модулярные коды,формированные на выходах регистров7 и 19, и модулярный код суммы сыхода сумматора 20 поступает навход блока 21. Одновременно с этимсодержимое 1 счетчика 10 подаетсяна адресный вход блока 11 памяти дляхранения констант, на адресный входкоторых также подаются содержимое1 на прямом выходе триггера 18 исодержимое и группы младших разря дов сдвигового регистра 7. Из блока11 памяти по адресу 16 и+8 1 +1 счи 20 тывается модулярный код очереднойконстанты, который подается на входгруппы коммутаторов 15,В соответствии с изложенным напредварительном (нулевом) такте ра 25 боты устройства в регистр 12 черезвторой информационный вход с входааргумента 4 устройства поступаетмодулярный код числителя Х значе(Х,30 ния - аргумента функции 2(х),подлежащей вычислению, при этом двоичный код номера г функции через вход 3 кода функции устройства записывается в младшие разряды сдвигового В ходе первого такта на управляю" щий вход группы мультиплексоров 13 поступает сигнал Ь =1, вследствие чего на выход группы мультиплексоров 13 пройдет величина, поступающая на второй информационный вход с входа константы 5 устройства. Таким образом, на второй вход модульного умно- жителя 16 поступает величина М, а на первый вход с выхода регистра 12- величина Х которая также поступает .на вход регистра 9. Модульный умно- житель 16 находит модулярный код числа М Х который запоминается в буферном регистре 17. В это же время на управляющие входы группы мультиплексоров 8 и группы коммутаторов 15 соответственно подаются сигналы Ь,=О и Ь,=1, вследствие чего модулярный код константы А, считываемый из блока 11 памяти для хранения констант, запишется в регистр 12, а в регистр 19 констант запишетсякод нуля. Модульный сумматор 20 иблок 21 на данном такте полезной работы не выполняют,На втором такте на вход управления сдвигом сдвигового регистра 7 подается сигнал Ь, =, при этом осуществляется циклический сдвиг его содержимого. а. в группу младших разрядов через вход 3 кода Функции устройства поступает двоичный код номера Функции Г (х). На управляющийвход группы мультиплексоров 13 поступает сигнал 1 з, =-О, поэтому на выходгруппы мультиплексоров 13 пройдет содерхалмое регистра 9, которое поступит на второй вход модульного умножителя 16, на первый вход которогоподается содержимое регистра 12. Модульный умножитель 16 получит модулярный код .величины Л ,Х которыйзапоминается в буферном регистре 17.Предыдущее содержимое регистра 17 вмодульном сумматоре 20 складываетсяс содержимым (ез данный момент нулевым) регистра 9 констант, модулярпый код величины М Х, с выхода модульного сумматора 20 передается в, блок 21, где со следующего тактаначнется операция пад этой величиной.Наряду с указанными действиямина втором такте на управляюшеле входыгрупп мультиплексоров 8 и коммутаторов 15 соответственно поступают сигналы Ь, =-0 и Ь, =О, поэтому в регистр19 констант поступает модулярный кодвеличины МА,1, которая считывается,из блока 11 памяти для хранения констант по адресу 16 г+8, а в регистр12 с входа 4 аргумента устройствапоступает модулярпый код числителяХ соответствующего значения аргуХхлента -М На третьем такте по сигналу Ь =1, подающемуся на управляющий вход группы мультиплексороез 13, на выход данной группы пройдет величина М, поступающая на второй информационный вход с входа э констаегеы устройсгва, с выхода регистра 12 величина Х поступает на вход регистра 9 игна первый вход модульного умножителя 16, на второй вход которого поступает величина М с выхода группы мультиплексоров 13. Модульный умно- житель 16 находит модулярный код числа МфХ , который запоминается в буферном регистре 17. 11 редыдущее 20 25 30 35 40 45 50 55 содержимое регистра 17 в модульном сумматоре 20 складывается с содержимьы М Арегистра 19 констант, модулярный код величины АХ,+М Ас выхода модульного сумматора 20 пе редается в блок 21, где со следующего такта начнется операция над этой величиной. В то же время на управляющие входы:.-рупп мультиплексоров8 и коммутаторов 15 соответственнопоступают слгназеы Ь =О и Ь =1 вследствие чего модулярный код константыЛсчитываемый из блока 11 памятидля хранения коестант по адресу16 5, записывается в регистр 12,а в регистр 9 запишется кодееуляНа последующ лх шести тактах работы устройства (с четвертого по девятый) п 1 зоисходят следующие действия; на четвертом, пятом и шестомтактах для Функции Г (х) повторяются операции, выполненные на тактахс первого по третий для функцииК(х), а с четвертого и .шестого тактов начинается зычисление соответ -ственно функции Г+ (х) и К (х), длякоторых повторя.отея операции, аналогичные описанным, Б результате натактах с четвер гого по девятый вблок 21 соответственпо поступят величины Х М Л Х + МАХ М,+ М, Л В отличие от второго такта(а также четвертого и шестого) навосьмом такте после циклическогосдвига содержимого сдвигового регист.ра 7 в него через вход 3 кода ФуеЛкции устройства новая информация непоступает, соответственно прекращается поступление новой информации ичерез вход 4 аргумента устройства. Наряду с этим на восьмом такте на выходе переноса счетчика 6 появится единичный сигнал, в соответствии с этим содерхалмое счетчика О (в данном случае нулевое) наращивается на единицу и на его выходе формируется код числа "1", а триггер 14 устанавливается в единичное состояние, Так как выполнение в блоке 21 операции занимает шесть тактов, то, начиная с восьмого такта, с выхода блока 21 через второй информационный вход мультиплексора 8 в регистр 12 начнут поступать полученные значения в порядке поступления входных величин на вход блока 21. В частности, навосьмом такте в регистр 12 поступит модулярный код величины Х,.На девятом такте по сигналу Ь =1, подающемуся на селекторный вход группы мультиплексоров 13, на выход пройдет величина М, поступающая на второй информационный вход с входа 5 константы устройства, с выхода регистра 12 вепичина Х передается в регистр 9 и на первый вход модульно;го умножителя 16, на второй вход которого с выхода группы мультиплексоров 13 поступает величина М. Модульный умножитель 16 находит модулярный код числа М Х который запоминается в буферном регистре 17. Одновременно с этим на селекторные входы групп мультиплексоров 8 и коммутаторов 15 поступают сигналы Ь =1 и Ь, =1, вследствие чего в ре гистр 19 констант запишется код нуля, а в регистр 12 - модулярный код величины В ц, поступаюший с выхода блока 21 6( )На десятом такте на входуправления сдвигом сдвигового регистра 7 подается сигнал Ь, =1, при этом осуществляется циклический сдвиг его содержимого и на выходе младших раз- щ рядов сдвигового регистра 7 появится двоичный код номера Б функции. На управляющий вход группы мультиплексоров 13 поступает сигнал Ь, =О,поэтому содержимое регистра 9, поступающее на второй информационный вход, пройдет на второй вход модульного умножителя 16, на первый вход которого поступает с выхода регистра 12 величина В . Модульный умножи тель 16 получит модулярный код величины В,Х который запоминается вбуферном регистре 17. Предыдущее содержимое регистра 17 в модульном сумматоре 20 складывается с содержимым регистра 19 констант, модулярный код величины М Х, с выхода модульного сумматора 20 подается в блок 21. Наряду с указанными действиями на десятом такте на селекторные входы групп мультиплексоров 8 и коммутаторов 15 соответственно поступают сигналы Ь, =1 и Ь =О, поэтому в регистр 19 констант поступает модулярный код величины МАсчитываемый из блока 11 памяти для хранения констант по адресу 16 г+9 (таблица), а в регистр 12 с выхода блока 21 поступает модулярный код величины Х. На одиннадцатом такте по сигналу Ь, =1, подающемуся на управляющий вход группы мультиплексоров 13, на выход данной группы пройдет величина М, поступающая на второй информационный вход с входа 5 константы устройства, содержимое регистра 12 поступает на вход регистра 9 и на первый вход модульного умножителя 16, на второй вход которого с выхода группы мультиплексоров 13 поступает величина М. Модульный умножитель 16 находит модулярный код числа МХ , который запоминается в буферном регистре 17. Предыдущее содержимое регистра 17 в модульном сумматоре 20 складывается с содержимым ре.гистра 19 констант, модулярный код величины М А +В Х, с выхода модульного сумматора 20 передается в блок 21. Наряду с этим на управляющие входы групп мультиплексоров 8 и коммутаторов 15 соответственно поступают сигналы Ь =1 и Ь =1, вследствие чего в регистр 19 запишется код нуля, а модулярный код константы В с выхода блока 21 поступит в регистр 12. На последующих шести тактах работы устройства (с двенадцатого по сем" надцатый) происходят следующие действия: на двенадцатом и тринадцатом тактах для функции 1 з;(х) повторяются операции, выполненный на тактах десятом и одиннадцатом для функции Г(х), а с двенадцатого и четырнадцатого тактов для функций Г(х) и Г(х) повторяются операции, аналогичные операциям, выполняемым с восьмого такта для функции й(х) (5). На последующих тактах с шестнадцатого по двадцать третий (5), сдвадцать четвертого по тридцать первый (4), с тридцать второго по тридцать девятый (3) и с сорокового посорок седьмой (2) для Функции выполняются действия, аналогичные действиям, реализуемым на тактах с восьмого по пятнадцатый, При этом на сорок первом, сорок третьем, сорок пятом и сорок седьмом тактах блок 21завершает Формирование величиИ Е,Й, й (2) соответственно, Модулярные коды искомых величин в указанных тактах снимаются с выхода 22устройства и на этом процесс вычисления Функций в заданных точкахзаканчивается, 1278839Начиная с сорокового такта, впредлагаемом устройстве может бытьначато вычисление новых четырех зна.чений одной и той же или четырехразличных функций,Формула изобретен ияУстройство для вычисления функций в модулярном коде, содержащее сдвиговый регистр, блок памяти для хра- нения констант, регистрконстант, модульный умножитель, модульный сумматор, группу коммутаторов, счетчик по модулю, два триггера, два вспомогательньгх регистра и буферный регистр, причем вход кода задания функции устройства соединен с входом младших разрядов сдвигового регистра, выход регистра констант соединен с вхоцом первого слагаемого модульного сумматора, информационный вход первого вспомогательного ре. гистра соецинен с выходом второго вспомогательного регистра и с входом первого сомножителя модульного умно- жителя, установочный вход второго вспомогательного регистра соединен с входом аргумента устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения бьзстродействия, оно содержит счетчик, две группы мультиплексоров и блок деления на константу, причем установочный вход устройства подключен к входам обнуления сдвигоного регистра, счетчика и счетчика по модулю, а также к входам сброса первого и второго триггеров, тактовый вход устройства подключен к счетному входу второго триггера и счетному входу счетчика по модулю, выход переноса которого соединен со счетным входом счетчика и входом установки первого триггера,разрядный выход счетчика, прямойвыход второго триггера. и выходы млад.ших разрядов сдвигового регистрасоединены соответственно с разрядами адресного входа блока памяти дляхранения констант, выход которогосоединен с информационными входамикоммутаторов группы, первые и вто рые выходы которых соединены соответственно с информационным входомрегистра констант и с первыми информационными входами мультиплексоровпервой группы, выходы которых соединены с соответствующими разрядамиинформационного входа второго вспомогательного регистра, выход первоготриггера соединеп с управляющими,входами мультиплексоров первой группьз, вторые информационные зходы которых соединены с выходом блока деления на константу, выход которогоявляется выходом устройства, прямойвыход второго триггера соединен суправляющими входами коммутаторовгруппы и с управляющими входами мультиплексоров второй группы, инверсныйвыход второго триггера соединен свходом управления сдвигом сдвиговогорегистра, выход первого вспомогательного регистра. и вхоц константы устройства соединены соответственно спервыми и вторыми информационнымиФвходами мультиплексоров второй груп пы, выходы которых соединены с соответствующими разрядами вхоца второго сомножителя модульного умножителя, ззыход которого соединен с входомбуферного регистра выход которогосоединен с входом второго слагаемогомодульного сумматора, выход которогосоединен с входом блока деления на1278839 Составитель А. Клюеватилло Техред В.Кадар Коррек дактор Ильин Заказ 6839/47 ИИП д. 4/5 ая н оскв венно-полиграфическое предприятие, г. Ужгород, ул. Проектна роиз по 3035, Тираж 67 Государс елам изоб твенногоретений и35, Раушс Подписноеомитета СССоткрытий

СмотретьЗаявка

3911178, 14.06.1985

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО

КОЛЯДА АНДРЕЙ АЛЕКСЕЕВИЧ, РЕВИНСКИЙ ВИКТОР ВИКЕНТЬЕВИЧ, СЕЛЯНИНОВ МИХАИЛ ЮРЬЕВИЧ, СМИРНОВ НИКОЛАЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/544, G06F 7/72

Метки: вычисления, коде, модулярном, функций

Опубликовано: 23.12.1986

Код ссылки

<a href="https://patents.su/7-1278839-ustrojjstvo-dlya-vychisleniya-funkcijj-v-modulyarnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функций в модулярном коде</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Вычислительное устройство

Случайный патент: Пульсометр