Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

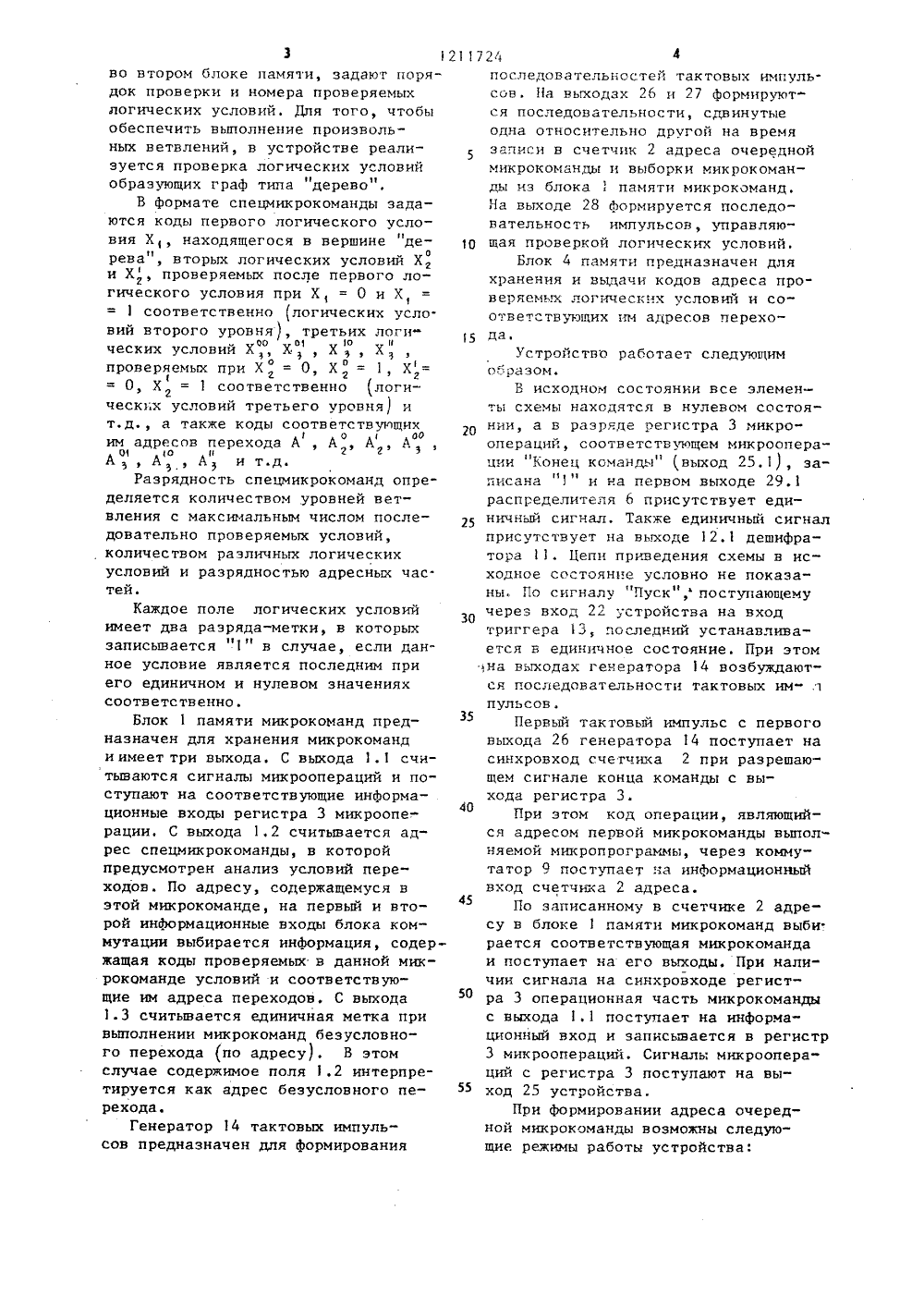

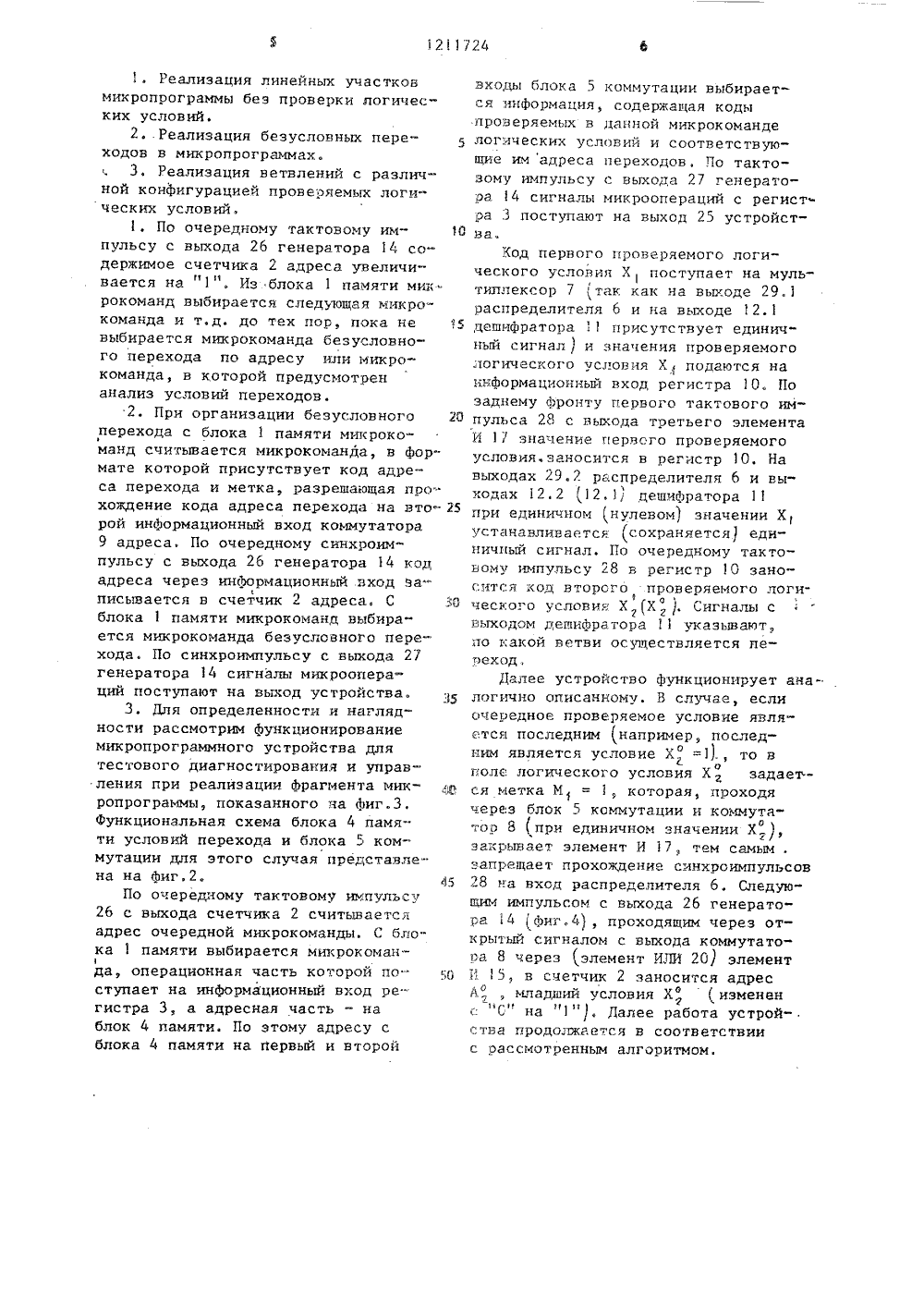

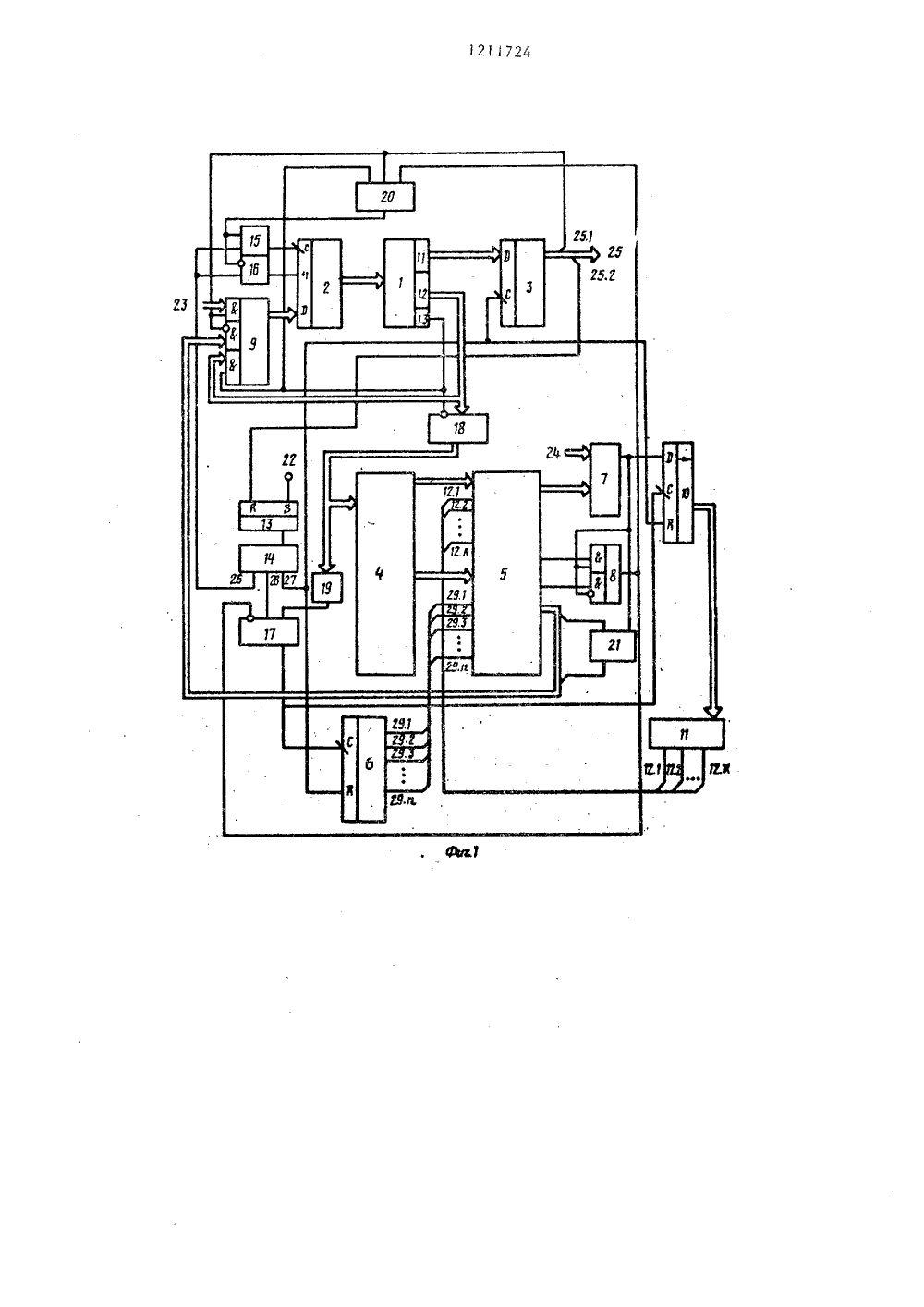

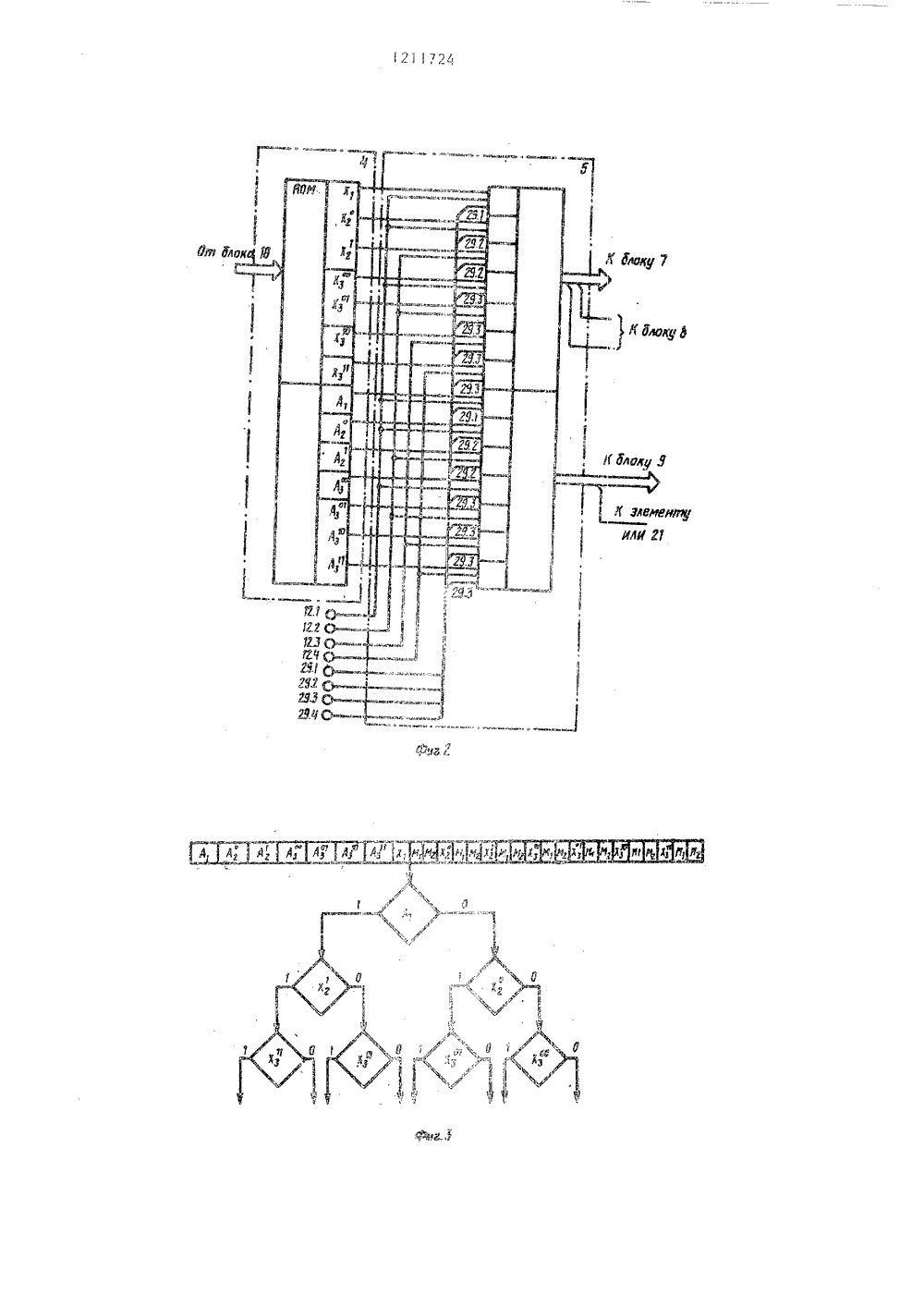

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9 2 1)4 Г ЕТЕНИЯ" тепьст ОРСК льство СССР9/22, 1981,ство СССР9/22 ь 1983 ог слощ еениярас. тор меУДАРСТВЕННЫЙ КОМИТЕТ ССС ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ИСАНИЕ ИЗ. (54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, счетчик адреса, регистр микроопераций, блок памяти микрокоманд перехода, блок коммутации и.мультиплексор, причем выход счетчика адреса подключен к адресному входу блока памяти микрокоманд, выход кода микрооперации которого подключен к информационному входу регистра микроопераций, выход которого подключен к выходу микрооперации устройства, выход адреса логического условия и выход адреса перехода блока памяти микрокоманд перехода подключены соответственно к первому и второму информационным входам блока коммутации, выход адреса логического условия которого подключен к управляющему входу мультиплексора, инфррмационный вход котор о подключен к входу логических у вий устройства, о т л и ч а ю е с я тем, что, с целью повыш быстродействия, в него введены пределитель импульсов, коммута ток, коммутатор адреса, регистр логических условий, дешифратор, логических условии, триггер пуска, генератор тактовых импульсов, три элемента И, группа элементов И и триэлемента ИЛИ, причем выходы признаков конца команды и конца работырегистра микроопераций подключенысоответственно к первому входу перво"го элемента ИЛИ и к выходу установки в "0 триггера пуска, вход установки в "1" и выход которого подключены соответственно к входу пускаустройства и к входу запуска генератора тактовых импульсов, первый,второй и третий выходы которого подключены соответственно к первому входу первого элемента И, синхровходу регистра микроопераций и к первому входу второго элемента И, вто"рой, третий входы и выход которогоподключены соответственно к выходукоммутатора меток, выходу второгоэлемента ИЛИ и к синхровходу регистра логических условий, информационный вход, вход установки в "0" и выход которого подключены соответственно к выходу мультиплексора, второ"му выходу генератора тактовых импуль"сов и к входу дешифратора логических ьусловий, выход которого подключен кпервому управляющему входу блока коммутации, второй управляющий вход, выходы первого и второго признаковокончания ветвления и выход адресаперехода которого подключены соответственно к выходу распределителяимпульсов, первому, второму информационным входам коммутатора меток ик первому информационному входу коммутатора адреса, второй, третий.информационные входы, первый, второйуправляющие входы и выход которогоподключены соответственно к входукода операции устройства, выходу ад"реса следующей микрокоманды блокапамяти микрокоманд,зыходу признакабезусловного перехода блока памятимикрокоманд, первому входу первогоэлемента ИЛИ и к информационномувходу счетчика адреса, синхрозход ивход прибавления "1" которого поцклюцены к выходам соответственно первого и третьего элементов И, первый ивторой входы первого элемента Исоединены соответственно а первыми вторым входами третьего элемента И, нторой вход которого подключенк выходу первого элемента ИЛИ, второй и третий входы которого подключены соответственно к первому управляющему входу коммутатора адреса ик выходу коммутатора меток, управ-ляющий вход которого подключен к вы ходу мульплексора и к первому вхо"ду третьего элемента ИЛИ, второйвход и выход которого подключенысоответственно к ньгходу модифицируемого разряда адреса перехода блокакоммутации и к первому информационному входу коммутатора адреса, третий информационный вход которогоподключен к первым входам элементон И группы, второй вход и выходыкоторых подключены соответственнок первому управляющему входу коммутатора адреса и к входам второгоэлемента ИЛИ, второй выход генератора тактовых импульсон подключен кзхопу чстанонки з 0" распреде.лителя импульсов, синхронход которого подключен к выходу нторого элемснта И, выходы элементон И группызбьединены и годключены к адресномувходу блока памяти мнкрокоманд перехода эИзобретение относится к автоматике и вычислительной технике и может быть использовано н устройствах упранления и диагностирования дискретных объектов.Целью изобретения является повышение быстродействия.На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока памяти условий 1 О и адресов перехода и блока коммутации; на фиг. 3 - фрагмент микропрограммы; на фиг,4ннеменная диаграмма работы устройства.Устройство содержит блок 1 памяти 15 микрокоманд с выходом 1.1 кода микро. операций, выходом 1.2 адреса и ныходом ,1,3 метки, счетчик 2 адреса регистр 3 микроопераций, блок 4 памяти микрокоманд перехода, блок 5 20 коммутации, распределитель 6 импульсов, мульплексор 7, коммутатор 8 меток, коммутатор 9 адреса, регистр 10 логических условий, дешифратор 11 логических условий 12,1 - 12,г - 25 группа выходов дешифратора), триггер 13 пуска, генератор 14 тактовых импульсов, элементы И 15, 16, 17, груп па ,8 элементов И первый 19, второй 20 и третий 21 элементы ИЛИ, входы г;уска 22, кода операции 23, логических условий 24,устройства, выход кода мнкрооперации 25 устройства, Кроме того, на хеме обозначены выходы 25.1 и 25.2 соответственно кон ца команды и конца работы регистра микроопераций соответственно первый 26 второй 27, третий 28 выходы генератора 14 тактовых импульсов и соответственно первый 29 - и -й 29 ви(ходь, распределителя 6 импульсов,Для реализации ветвлений с.произвольной топологией н устройстве обес печивается возможность проверки логических условий из множестна заданных в любой последовательности, Предлагаемое устройство содержит дна блока памяти. В первом блоке хранятся мнкрокоманды, содержащие поле микроогераций, адресное поле и поле метки, В зависимости от значения метки н адресном поле задается либо адрес безусловного перехода, либо адрес спецмикрокоманды при необходимости ныполнения ветвле ния, Спецмикрокоманды, хранимые3 2 во втором блоке памяти, задают порядок проверки и номера проверяемых логических условий. Для того, чтобы обеспечить выполнение произвольных ветвлений, в устройстве реализуется проверка логических условий образующих граф типа "дерево".В формате спецмикрокоманды задаются коды первого логического условия Х, находящегося в вершине де 1 о рева, вторых логических условий Х, и Х, проверяемых после первого логического условия при Х, = О и Х,1 соответственно (логических усло. вий второго уровня, третьих логиоо о о и ческих условий Х Х , ХХпроверяем при Хо = О, Хо = 1, Хг= = О, Х= 1 соответственно (логических условий третьего уровня) и т.д., а также коды соответствующихооо им адресов перехода А, А, ААО оА, А, А ит.д.Разрядность спецмикрокоманд определяется количеством уровней ветвления с максимальным числом последовательно проверяемых условий, количеством различных логических условий и разрядностью адресных час. тей.Каждое поле логических условий имеет два разряда-метки, в которых записывается "1 " в случае, если данное условие является последним при его единичном и нулевом значениях соответственно.Блок 1 памяти микрокоманд предназначен для хранения микрокоманд и имеет три выхода. С выхода 1.1 считываются сигналы микроопераций и поступают на соответствующие информационные входы регистра 3 микроопе-. рации. С выхода 1.2 считывается адрес спецмикрокоманды, в которой предусмотрен анализ условий переходов. По адресу, содержащемуся в этой микрокоманде, на первый и второй информационные входы блока коммутации выбирается информация, содержащая коды проверяемых в данной микрокоманде условий и соответствующие им адреса переходов. С выхода 1.3 считывается единичная метка при выполнении микрокоманд безусловного перехода (по адресу). В этом случае содержимое поля 1.2 интерпретируется как адрес безусловного перехода.Генератор 14 тактовых импульсов предназначен для формирования11724 4 5 О 5 20 25 30 35 40 45 50 55 последовательностей тактовых импульсов. На выходах 26 и 27 формируются последовательности, сдвинутые одна относительно другой на время записи в счетчик 2 адреса очередной микрокоманды и выборки микрокоманды из блокапамяти микрокаманд, На выходе 28 формируется последовательность импульсов, управляющая проверкой логических условий.Блок 4 памяти предназначен для хранения и выдачи кодов адреса проверяемых логических условий и соответствующих им адресов перехода.Устройства работает следующим образам.В исходном состоянии все элементь схемы находятся в нулевом состоянии, а в разряде регистра 3 микро- операций, соответствующем микроаперацчи "Конец команды" (выход 25.1) записана и на первом выходе 29.1 распределителя 6 присутствует единичный сигнал. Также единичный сигнал присутствует на выходе 12.1 дешифратора 1. Цепи приведения схемы в исходное состояние условно не показаны. По сигналу "Пуск",поступающему через вход 22 устройства на вход триггера 3, последний устанавливается в единичное состояние. При этом,на выходах генератора 14 возбуждаются последовательности тактовых им-,япульсон.Первый тактовый ишульс с первого выхода 26 генератора 14 поступает на синхровход счетчика 2 при разрешающем сигнале конца команды с выхода регистра 3.При этом код операции, являющийся адресом первой микрокоманды выполняемой микропрограммы, через коммутатор 9 поступает на информационный вход счетчика 2 адреса.По записанному в счетчике 2 адресу в блоке 1 памяти микрокоманд выби. рается соответствующая микрокоманда и поступает на его выходы. При кали" чии сигнала на синхровходе регистра 3 операционная часть микрокоманды с выхода 1.1 поступает на информационный вход и записывается в регистр 3 микроопераций. Сигналы микроопераций с регистра 3 поступают на выход 25 устройства.При формировании адреса очередной микрокоманды возможны следующие режимы работы устройства:1. Реализация линейных участков микропрограммы беэ проверки логических условии,2 Реализация безусловных переходов в микропрограммах.3, Реализация ветвлений с различной конфигурацией проверяемых логических условий.1. По очередному тактовому им О пульсу с выхода 26 генератора 14 содержимое счетчика 2 адреса увеличивается на "1", Из блока 1 памяти микрокоманд выбирается следующая микро- команда и т.д. до тех порр пока не 15 выбирается микрокоманда безусловного перехода по адресу или микро- команда, в которой предусмотрЕн анализ условий переходов.2. При органиэации безусловного 2 О перехода с блока 1 памяти микрокоманд считывается микрокоманда, в фор" мате которой присутствует код адреса перехода и метка, разрешающая прохождение кода адреса перехода на вто рой информационный вход коммутатора 9 адреса. По очередному синхроимпульсу с выхода 26 генератора 14 код адреса через информационньпл вход эа-писывается в счетчик 2 адреса. С блока 1 памяти микрокоманц выбирается микрокоманда безусловного перехода, По синхроимпульсу с выхода 27 генератора 1 ч сигналы микроопераций поступают на выход устройства.3. Для определенности и наглядности рассмотрим функционирование микропрограммного устройства для тестового диагностирования и управления при реализации Фрагмента микропрограммы, показанного на фиг.3. Функциональная схема блока ч памяти условий перехода и блока 5 ком-= мутации для этого случая представлена на фиг,2. ЯПо очередному тактовому импульсу 26 с выхода счетчика 2 считывается адрес очередной микрокоманды. С блока 1 памяти выбирается микрокоманда, операционная часть которой пав . ступает на информационный вход регистра 3, а адресная часть - на блок 4 памяти. По этому адресу с блока ч памяти на первый и второй входы блока 5 коммутации выбирается информация, содержащая кодыпроверяемых в данной микрокоманделогглческих условий и соответствующие им адреса переходов. По тактодому импульсу с выхода 27 генератора 1 ч сигналы микроопераций с регистра 3 поступают на выход 25 устройства.1 Хоц первого проверяемого логического условия Х 1 поступает на мультиплексор 7 (так как на выходе 29.1распределителя 6 и на выходе 12.1дешифратора .1 присутствует единичный сигнал ) и значения проверяемогологического условия Х 1 подаются наинформационный вход регистра 10. Позаднему фронту первого тактового импульса 28 с выхода третьего элементаИ 17 значение первсго проверяемогоусловия, заносится в регистр 10. Навыходах 29,2 распределителя б и выходах 12.2 (12.1 цешифратора 11при единичном (нулевом 1 значении Хустанавливается (сохраняется единичный сигнал. По очередному тактовому импульсу 28 в регистр 10 заносится код второго проверяемого логического условия Х (Х ,. Сигналы свыходом дешифратора 11 указываютпо какой ветви осуществляется переход,Далее устройство функционирует аналогично Описанному. В случае, еслиочередное проверяемое условие является последним (например, последним является условие Хо =1., то вполе логического условия Х задается метка И = 1, которая, проходячерез блок 5 коммутации и коммутатор 8 при единичном значении Хзакрывает элемент И 7, тем самым,запрещает прохождение синхроимпульсов28 на вход распределителя б. Следующил импульсом с выхода 26 генератора 14 (фиг.4), проходящим через открытый сигналом с выхода коммутатора 8 через (элемент ИЛИ 20 элементИ 15, в счетчик 2 заносится адресЛ , младший условия Х ,измененс. "С" на "1", Далее работа устройства продолжается в соответствиис рассмотренным алгоритмом.

СмотретьЗаявка

3768821, 11.07.1984

ПРЕДПРИЯТИЕ ПЯ А-7160

СЫЧЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, МАЛАХОВ ВИКТОР АЛЕКСАНДРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/7-1211724-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для управления системой обегающего контроля

Следующий патент: Микропрограммное устройство управления с контролем

Случайный патент: Устройство для измерения изменения частоты