Устройство для умножения чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1481748

Авторы: Жалковский, Шостак, Шпаков

Текст

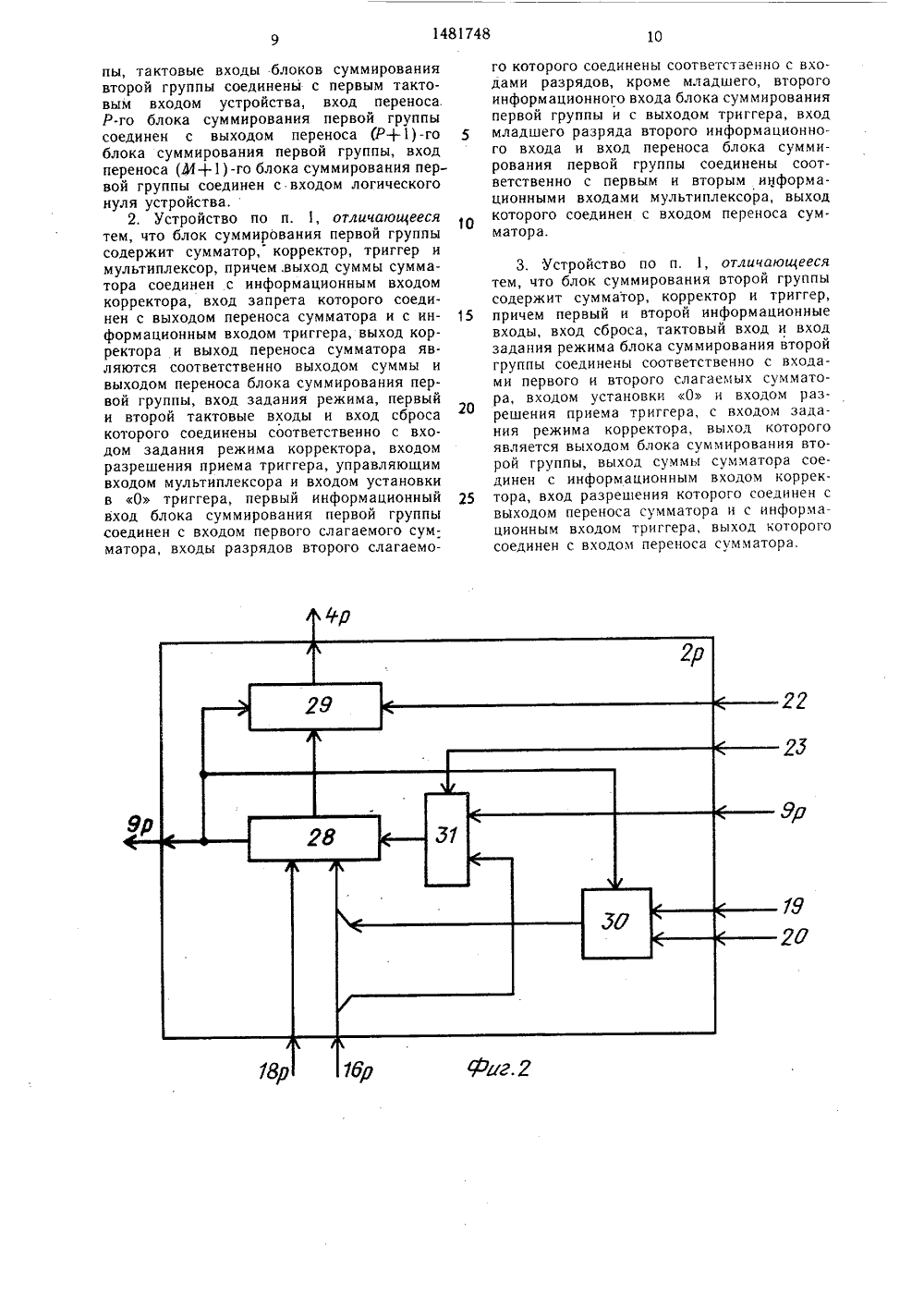

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 4 6 06 Е 7 52 ГОСУДАРСТВЕННЫЙ КОМИТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИ Е о(,я 19 й, А(ММ 56) Авторское свидетельство СССР0 229758, кл. 6 06 Р 7/52, 1982.Авторское свидетельство СССР0 842800, кл. С 06 Р 7/52, 1979.54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯИСЕЛ ЯО 1481748 А 1(57) Изобретение относится к вычислительной технике и может быть применено для быстрого выполнения операции умножения двоичных и десятичных чисел, Особенно эффективно его использование при применении БИС и СБИС. Целью изобретения является сокращение аппаратурных затрат за счет новой организации связей. Устройство для умножения чисел содержит группу блоков 1 умножения, группы блоков 2, 3 суммирования, группы буферных регистров 5 - 7 и группу регистров 8 произведения. 2 з. п. ф-лы, 5 ил.5 10 15 20 50 55 Изобретение относится к области вы. числительной техники, может быть использовано для умножения двоичных и десятичных чисел и может найти примененение в качестве основы при разработке быстродействующих арифметических устройств универсальных ЭВМ, работающих как с двоичными, так и с десятичными числами.Целью изобретения является сокращение аппаратурных затрат.На фиг. 1 показана структурная схема устройства для умножения чисел; на фиг, 2 - структурная схема блока суммирования первой группы; на фиг. 3 - структурная схема блока суммирования второй группы; на фиг. 4 и 5 - потактные временные диаграммы выполнения соответственно двоичного и десятичного умножения.Устройство для умножения чисел содержит (фиг. 1) группу блоков 1 - 1 умножения, первую группу блоков 2 - 2 м+ суммирования, вторую группу блоков 3 - Зм суммирования, выходы 4 - 4суммы соответственно блоков 2 - 2+ суммирования первой группы, первую, вторую и третью группы буферных регистров 5, - 5 6 - 6 и 7 - 7соответственно, группу регистров 8 - 8 + произведения, входы 9 - 9 переноса соответственно блоков 2 - 2 суммирования первой группы, вход 10 множителя устройства, группу входов 11 - 11, цифр множимого устройства, вход 12 зна чения коррекции устройства, входы 13 и 14 соответственно первой и второй констант устройства, вход 15 логического нуля устройства, выходы 16 - 1 Ь, соответственно регистров 7 - 7 м+третьей группы, выход 17 младшей части произведения устройства, 35 группу выходов 18 - 18 цифр старшей части произведения устройства, вход 19 начальной установки устройства, первый тактовый вход 20 устройства, выходы 21 - 2 м+ блоков 3 - 3 + суммирования40 второй группы соответственно, вход 22 задания режима устройства, второй тактовый вход 23 устройства, выходы 24 - 24 м, старших частей произведений и выходы 25 - 25. младших частей произведений блоков 1 - 1, умножения, группы выходов 26 - 26 45 буферных регистров 5 - 5 первой группы соответственно, выходы 27 - 27; буферных регистров 6 - 6 второй группы соответственно.Блок 2 суммирования первой группы содержит (фиг. 2) сумматор 28, корректор 29, триггер 30 и мультиплексор 31.Блок 3 суммирования второй группы содержит (фиг. 3) сумматор 32, корректор 33 и триггер 34.Рассмотрим функциональное назначение и реализацию основных блоков и узлов устройства. Каждый из блоков 1 - 1 умноженияосуществляет умножение соответствующей тетрады разрядов множимого на тетраду разрядов множителя, В зависимости от значения потенциала, поступающего с входа 22 ,на вход задания режима блока 1 умножения на его выходе 24 старшей и выходе 25 младшей части произведения появляется результат умножения либо в двоичном, либо в двоично-десятичном коде. Потенциал логической единицы на входе 22 обеспечивает работу устройства в десятичной системе счисления, а потенциал логического нуля - его работу в двоичной системе счисления. Блоки 1, - 1. умножения целесообразно реализовать в виде ППЗУ, В этом случае младшая или старшая часть двоично-десятичного произведения на выходах блока умножения могут формироваться уже скорректированными на +6 без каких-либо дополнительных аппаратурных затрат,Блоки 2 - 2;+ суммирования первой группы предназначены для формирования промежуточных и окончательного результатов при выполнении операции двоичного и десятичного умножения, причем все они работают идентичным образом. Рассмотрим функциональное назначение узлов блока 2 р (р=2, 3, , м). В нем (фиг. 2) на сума- торе 28 осуществляется суммирование значений двух тетрад, поступающих с выхода 18, регистра 8 р- произведения и с выхода 16 буферного регистра 7 третьей группы, причем значение выходного переноса сумматора 28 запоминается в триггере 30, которое в следующем такте подается с выхода триггера 30 на вход младшего разряда второго входа сумматора 28, Значение входного переноса сумматора 28 поступает через мультиплексор 31 либо с выхода младшего разряда буферного регистра 7 р третьей группы, либо с выхода переноса сумматора 28 более старшего (р+1) -го блока суммирования первой группы. Коммутация выхода триггера 30 с входом младшего разряда второго входа сумматора 28 обеспечивает возможность быстрого приведения переносов в конце выполнения операции умножения. В этом случае сквозной перенос в блоках 2 - 2 м+ суммирования первой группы распространяется через мультиплексоры 31 и одновременно в каждом блоке на сумматоре 28 подсуммируется содержимое триггера 30. Настройка же мультиплексоров 31 блоков суммирования первой группы на передачу информации через их вторые входы осуществляется потенциалом логической единицы с входа 23 устройства.При выполнении в устройстве двоичного умножения корректор 29 настраивается потенциалом логического нуля с входа 22 на передачу информации транзитом. При десятичном умножении с входа 22 на управляющий вход задания режима коррек 148174810 20 25 30 35 40 50 55 тора 29 подается потенциал логической единицы, что обеспечивает коррекцию -6 в случае отсутствия выходного переноса сум-. матора 28. Значение же выходного переноса сумматора 28, равное логической единице, поступая на вход запрета коррекции корректора 29, обеспечивает передачу через него информации без изменения. Самый старший 2 и самый младший 21+ блоки суммирования первой группы построены точно так же, как и описанные выше блоки 22 - 2, причем с входа 12 устройства в блок 2 при двоичном умножении, чисел в дополнительных кодах может вводиться коррекция либо подсуммироваться в процессе умножения двух чисел третье число к получающемуся произведению.Блоки 3 - Э + суммирования второй группы предназначены для предварительного суммирования старших и младших частей произведений, вырабатываемых блоками 1 - 1. умножения.На первый вход сумматора 32 блока Зр суммирования второй группы подается содержимое р-го буферного регистра 5 первой группы, а на второй вход - значение содержимого (р - 1) -го буферного регистра 6 второй группы. После выполнения очередного такта, значение результата суммирования на сумматоре 32 запоминается в буферном регистре 7 третьей группы, а значение выходного переноса сумматора 32 - в триггере 34.При выполнении в устройстве двоичного, умножения корректор 33 настраивается потенциалом логического нуля с входа 22 на передачу информации транзитом. При десятичном умножении с входа 22 на управляющий вход корректора 33 поступает потенциал логической единицы, что обеспечивает коррекцию +6 при наличии единичного значения выходного переноса сумматора 32. В отсутствие переноса из сумматора 32 информация через корректор 33 передается без изменения.Самый старший 3 и самый младший 3+ блоки суммирования второй группы построены так же, как и блоки 3 - 3, но подключены они в устройстве несколько иначе. Если при десятичном умножения старшие тетрады произведений на выходах блоков 1 - 1. умножения формируются уже скорректированными на +6, то на вход 13 первой константы устройства подается код 0000, а на вход 14 второй константы - код 0110. Если же младшие тетрады произведений на выходах блоков 1 - 1. умножения формируются уже скорректированными на +6, то на вход 13 первой константы подается код 0110, а на вход 14 второй константы - код 0000. При двоичном умножении на оба входа 13 и 14 подается код 0000. Устройство работает следуь: ци:; с;бр,:.О.; (фиг. 4 и 5).По сигналу У 19 происходит обнуление регистров 7 - 7. +, 8 - 8,+ и триггеров 30 и 34 блоков суммирования, сигнал У 2 С разрешает запись по синхроимпульсу инфор. мации в регистры 5 - 5, 6 - 6, 7 - 7;+ 8 - 8. , а также в триггеры ЗО и 34 блоков суммирования, сигнал У 22 ооеспечивает функционирование блоков 1, -умножения в десятичной системе счисления и настройку корректоров 29 и 33 блоков суммирования на режим коррекции, ю сигналу У 23 мультиплексора 31 блоки сум.ирования первой группы настраиваются ня передачу информации с их вторых входов, на которые поступают значения выходных переносов из сумматоров 28 соседних более младших блоков с.мхЯовання пег;с 1." группы.Рассмотрим выпс 1 лнсчс;. Ня чиого жения (фиг. 4). Перед началом онепя. ции ня Входах1- -устаяв,:1 сстгс". значения множимого. на Входе О множителя уст 110 йстВя устянав.1 Влстся 31 с.с самой младшей тетрады множителя.В первом такте двои;ноге умнс 1 х,сня в блоках 11 - 1, я",ая младшая тс )1;1. Да МНОжнтЕЛЯ Пс РЕМНОжЯЕтСЯ НЯ С 10: - ветствующие тетрадь м нож и м ого., 1 воич и ьк результаты этих тетрадных умножений зяи;: - сываются в буфер - .ые регистры 5, 5, и 6 - 6 по сигналу разреше:; У 20. Одновременно происходя г об нуле;,.с ре- гистрОВ 7 - lн+1, 8 - -8 м+; и трггс)10 30 и ЗЯ блоков суммирования (с: ;я.; У 9). а также подача на входО устроЯства следующей тетрады множителя.ВО Втором такт. .".нОИся ., 10 чсс;- дят перемножение очсредной Вторс 1,) Сс- рады множителя на тетрадь: мюжимого одноВременно с этим прсдвяритсьнОС с",м.нрОВяние предыдущих тстрядных 11 роиззсдсний в блоках 3 - 3, суммирования второй группы. В конце второго такта с разрешения сигнала У 20 в регистрах 5- -5, 6 - 6, 7 - 7 н+, 8 - 8 и триггерах 30 и 34 блоков суммирования фиксируется промежуточная информация, я на входе )с множителя устройства появляется значение следующей (третьей) тетряды множителя.Аналогичным образом устройство фу.;- ционирует и В других тактах. В каждо такте с выхода 17 устройства, начиная с четвертого такта, считывается значение очсредной тетрады младшей части результата.После выполнения последнего м-го такта собственно умножения в буферных регистрах 5 - 5 и 6 - 6 запоминаются значе. ния тетрадных произведений последней (самой старшей) тетрады множителя наВсе тетрады множимого.При выполнении (м+1) -го такта происходит предварительное суммирование значений содержимогю буферных регистров 5 5 н10 25 ЗО 40 5 О формула изобретения и 61 в 6 в блоках 3 - 3 суммирования второй группы, а также суммирование содержимого регистров 8 - 8 и 7 - 7,. в блоках 2 - 2+1 суммирования первой группы. С входа 10 множителя устройства при этом на все входы множителя блоков 1 - 1 умножения подается нулевая тетрада. В конце такта образуемые на выходах блоков 11 - 1 нулевые произведения запоминаются в буферных регистрах 5 - 5 и 61 - 6, а в регистрах 71 - 7 и+1 и 81 - 8 н+1. некоторая промежуточная информация.После выполнения (м+2)-го и (м+3)-го тактов завершается вывод информации из блоков 31 - Зм+ и буферных регистров 71 - 7 мнПри выполнении (м+4)-го такта сигнал У 23 настраивает мультиплексоры 31 блоков 21 - 2 н суммирования первой группы на передачу информации через их вторые входы, тем самым выходы переноса сумматоров 28 оказываются соединенными с входами переноса сумматоров 28 соседних старших блоков суммирования первой группы. В результате этого значения содержимого триггеров 30 подсуммируются к сумме содержимых соответствующих регистров 7- 7 и 81 - 8,и двухрядный код произведения преобразуется к однорядному.Поскольку при приведении двухрядного кода к однорядному перенос распространяется через все блоки 21 - 2 и+, суммирования, то длительности одного такта работы устройства не хватает для завершения такого приведения, Поэтому сигнал У 23 поддерживается в течение двух (как это предполагается на фиг. 4 и 5) или более тактов.После выполнения (м+4) -го и (м+5) -го тактов в регистрах 8 - 8 произведения будет находиться старшая часть окончательного произведения в однорядном коде. Младшая же часть произведения уже введена через выход 17 устройства во время выполнения предыдущйх тактов.Десятичное умножение выполняется в основном аналогично двоичному. На фиг. 5 приведена диаграмма выполнения десятичного умножения в предположении, что количество десятичных разрядов в операндах равно м. Отличие от двоичного умножения состоит в том, что в тактах с первого по (м+5)-й присутствует дополнительный сигнал У 22, который настраивает блоки 11 в 1 на умножение в десятичной системе счисления, а корректоры 29 и 33 блоков суммирования - на режим коррекциии. 1. Устройство для ум ножения чисел, содержащее группу блоков умножения, две группы блоков суммирования, группу регистров произведения и три группы буферных регистров, причем вход множителя устройства соединен с входами множителя блоков умножения группы, входы множимого которых соединены с соответствующими входами цифр множимого группы устройства, вход задания режима которого соединен с входами задания режима блоков умножения группы, с входами задания режима блоков суммирования первой и второй групп, выходы старших и младших частей произведений блоков умножения группы соединены с информационными входами соответствующих буферных регистров первой и второй групп, выходы буферных регистров первой группы соединены с первыми информационными входами соответствующих блоков суммирования второй группы, выход Р-го (Р= 1 - М, М=п 4, и - разрядность сомножителей) буферного регистра второй группы соединен с вторым информационным входом (Р+1) -го блока суммирования второй группы, выходы блоков суммирования второй группы соединены с информационными входами соответствующих буферных регистров третьей группы, входы установки в О которых соединены с входом начальной установки устройства, выходы суммы блоков суммирования первой группы соединены с информационными входами соответствующих регистров произведения группы, выход Р-го регистра произведения группы соединен с первым информационным входом (Р+1)-го блока суммирования первой группы и является выходом Р-й цифры старшей части произведения устройства, выход младшей части произведения которого соединен с выходом (М+1) -го регистра произведения группы, вход начальной установки устройства соединен с входами установки в О регистров произведения группы, входы разрешения приема которых объединены с входами разрешения приема буферных регистров первой, второй и третьей групп и соединены с первым тактовым входом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, входы первой и второй констант устройства соединены соответственно с вторым информационным входом первого и .с первым информационным входом (М+1) -го блоков суммирования второй группы, вход значения коррекции устройства соединен с первь 1 м информационным входом первого блока суммирования первой группы, выходы буферных регистров третьей группь 1 соединены с вторыми информационными входами соответствующих блоков суммирования первой группы, входы сброса которых объединены с входами сброса блоков суммирования второй группы и соединены с входом начальной установки устройства, первый и второй тактовые входы которого соединены соответственно с первыми и вторыми тактовыми входами блоков суммирования первой группы, тактовые входы блоков суммирования второй группы соединены с первым тактовым входом устройства, вход переноса. Р-го блока суммирования первой группы соединен с выходом переноса Р+1) -го 5 блока суммирования первой группы, вход переноса (Я+1) -го блока суммирования первой группы соединен с входом логического нуля устройства,2. Устройство по п. 1, отличающееся тем, что блок суммирования первой группы содержит сумматор, корректор, триггер и мультиплексор, причем, выход суммы сумматора соединен с информационным входом корректора, вход запрета которого соединен с выходом переноса сумматора и с ин формационным входом триггера, выход корректора и выход переноса сумматора являются соответственно выходом суммы и выходом переноса блока суммирования первой группы, вход задания режима, первый и второй тактовые входы и вход сброса которого соединены соответственно с входом задания режима корректора, входом разрешения приема триггера, управляющим входом мультиплексора и входом установки в О триггера, первый информационный 25 вход блока суммирования первой группы соединен с входом первого слагаемого сумматора, входы разрядов второго слагаемого которого соединены соответственно с входами разрядов, кроме младшего, второго информационного входа блока суммирования первой группы и с выходом триггера, вход младшего разряда второго информационного входа и вход переноса блока суммирования первой группы соединены соответственно с первым и вторым информационными входами мультиплексора, выход которого соединен с входом переноса сумматора. 3. Устройство по п. 1, отличающееся тем, что блок суммирования второй группы содержит сумматор, корректор и триггер, причем первый и второй информационные входы, вход сброса, тактовый вход и вход задания режима блока суммирования второй группы соединены соответственно с входами первого и второго слагаемых сумматора, входом установки О н входом разрешения приема триггера, с входом задания режима корректора, выход которого является выходом блока суммирования второй группы, выход суммы сумматора соединен с информационным входом корректора, вход разрешения которого соединен с выходом переноса сумматора и с информационным входом триггера, выход которого соединен с входом переноса сумматора.осударственного13035, М ственно-издател роиз Редактор Л. ГратиЗаказ 2690/49НИИПИ Г Составитель АТехред И. Верес Тираж 669комитета по изобрете осква, Ж - 35, Рауш ьский комбинат Г 1 атен КлюевКоррекПодписиям и открытикая наб., р,.т, г. Ужгород ор А. Обручарноеям при ГКНТ ССС4/5ул. Гагарина, 1 О 1

СмотретьЗаявка

4318783, 20.10.1987

ПРЕДПРИЯТИЕ ПЯ М-5339

ЖАЛКОВСКИЙ АНДРЕЙ АНТОНОВИЧ, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ, ШПАКОВ ЛЕОНАРД ОРЕСТОВИЧ

МПК / Метки

МПК: G06F 7/52

Опубликовано: 23.05.1989

Код ссылки

<a href="https://patents.su/6-1481748-ustrojjstvo-dlya-umnozheniya-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел</a>

Предыдущий патент: Устройство для умножения двоичных чисел

Следующий патент: Устройство для умножения

Случайный патент: Автомат для сборки шариковых авторучек