Устройство для умножения чисел по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

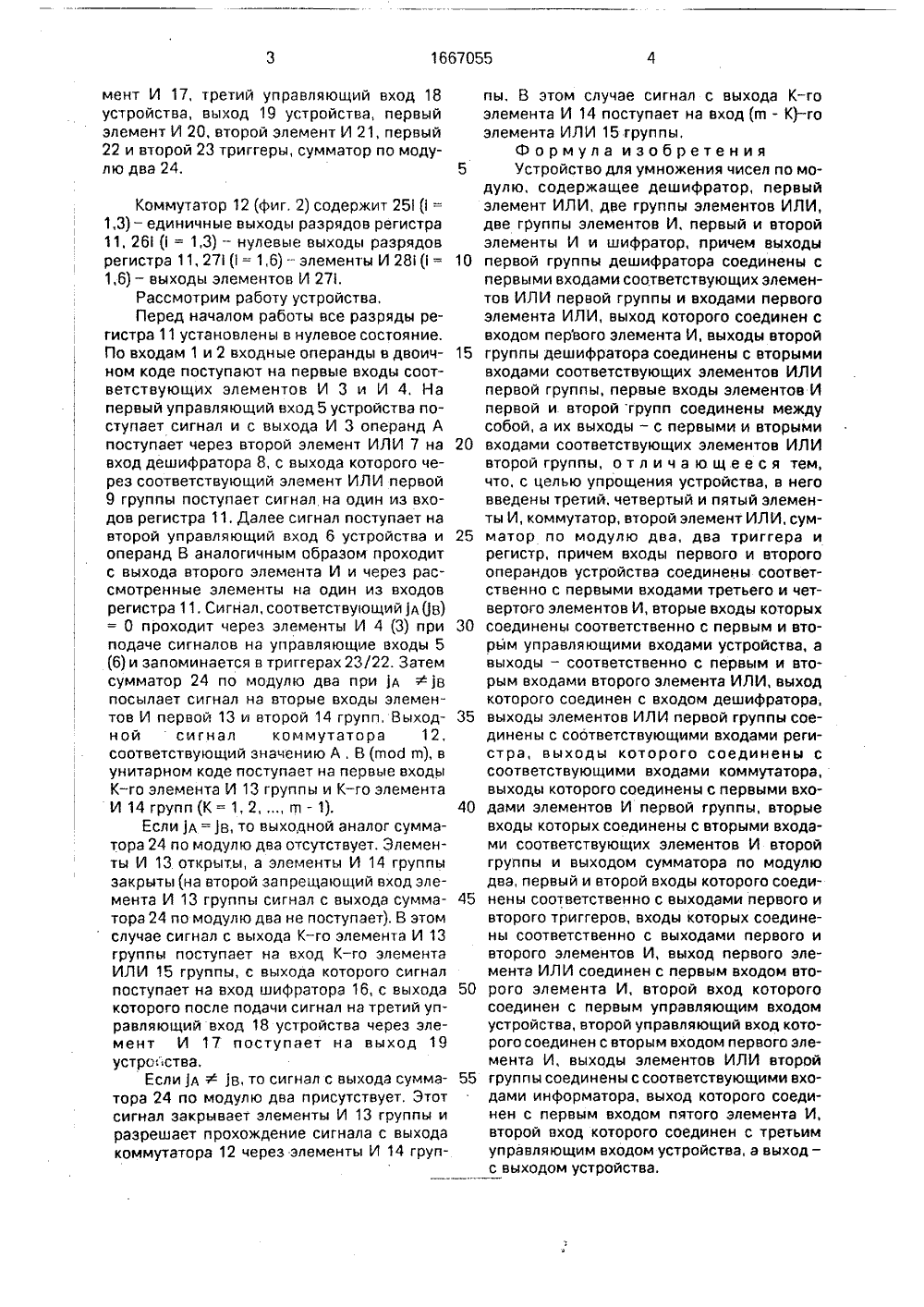

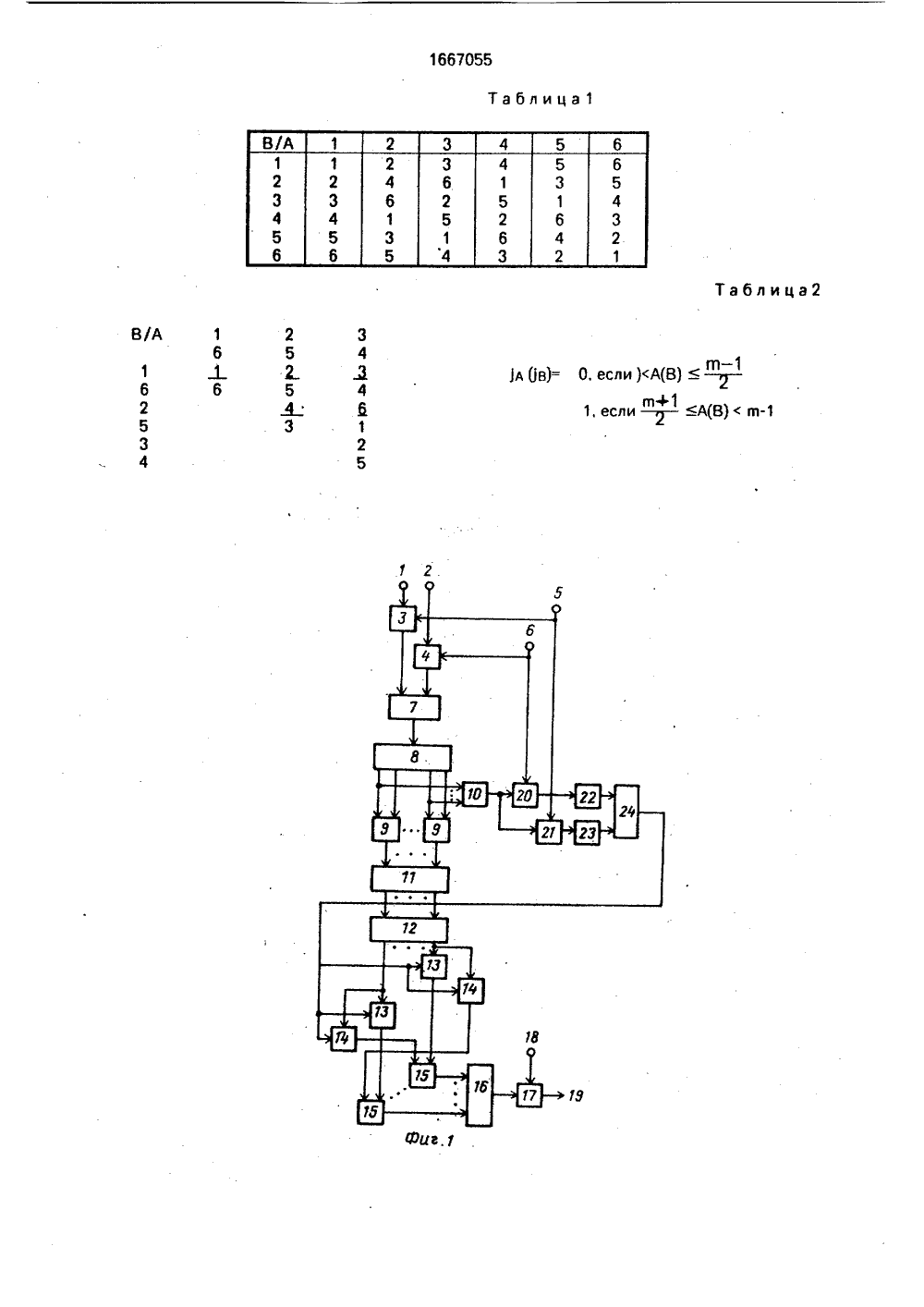

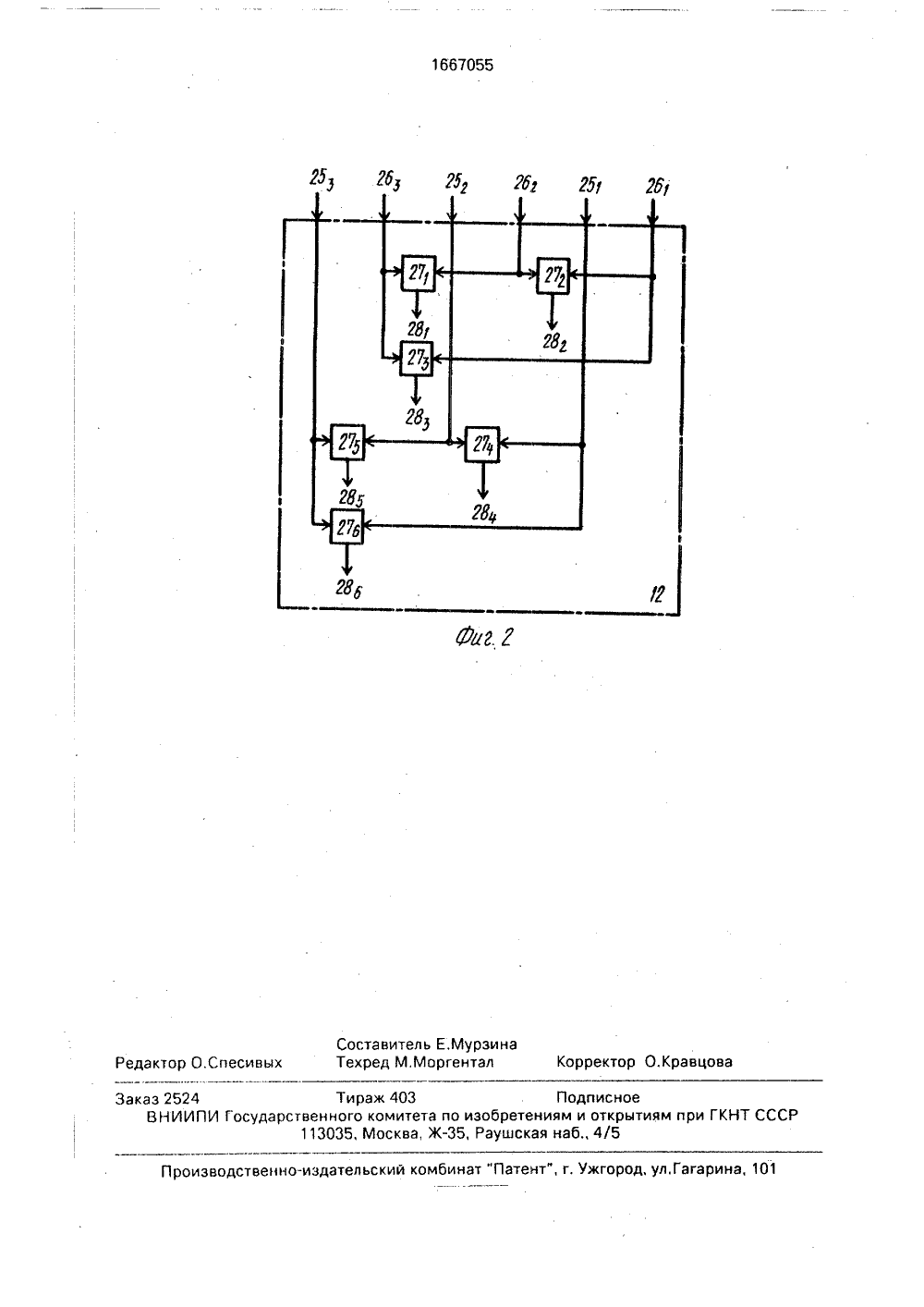

)5 6 06 Р 7/49, 7/72 ИСАНИЕ ИЗОБРЕТЕНИ ощение устройГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССР М 1126950, кл. 6 06 Г 7/49, 1983.Авторское свидетельство СССР М 1187161, кл. О 06 Р 7/49, 1984.(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов. Цель изобретения - упрощение устройства. Новым в устройстве,Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов.Цель изобретения - упр ства.Сущность изобретения состоит в преобразовании первого и второго операнда из двоичного в унитарный код при помощи одного дешифратора с данного полученного результата (с учетом симметрии арифметической таблицы) в регистр и последующего преобразования состояния регистра в результат операции А - В (вод гп) (А, В - операнды, е - модуль) с использованием коммутатора. Рассмотрим табл. 1 операции модульного умножения для т = 7..,Ж 1667055 А 1 содержащем дешифратор 8, две группы элементов ИЛИ 9, 15, элемент ИЛИ 10, два элемента И 20, 21, две группы элементов И 13, 14 и шифратор 16, является введение трех элементов И 3, 4, 17, элемента ИЛИ 7, регистра 11 и коммутатора 12, что дало возможность исключить второй дешифратор и существенно уменьшить количество элементов И в используемом коммутаторе. Сущность изобретения состоит в преобразовании первого и второго операндов из двоичного в унитарный код при помощи одного дешифратора 8 с записью полученного результата (с учетом симметрии арифметической таблицы) в регистр 11 и последующем преобразовании состояния регистра 11 в результат операции А х В (гпод гп) (А, В - операнды, гп - модуль). с использованием коммутатора 12. 2 ил. Отметим, что ввиду симметрии табл. 1 можно изобразить на табл. 2, где в клетках над чертой указаны числа, соответствующие результату операции модульного умножения при А =)В, а под чертой - при)А )В,На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема коммутатора (для п 1 = 7).Устройство(фиг. 1) содержит вход 1 первого операнда устройства, вход 2 второго операнда устройства, третий 3 и четвертый 4 элементы И, первый 5 и второй 6 управляющие входы устройства, второй элемент ИЛИ 7, дешифратор 8, первую группу элементов ИЛИ. первый элемент ИЛИ 10, регистр 11, коммутатор 12, первую 13 и вторую 14 группы элементов И, вторую 15 группу элементов ИЛИ, шифратор 16, пятый эле10 15 20 30 35 40 45 50 55 мент И 17, третий управляющий вход 18 устройства, выход 19 устройства, первый элемент И 20, второй элемент И 21, первый 22 и второй 23 триггеры, сумматор по модулю два 24. Коммутатор 12 (фиг. 2) содержит 25 ( = 1,3) - единичные выходы разрядов регистра 11, 26 ( = 1,3) - нулевые выходы разрядов регистра 11,27 (1 = 1,6) - элементы И 28( = 1,6) - выходы элементов И 27.Рассмотрим работу устройства, Перед началом работы все разряды регистра 11 установлен ы в нулевое состояние. По входам 1 и 2 входные операнды в двоичном коде поступают на первые входы соответствующих элементов И 3 и И 4, На первый управляющий вход 5 устройства поступает сигнал и с выхода И 3 операнд А поступает через второй элемент ИЛИ 7 на вход дешифратора 8, с выхода которого через соответствующий элемент ИЛИ первой 9 группы поступает сигнал на один из входов регистра 11, Далее сигнал поступает на второй управляющий вход 6 устройства и операнд В аналогичным образом проходит с выхода второго элемента И и через рассмотренные элементы на один из входов регистра 11. Сигнал, соответствующий ) д (в) = 0 проходит через элементы И 4 (3) при подаче сигналов на управляющие входы 5 (6) и запоминается в триггерах 23/22. Затем сумматор 24 по модулю два прид )в посылает сигнал на вторые входы элементов И первой 13 и второй 14 групп, Выходной сигнал коммутатора 12, соответствующий значению А, В (проб п), в унитарном коде поступает на первые входы К - го элемента И 13 группы и К - го элемента И 14 групп(К=1,2 щ -1).Если )А =)в, то выхоцной аналог сумматора 24 по модулю два отсутствует. Элементы И 13 открыты, а элементы И 14 группы закрыты (на второй запрещающий вход элемента И 13 группы сигнал с выхода сумматора 24 по модулю два не поступает). В этом случае сигнал с выхода К - го элемента И 13 группы поступает на вход К - го элемента ИЛИ 15 группы, с выхода которого сигнал поступает на вход шифратора 16, с выхода которого после подачи сигнал на третий управляющий вход 18 устройства через элемент И 17 поступает на выход 19 устройства.Если )д)в, то сигнал с выхода сумматора 24 по модулю два присутствует. Этот сигнал закрывает элементы И 13 группы и разрешает прохождение сигнала с выхода коммутатора 12 через элементы И 14 группы, В этом случае сигнал с выхода К-го элемента И 14 поступает на вход (т - К) - го элемента ИЛИ 15 группы,Формула изобретения Устройство для умножения чисел по модулю, содержащее дешифратор, первый элемент ИЛИ, две группы элементов ИЛИ, две группы элементов Ипервый и второй элементы И и шифратор, причем выходы первой группы дешифратора соединены с первыми входами соответствующих элементов ИЛИ первой группы и входами первого элемента ИЛИ, выход которого соединен с входом первого элемента И, выходы второй группы дешифратора соединены с вторыми входами соответствующих элементов ИЛИ первой группы, первые входы элементов И первой и второй групп соединены между собой, а их выходы - с первыми и вторыми входами соответствующих элементов ИЛИ второй группы, отл и ч а ю щееся тем, что. с целью упрощения устройства, в него введены третий, четвертый и пятый элементы И, коммутатор, второй элемент ИЛИ, сумматор по модулю два, два триггера и регистр, причем входы первого и второго операндов устройства соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с первым и вторым управляющими входами устройства, а выходы - соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с входом дешифратора, выходы элементов ИЛИ первой группы соединены с соответствующими входами регистра, выходы которого соединены с соответствующими входами коммутатора, выходы которого соединены с первыми входами элементов И первой группы, вторые входы которых соединены с вторыми входами соответствующих элементов И второй группы и выходом сумматора по модулю два, первый и второй входы которого соединены соответственно с выходами первого и второго триггеров, входы которых соединены соответственно с выходами первого и второго элементов И, выход первого элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого соединен с первым управляющим входом устройства, второй управляющий вход которого соединен с вторым входом первого элемента И, выходы элементов ИЛИ второй группы соединены с соответствующими входами информатора, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с третьим управляющим входом устройства, а выход - с выходом устройства,1667055 рректор О,Кравцов ктор О,Спесивых роизводственно-издательский комбинат "Патент", г. Ужгород, ул.Га 101 аз 2524ВНИИПИ Госу Л Рб В Рбу Я 5 ставитель Е.Мурзинахред М Моргентал Тираж 403 Подписноеенного комитета по изобретениям и открытиям при ГКНТ СССР 13035, Москва, Ж, Раушская наб.,4/5

СмотретьЗаявка

4754343, 31.10.1989

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ФОМЕНКО ОЛЕГ НИКОЛАЕВИЧ, КРАСНОБАЕВ ВИКТОР АНАТОЛЬЕВИЧ, ИРХИН ВАЛЕРИЙ ПЕТРОВИЧ, ПАНКОВ ВЛАДИМИР МИХАЙЛОВИЧ, УВАРОВ ВЛАДИМИР НИКОЛАЕВИЧ, КУЦЫЙ СЕРГЕЙ ИВАНОВИЧ, ЖУРАВЛЕВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ

МПК / Метки

Метки: модулю, умножения, чисел

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/4-1667055-ustrojjstvo-dlya-umnozheniya-chisel-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел по модулю</a>

Предыдущий патент: Сумматор-умножитель по модулю три

Следующий патент: Устройство для суммирования-вычитания чисел с плавающей запятой

Случайный патент: Устройство для разделения сыпучих смесей