Запоминающее устройство с обнаружением и исправлением модульных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1304080

Автор: Бородин

Текст

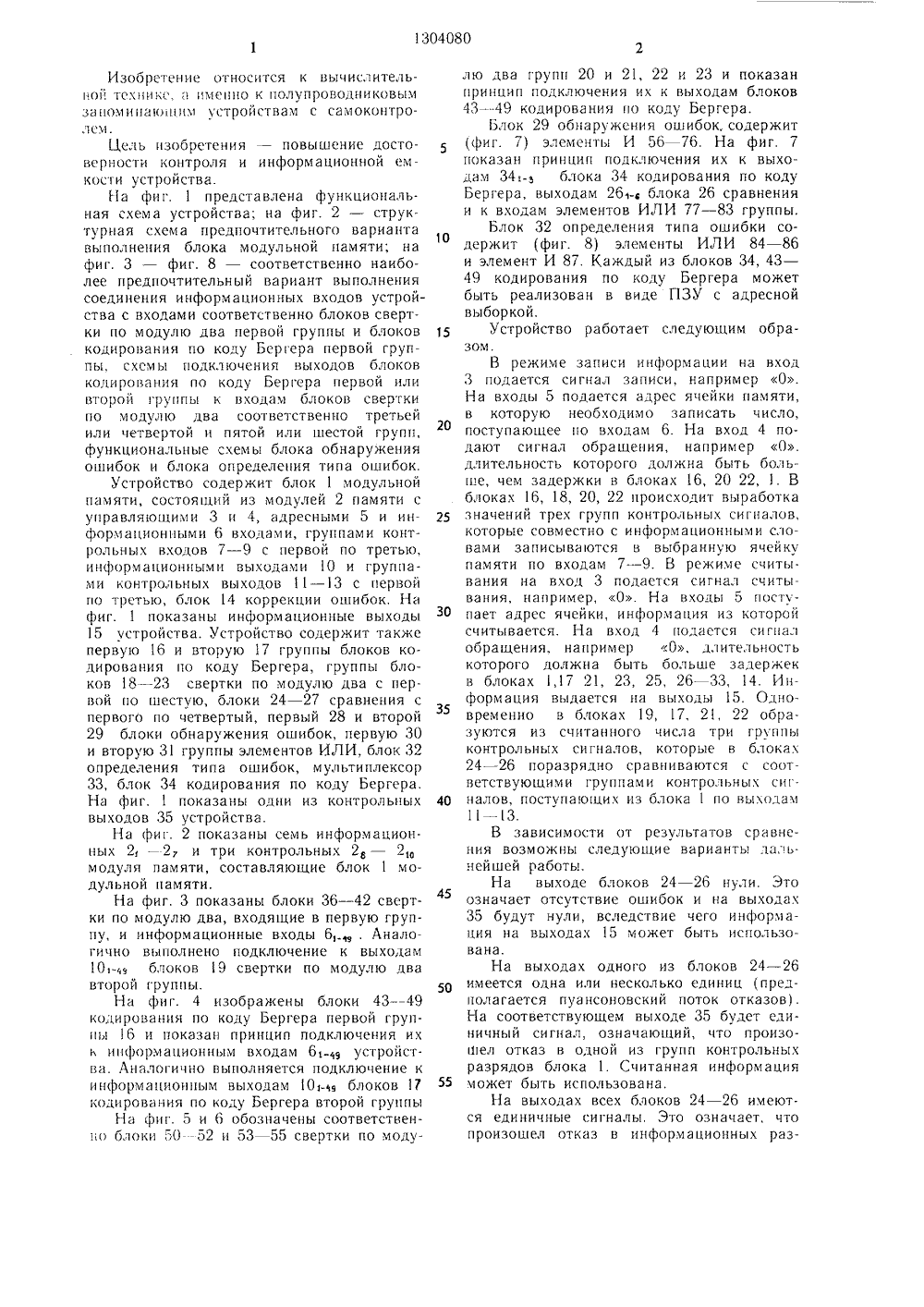

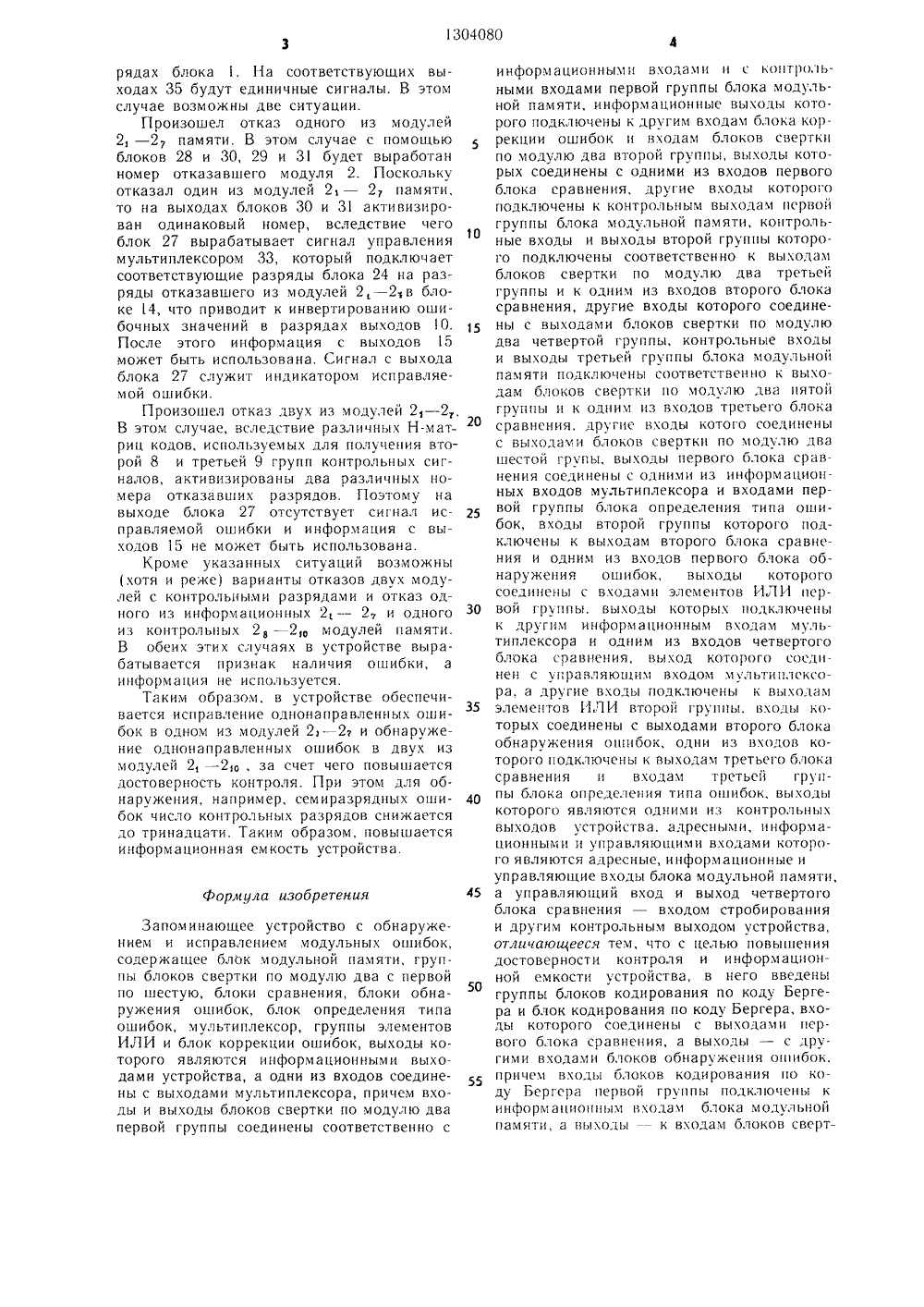

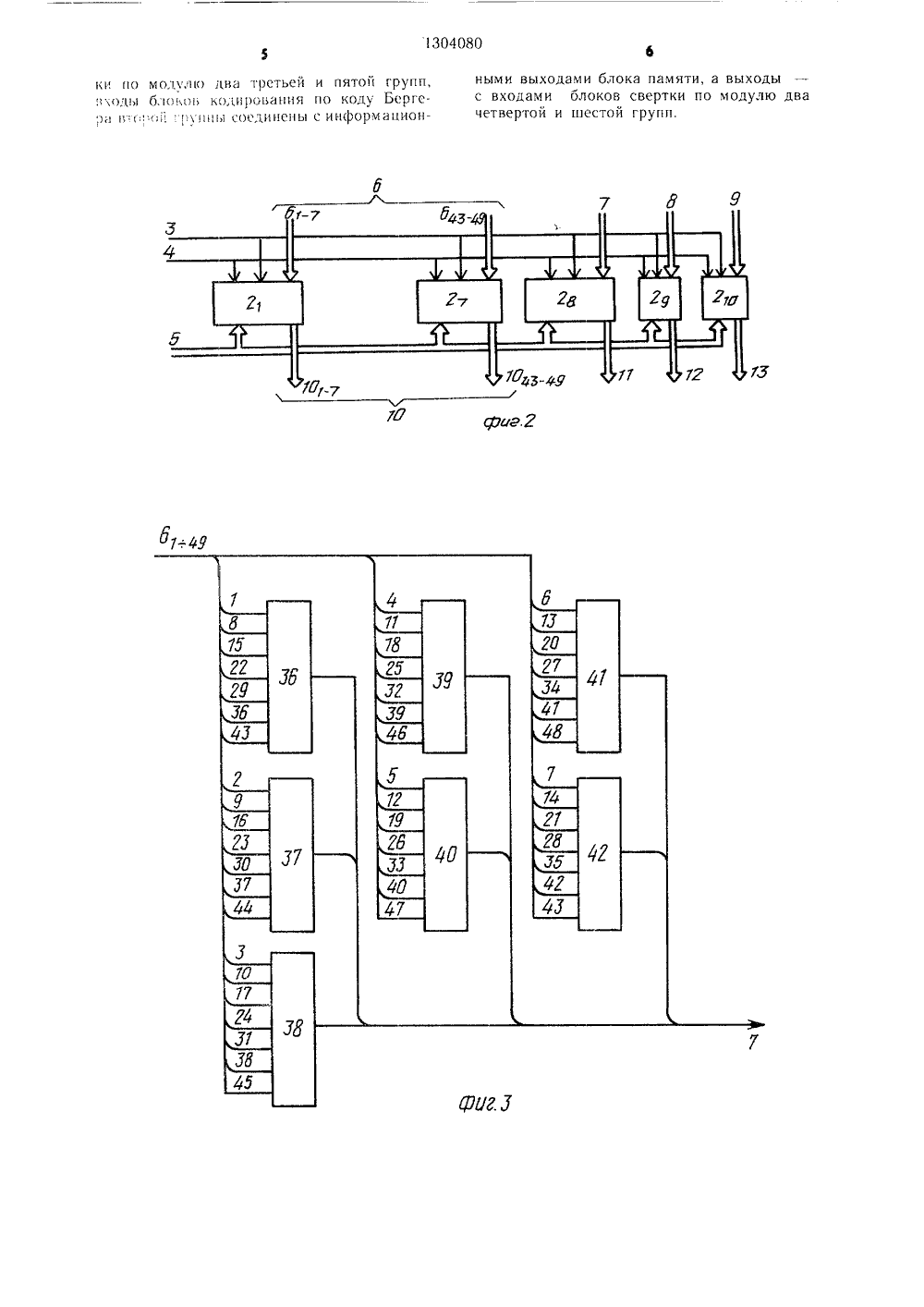

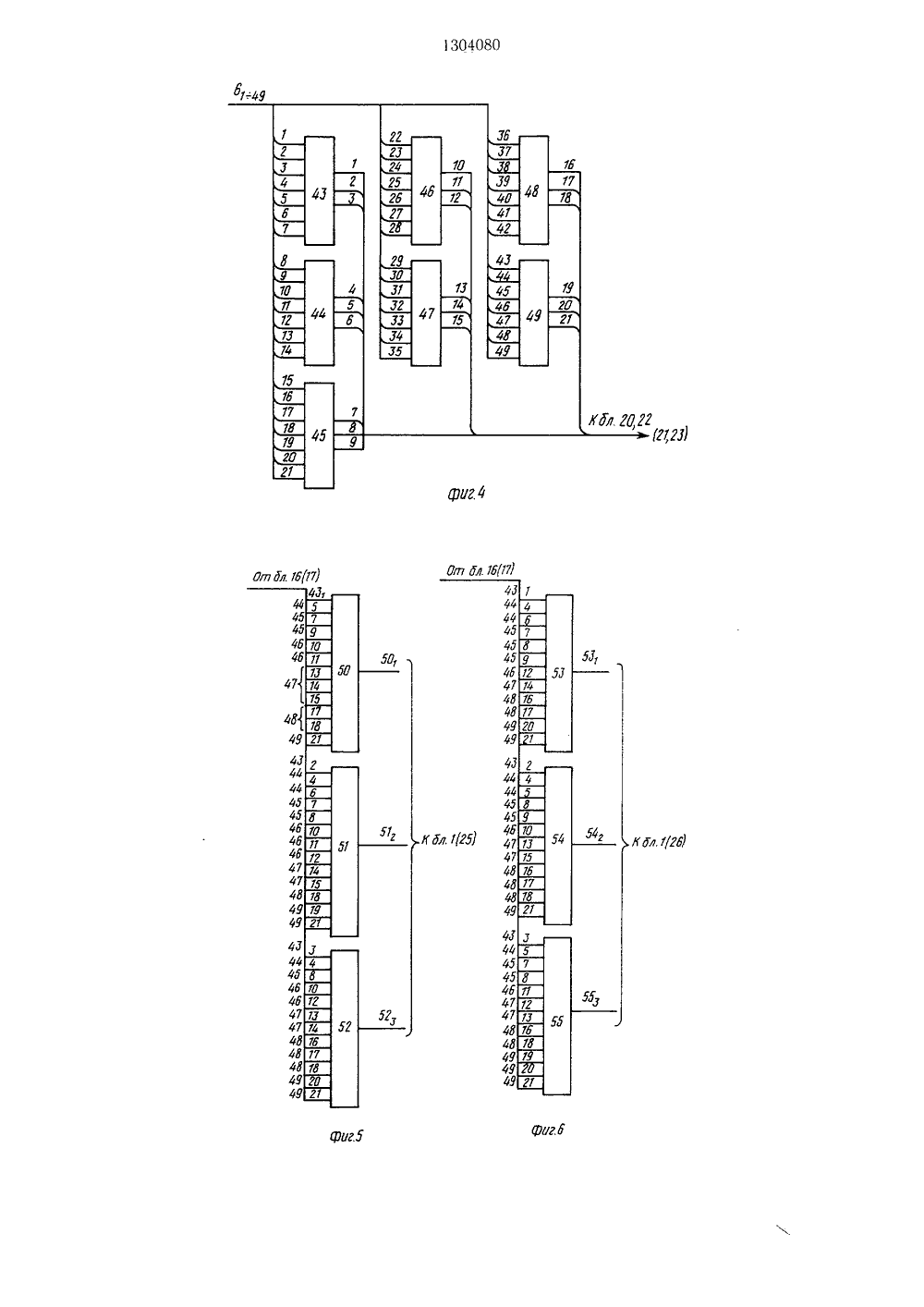

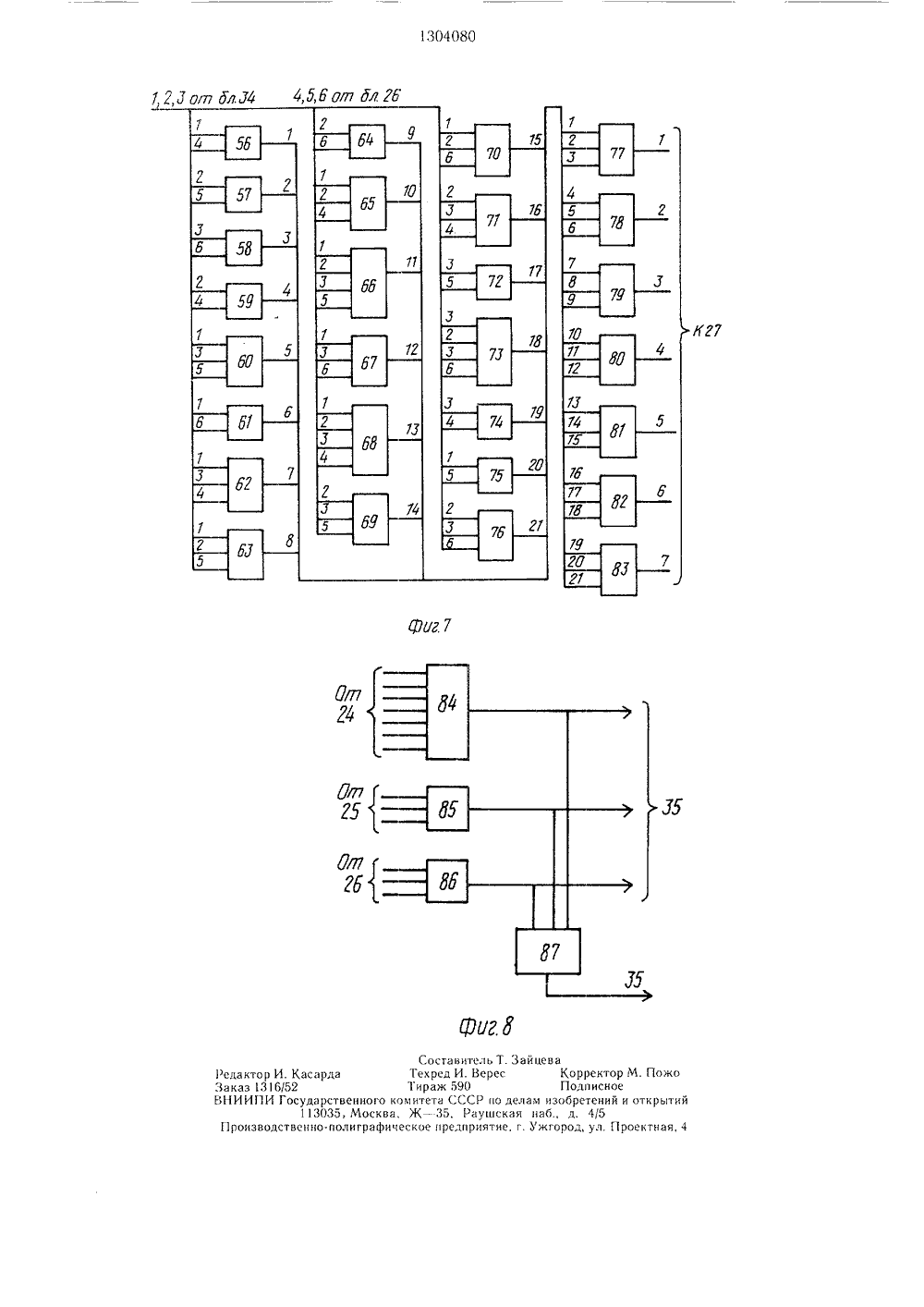

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А 1 11 С 29 00 СИСОЙ13ИВПца ТЕНИЯ 00 С) ГОСУДАРСТВЕННЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗОБ А ВТОРСКОМУ СВИДЕТЕЛЬС(71) Московский энергетический институт (72) Г. А, Бородин(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ МОДУЛЬНЫХ ОШИБОК(57) Изобретение относится к вычислительной технике, .а именно к полупроводниковым запоминающим устройствам. Целью изобретения является повышение достоверности контроля и повышение информационной емкости устройства. Устройство содержит блок 1 модульной памяти, состоящий из модулей 2 памяти, с тремя группами контрольных входов 7 - 9 и выходов1 - 13, блок 14 коррекции ошибок, две группы бло 54 у ЯО 1304080 ков 16 и 17 кодирования по коду Бергера, шесть групп блоков 1823 свертки по модулю два, четыре блока 24 -27 сравнения, два блока 28 и 29 обнаружения ошибок. две группы элементов ИЛИ 30 и 31, блок 32 определения типа ошибок, мультиплексор 33, блок 34 кодирования по коду Бергера. Путем ввода в устройство блоков кодирования по коду Бергера обеспечивается обнаружение многократных однонаправленных ошибок в двух, например, семиразрядных модулях 2 памяти и исправление их в одном из модулей 2 памяти, за счет чего повышается достоверность контроля устройства. При этом число контрольных разрядов в блоке 1 памяти снижается, например, до тринадцати, за счет чего повышается информационная емкость устройства. Блоки 28 - 31 служат для определения номеров модулей 2, в которых произошли однонаправленные ошибки во всех разрядах, а блок 32 вырабатывает сигнал некорректируемой ошибки и сигналы наличия ошибок. 8 ил.510 15 20 25 30 35 40 45 50 55 Изобретение относится к вычислительой технике, а именно к полупроводниковым за пом и паюгцнм устройствам с самоконтроЦель изобретения - повышение достоверности контроля и информационной емкости устройства.На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - структурная схема предпочтительного варианта выполнения блока модульной памяти; на фиг. 3 - фиг. 8 - соответственно наиболее предпочтительный вариант выполнения соединения информационных входов устройства с входами соответственно блоков свертки по модулю два первой группы и блоков кодирования по коду Бергера первой группы, схемы подключения выходов блоков кодирования по коду Бергера первой или второй группы к входам блоков свертки по модулю два соответственно третьей или четвертой и пятой или шестой групп, функциональные схемы блока обнаружения ошибок и блока определения типа ошибок.Устройство содержит блок 1 модульной памяти, состоящий из модулей 2 памяти с управляющими 3 и 4, адресными 5 и информационными 6 входами, группами контрольных входов 7 - -9 с первой по третью, информационными выходами 10 и группами контрольных выходов 11 - 3 с первой по третью, блок 14 коррекции ошибок. На фиг. 1 показаны информационные выходы 15 устройства. Устройство содержит также первую 16 и вторую 17 группы блоков кодирования по коду Бергера, группы блоков 18 - 23 свертки по модулю два с первой по шестую, блоки 24 - 27 сравнения с первого по четвертый, первый 28 и второй 29 блоки обнаружения ошибок, первую 30 и вторую 31 группы элементов ИЛИ, блок 32 определения типа ошибок, мультиплексор 33, блок 34 кодирования по коду Бергера. На фиг. 1 показаны одни из контрольных выходов 35 устройства,На фиг. 2 показаны семь информационных 2 - 2, и три контрольных 26 - 2 модуля памяти, составляющие блок 1 модульной памяти.На фиг. 3 показаны блоки 36 - 42 свертки по модулю два, входящие в первую группу, и информационные входы 6,. . Аналогично выполнено подключение к выходам 10- блоков 19 свертки по модулю два второй группы.На фиг. 4 изображены блоки 43 - 49 кодирования по коду Бергера первой группы 16 и показан принцип подключения их к информационным входам 6устройства. Лналогично выполняется подключение к информационным выходам 10 ч блоков 17 кодирования по коду Бергера второй группыНа фиг. 5 и 6 обозначены соответствен-о блоки 50 -52 и 53 - 55 свертки по модулю два групп 20 и 21, 22 и 23 и показан принцип подключения их к выходам блоков 4349 кодирования по коду Бергера.Блок 29 обнаружения ошибок, содержит фиг. 7) элементы И 56 76. На фиг. 7 показан принцип подключения их к выходам 34- блока 34 кодирования по коду Бергера, выходам 26блока 26 сравнения и к входам элементов ИЛИ 77 - 83 группы.Блок 32 определения типа ошибки содержит (фиг. 8) элементы ИЛИ 84 - 86 и элемент И 87. Каждый из блоков 34, 43 - 49 кодирования по коду Бергера может быть реализован в виде ПЗУ с адресной выборкой.Устройство работает следующим образом.В режиме записи информации на вход 3 подается сигнал записи, например О. На входы 5 подается адрес ячейки памяти, в которую необходимо записать число, поступающее по входам 6. На вход 4 подают сигнал обращения, например О. длительность которого должна быть больше, чем задержки в блоках 16, 20 22, 1. В блоках 16, 18, 20, 22 происходит выработка значений трех групп контрольных сигналов, которые совместно с информационными словами записываются в выбранную ячейку памяти по входам 7 - 9. В режиме считывания на вход 3 подается сигнал считывания, например, О. На входы 5 поступает адрес ячейки, информация из которой считывается. На вход 4 подастся сигнал обращения, например О, длительность которого должна быть больше задержек в блоках 1,17 1, 23, 25, 26 в 33, 14. Информация выдается на выходы 15. Одновременно в блоках 19, 17, 21, 22 образук)тся из считанного числа три группы контрольных сигналов, которые в блоках 24 - 26 поразрядно сравниваются с соответствующими группами контрольных сигналов, поступающих из блока 1 по выходам 11 - 13.В зависимости от результатов сравнения возможны следующие варианты дальнейшей работььНа выходе блоков 24 - 26 нули. Это означает отсутствие ошибок и на выходах 35 будут нули, вследствие чего информация на выходах 15 может быть использована.На выходах одного из блоков 24 - 26 имеется одна или несколько единицпредполагается пуансоновский поток отказов). На соответствующем выходе 35 будет единичный сигнал, означающий, что произошел отказ в одной из групп контрольных разрядов блока 1. Считанная информация может быть использована.На выходах всех блоков 24 - 26 имеются единичные сигналы. Это означает, что произошел отказ в информационных раз 1304080рядах блока 1. На соответствующих выходах 35 будут единичные сигналы. В этом случае возможны две ситуации.П роизошел отказ одного из модулей 2, - 2 памяти. В этом случае с помощью блоков 28 и 30, 29 и 31 будет выработан номер отказавшего модуля 2. Поскольку отказал один из модулей 2 - 2, памяти, то на выходах блоков 30 и 31 активизирован одинаковый номер, вследствие чего блок 27 вырабатывает сигнал управления мультиплексором 33, который подключает соответствующие разряды блока 24 на разряды отказавшего из модулей 2, - 2 в блоке 14, что приводит к инвертированию ошибочных значений в разрядах выходов 10. После этого информация с выходов 15 может быть использована. Сигнал с выхода блока 27 служит индикатором исправляемой ошибки.Произошел отказ двух из модулей 2, - 2 В этом случае, вследствие различных Н-мат 20 риц кодов, используемых для получения второй 8 и третьей 9 групп контрольных сигналов, активизированы два различных номера отказавших разрядов. Поэтому на выходе блока 27 отсутствует сигнал ис правляемой ошибки и информация с выходов 15 не может быть использована.Кроме указанных ситуаций возможны (хотя и реже) варианты отказов двух модулей с контрольными разрядами и отказ одного из информационных 2, - 2, и одного из контрольных 2, - 2 модулей памяти. В обеих этих случаях в устройстве вырабатывается признак наличия ошибки, а информация не используется.Таким образом, в устройстве обеспечивается исправление однонаправленных ошибок в одном из модулей 2 - 2 и обнаружение однонаправпенных ошибок в двух из модулей 2, - 21 о, за счет чего повышается достоверность контроля. При этом для обнаружения, например, семиразрядцых оши бок число контрольных разрядов снижается ло тринадцати. Таким образом, повышается информационная емкость устройства. Фор,чула изобретенияЗапоминающее устройство с обнаружением и исправлением модульных ошибок, содержащее блок модульной памяти, группы блоков свертки по модулю два с первой по шестую, блоки сравнения, блоки обнаружения ошибок, блок определения типа ошибок, мультиплексор, группы элементов ИЛИ и блок коррекции ошибок, выходы которого являются информационными выходами устройства, а одни из входов соединены с выходами мультиплексора, причем входы и выходы блоков свертки по модулю два первой группы соединены соответственно с информационными входам ц и с коцт 1 ихьными входами первой группы блока модульной памяти, информационцыс выходы которого подключены к другим входам блока коррекции ошибок ц входам блоков свертки по модулю два второй группы, выходы которых соединены с одними из входов первого блока сравнения, другие входы которого подключены к контрольным выходам первой группы блока модульной памяти, контрольные входы и выходы второй группы которого подключены соответственно к выходам блоков свертки по модулю два третьей группы и к одним из входов второго блока сравнения, другие входы которого соединены с выходами блоков свертки по модулю два четвертой группы, контрольные входы и выходы третьей группы блока модульной памяти подключены соответственно к выходам блоков свертки по модулю лва пятой группы и к одним из входов третьего блока сравнения, другие входы котого соединены с выходами блоков свертки по модулю два шестой групы, выходы первого блока сравнения соединены с одними из информационных входов мультиплексора и входами первой группы блока определения типа ошибок, входы второй группы которого подключены к выходам второго блока сравнения и одним из входов первого блока обнаружения ошибок, выходы которого соединены с входами элементов ИЛИ первой группы, выходы которых подключены к другим информационным входам мультиплексора и одним из входов четвертого блока сравнения, выход которого сослинен с управляющим входом мультиплексорара, а другие входы подключены к выхолам элементов ИЛИ второй группы, входы которых соединены с выходами второго блока обнаружения ошибок, одни из входов которого подключены к выходам третьего блока сравнения и входам третьей группы блока определения типа ошибок, выходы которого являются одними из контрольных выходов устройства, адресными, информационными и управляющими входами которого являются адресные, информационные и управляющие входы блока модульной памяти, а управляющий вход и выход четвертого блока сравнения - входом стробирования и другим контрольным выходом устройства, отличающееся тем, что с целью повышения достоверности контроля и информационной емкости устройства, в него введены группы блоков кодирования по коду Бергера и блок кодирования по коду Бергера, входы которого соединены с выходами первого блока сравнения, а выходы - с другими входами блоков обнаружения ошибок, причем входы блоков кодирования по коду Бергера первой группы подключены к информационным вхолам блока модульной памяти, а выходы -- к входам блоков свсрт ки по модулю дна третьей и пятой групп, входы блоков кодирования по коду Бергера н-ч ч,й руины соединены с информационными выходами блока памяти, а выходы с входами блоков свертки по модулю два четвертой и шестой групп.1304080 Оп г 5 ЗайцеваК делам изоб ая наб., , г. Ужгорг Г,1 ол для 4,5,бол дд Рб Составители Т да Техред И. Верес Тираж 590 твенного комитета СССР по 5, Москва, Ж, Раушс юлиграфическое предприяти

СмотретьЗаявка

3997891, 30.12.1985

МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, модульных, обнаружением, ошибок

Опубликовано: 15.04.1987

Код ссылки

<a href="https://patents.su/6-1304080-zapominayushhee-ustrojjstvo-s-obnaruzheniem-i-ispravleniem-modulnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с обнаружением и исправлением модульных ошибок</a>

Предыдущий патент: Буферное запоминающее устройство

Следующий патент: Композиция для изготовления фольгированных изделий

Случайный патент: Приспособление для погрузки и разгрузки железнодорожных платформ с лесоматериалом