Устройство для исправления двухкратных ошибок в блоках передачи и хранения информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1173417

Автор: Поваляев

Текст

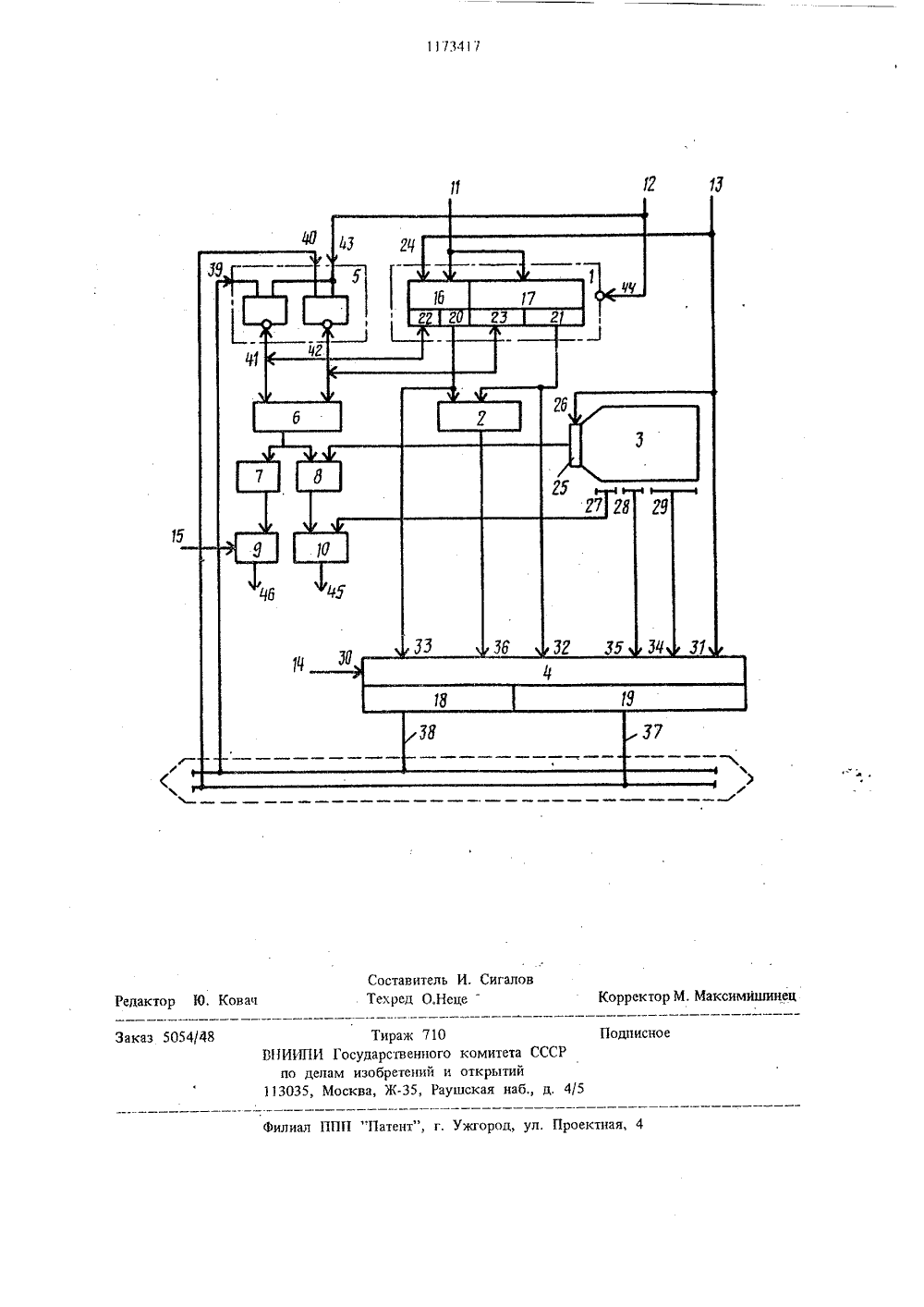

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН ПИСАНИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕЛЬСТВ ТОРСК ом ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИй(54) (57) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ,ДВУКРАТНЫХ. ОШИБОК В БЛОКАХ ПЕРЕДАЧИ И ХРАНЕНИЯ ИНФОРМАЦИИ, содержащее входной регистр, первый и второй формирователи синдрома ошибки, схему сравнения,регистр ошибок, причем группа информацион.ных и группа контрольных входов устройствасоединены соответственно с группой информа э.ционных и группой контрольных разрядоввходного регистра, группы выходов информа. -ционных и контрольных разрядов входногорегистра соединены с входами первого формирователя синдрома ошибки, о т л и ч а ющ е ес я тем, что, с целью повышениябыстродействия и достоверности передачи данных, в устройство введены блок памяти ошибок, блок коррекции, группа инверторов суправляемым выходом, элемент ИЛИ и триггер ошибки коррекции, причем выход первогоформирователя синдрома ошибки соединен спервым входом схемы сравнения, входомконтрольного кода блока коррекции и адресным входом блока памяти ошибок, выходыпризнаков ошибок, ошибок контрольной частисообщения, ошибок информационной частисообщения блока памяти ошибок соединенысоответственно с первым информациринымвходом регистра ошибок, входом признакаинформацйонной ошибки и входом признакаконтрольной ошибки, вход команды чтения 801173417 4 6 06 Г 11/08 6 11 С 29 00 устройства соединен с входом разрешениясчитывания блока памяти ошибок, входомустановки нуля контрольной части входного регистра и входом признака команды чтенияблока коррекции, группы выходов информационных и контрольных разрядов входного регистра соединены соответственно с группамиинформационных и контрольных входов блока коррекции, вход команды записи устрой.ства соединен с входом признака командызаписи блока коррекции, группы информационных и контрольных выходов которого соединены с входами соответствующих элементовгруппы инверторов с управляемым выходом иявляются соответственно группами информационных и контрольных выходов устройства,выходы группы инверторов с управляемымивыходами соединены с информационными и(контрольными входами второго формирователясиндрома ошибки, группы управляемыхвыходов информационных и контрольных разря.дов входного регистра соединены с группамиинформационных и контрольных входов второго формирователя синдрома ошибки, выходкоторого соединен с вторым входом схемысравнения и через элемент ИЛИ с информационным входом триггера ошибки коррекции,выход схемы сравнения соединен с вторыминформационным входом регистра ошибок, .выход которого является идентификационнымвыходом сигнала ошибки устройства, тактовыйвход устройства соединенн с входом синхронизации триггера ошибки коррекции, выходкоторого является выходом сигнала ошибкикоррекции устройства, управляющий вход устройства соединен с входом управления выходами входного регистра и управляющим вхо дом группы инверторов с управляемым вы 117347Изобретение относится к вычислительной технике и может быть использовано для исправления двукратных ошибок в блоках хранения информации и трактах приемо. передачи дискретных данных, например, при считывании 5 данных из оперативной памяти в процессор вы. числительной машины или записи даниях иэ процессора в оперативную память.ЪЦе 1 ь изобретения - , повышение быстродей ствия устройства идостоверности передачи, данных.На чертеже представлена блок. схема предлагаемого устройства.Устройство содержит входной регистр. 1, 15 первый формироватвдь 2 синдрома ошибки, блок 3 памяти ошибок, блок 4 коррекции,1 группу 5 инверторов с управляемым выходом, второй формирователь б синдрома ошибки, элемент ИЛИ 7, схему 8 сравнения, триггер 9 20ошибки коррекции, регистр 10 ошибок, вход 11 сообщения, вход 12 управления, вход 13 команды чтения, вход 14 команды записи и тактовый вход 15 устройства. На первую группу16 информационных входов входного регистра 251 поступает контрольная часть сообщения, а на вторую группу 17 - информационная часть. Блок коррекции разделен на две части: конт.ольную 18 и информационную 19, Входнойегистр состоит из О-триггеров с прямыми 30 и тристабильными выходами. При этом выходы 20 и 21 входного регистра образованы прямыми выходами триггеров, а выходы 22 и 23 - их тристабильными выходами, вход 24 установки нуля контрольной части входного регистра соединен с входом команды чтения. Блок 3 памяти ошибок может быть выполнен, , например, на ППЗУ и имеет адресный вход 25, , вход 26 разрешения считывания, выход 27признаков ошибок, выходы 28 и 29 признаков 4 р ошибок контрольной и информационной частисообщения. Блок 4 коррекции имеет следующиевходы: признаков команд записи 30 и чтения 31, информационных 32 и контрольных 33 разрядов входного регистра, признака информационной 34 и контрольной 35 ошибок и синдромного кода 36, Выходы блока коррекции сгруппированы в две группы, составляющие интерфейс межблочнойсвязи вычислительной машины, и являются соответственно группами 50 информационных 37 и контрольных 38 выхо. дов устройства. Входы группы,инверторов с уп равляемыми выходами подразделяются на кон. трольные 39 и информационные 40. Указаннаягруппа имеет соответствующие входам тристабильные управляемые выходы 41 и 42, вход 43 разрешения, соединенный с управляющим вхо. дом устройства и входом 44 разрешения триста. бильных выходов входного регистра. Выходы регистра ошибок и триггера ошибки коррекции составляют соответственно идентификационный выход 45 ошибки устроиств и выход 46 ошиб ки коррекции устройства.В основу построения формирователей 2 и б синдрома ошибки положена матрица, состоя. шая из элементов, реализующих функцию ИСКЛ 0 ЧАЮЩЕЕ ИЛИ. Блок 4 коррекции реализу. ет на своих выходах следующие логические функции%63) = Р (,ЕЗЭ. мЮ)ч ЕЭ, П. РВс,: 5 Я ЕС, С, Й мС,ЕС )91,где ВО; - функция на 1.й информационной вы. ходной шине устройства;ВС - функция на 1- й контрольной выход.-., ной шкапе устройства;О; - информационный бит сообщения;С - контрольный бит сообщения;ЕО; - ошибка информационного бита сооб. щения:ЕС - ошибка контрольного биты сообщения;В - 1.й разряд синдромного кода;ЛВ - команда чтения;ЧЧ - команда записи.При отсутствии команд чтения или записи 5 лок,коорекции отключается от интерфейса,Управляющие сигналы на входах 12 - 15 уст. ройства формируются устройством, входящим в состав ЭВМ, использующим предлагаемое устройство для исправления двукратных ошибок,Устройство работает следующим образом, Передаваемое информационное сообщение, например 16 бит,с сопровождающим его контрольным кодом, например 10 бит, поступает на вход 11 сообщения устройства и записывается во входной регистр, На входе 44 разрешения имеется сигнал, разрешающий трансляцию записанной информации через тристабильные выходы 22 и 23 на входы формирователя б синдрома ошибки, С прямых выходов входного регистра записанное сообщение поступает на формирователь 2, а с три. стабильных выходов - на формирователь 6 синдрома ошибки. Оба формирователя складывают по модулю два информационные и контрольные биты сообщения в соответствии с Матрицей формирования синдрома ошибки (табл. 1), Вычисленные синдромы ошибки с выходов обоих формирователей сравниваются на схеме 8 сравнения, Результат сравнения поступает на второй информационный вход регистра ошибок. Код синдрома ошибки с вы хода формирователя 2 синдрома ошибки пос.тупает на адресный вход 25 блока 3 памяти ошибки, который выполнен на программиру.емом постоянном запоминающем устройстве ППЗУ объемом 1 Кх 29. На входе 26 разрешения считывания блока памяти ошибок имеет ся разрешающий сигнал (активизированная ко. манда чтение), позволяющий прочитать из ППЗУ содержимое ячейки, адрес которой задан кодом синдрома ошибки с выхода формирователя 2 синдрома ошибки. В ячейках О ППЗУ (табл. 3 и 9) прошиты заранее запрограммированные варианты одиночных и двубитных ошибок кода (26, 16). Число возможных двубитных ошибок этого кода оценивается чис. лом сочетаний С = 325, которое совместно 5 с 2 б-ю однобитными ошибками и определяет массив корректируемых ошибок названного кода. По адресу 0000 прошита нулевая инфор. мация - отсутствие ошибок, По адресам локаторов ошибки (коды столбцов матрицы) э 0прошит соответствующий локатору бит. По, адресам, равным сумме по модулю два кодов локаторов, прошиты биты позиций, локаторы которых участвовали в создании этой суммы. Кроме того, в ячейках ППЗУ прошиты призна ки ошибок, соответствующие вариантам оши бок: однобитная ошибка и двубитная ошибка, В массиве ячеек, равном 1 К - 352, прошит признак ошибки "Больше двух ошибок".Признаки ошибок совместно с сигналом со схемы сравнения записываются в регистр ошибок. Выходы 28 и 29 признаков ошибок в информационных и контрольных битах поступают на вход блока коррекции, где складываются по модулю два соответственно с информационными и контрольными битами сообщения из входного регистра. Скорректированная информация, сопровождаемая скорректированным контрольным кодом, через выходы 37 и 38 передат40 ется на интерфейс (например, общая шина) межблочной связи вычислительной машины через магистральные передатчики с открытыь коллекторным выходом, На вход 44 разрешения по- дается сигнал, отключающий тристабильные выходы 22 и 23 входного регистра и подклю.4 чающий выходы 42 и 41 блока инверторов с управляемым выходом к входам формиро. вателя б синдрома ошибки. Если коррекция сообщения бь 1 ла выполнена устройством пра.50 вильно, то ни один из синдромных битов не будет активизирован и логический элемент ИЛИ будет транслиро".ать на информационный вход триггера ошибки коррекции "0", В про.тивном случае указанный триггер будет активи,-,зирован. Зались в триггер 9 ошибки коррекцииосуществляется воздействием на тактовый вход15 устройства. При работе предлагаемого устройства в тракте записи данных (например, при записи данных из процессора в оперативную память), записываемая информация поступает на вход 11 устройства и записывается в информационную часть входного регистра. Вход 14 команды записи активизирован, а на входе 13 команды чтения - "0", который, воздействуя, на вход 24 установки нуля контрольной части входно. го регистра, сбрасывает ее триггеры в нулевое состояние. На входе 12 управления имеется управляющий сигнал, позволяющий трансляцию записанного во входной регистр 1 сообщения через тристабильные выходы 22 и 23 на входы формирователя б синдрома ошибки. В этом режиме работы устройства формирователя 2 и 6 синдрома ошибки генерируют контрольный код, соответствующий принятой во входной регистр информации согласно матрице (табл. 2). Результаты обеих генераций должны совпадать, если соответствующее оборудование работает правильно. В противном случае выход схемы 8 сравнения будет активизирован и триггер ошибки оборудования регистра 10 ошибок будет также активизирован, Блок 3 памяти ошибок блокирован запрещающим сигналом на входе 26 разрешения считывания. (отсутствие команды чтение), поэтому с выходов 28 и 29 блока 3 в блок 4 коррекции поступают "1". Активизированный вход 14 команды записи разрешает передачу сгенерированного формировател"м 2 контрольного кода через блок 4 коррекции (выход 38) и свободную трансляцию входного сообщения на выход 37. В этом режиме работы функциясуммы по модулю два в блоке 4 коррекции подавлят, ется и блок производит трансляцию информа; - ; ции и присвоенного ей контрольного кода.на интерфейс. На управляющий вход 12 подается сигнал, разрешающий подключение выходов 42 и 41 группы 5 инверторов к формирователю 6 синдрома ошибки и отключающий тристабильные выходы 22 и 23 входного регистра от этого формирователя. Формирователь б вырабатывает синдром ошибки, который при наличии ошибки трансляции на интерфейс активизирует элемент ИЛИ 7 и триггер 9 ошибки.1173437 Составитель И Техред О,Нец Сигал Ю, К аказ 5054/4 одписно ета СССР тиинаб д, 4/ лиал ППП "Патент", г. Ужгород, ул. Проектная,Тираж 710 В 11 ИИПИ Государственного ком по делам изобретений и отк 113035, Москва, Ж, Раушска

СмотретьЗаявка

3616777, 27.05.1983

ПРЕДПРИЯТИЕ ПЯ А-7638

ПОВАЛЯЕВ ЭДУАРД ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/08, G11C 29/00

Метки: блоках, двухкратных, информации, исправления, ошибок, передачи, хранения

Опубликовано: 15.08.1985

Код ссылки

<a href="https://patents.su/4-1173417-ustrojjstvo-dlya-ispravleniya-dvukhkratnykh-oshibok-v-blokakh-peredachi-i-khraneniya-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления двухкратных ошибок в блоках передачи и хранения информации</a>

Предыдущий патент: Устройство для обнаружения искажений в двоичных последовательностях

Следующий патент: Устройство для ввода-вывода информации

Случайный патент: Устройство для ввода информации