Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

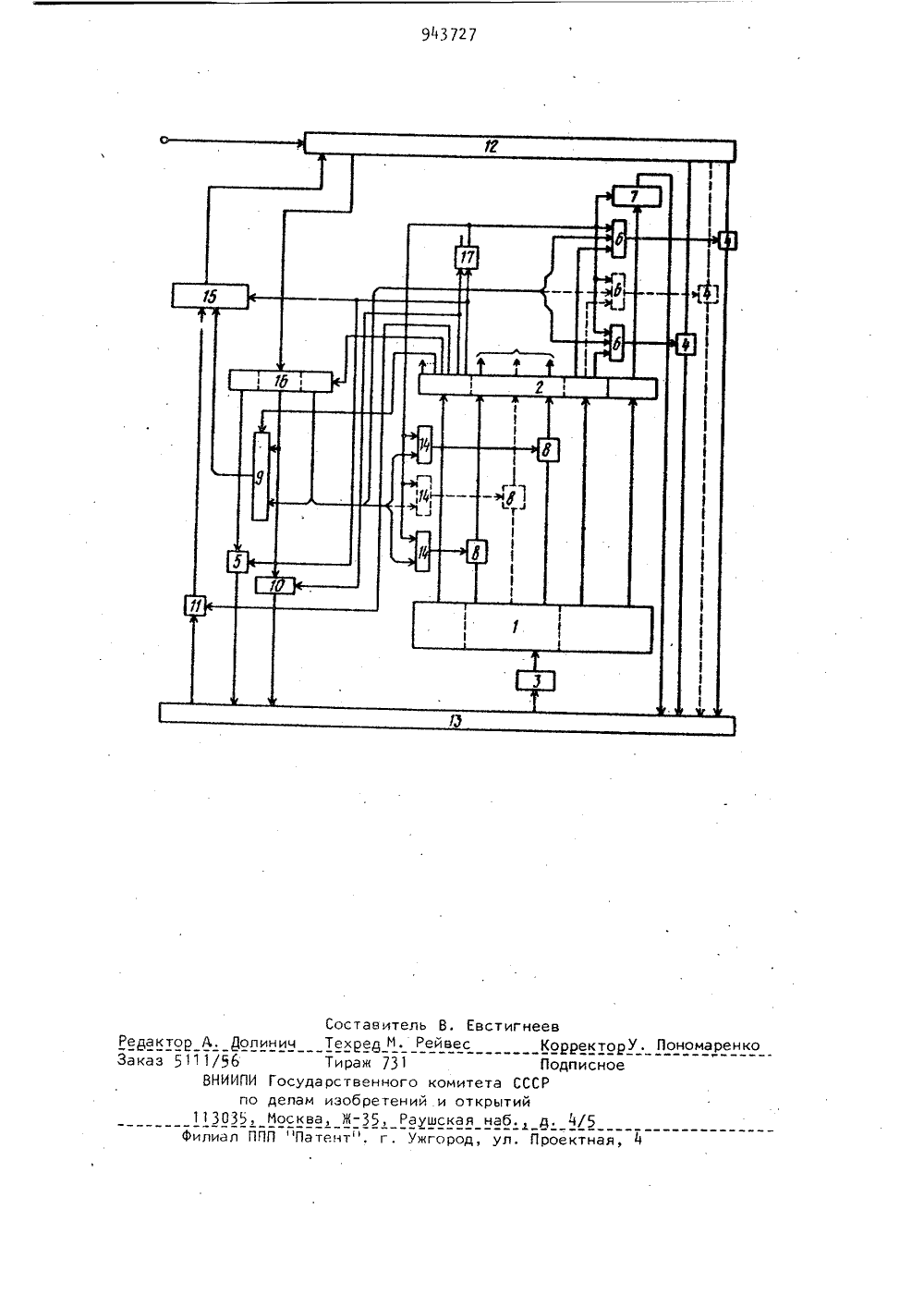

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 943727 Союз СоветскикСоциалистическиеРеспублик(22) Заявлено 26. ОЙ. 77 (21) 2479572/18-2 Ьс присоелиненйем заявки М(23) Приоритет(51) М. Кл. 6 06 Р 9/46 Гевударстиеьй квветет. СССР па двлвк изобретений н еткуытвй(5 Й) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ 1Изобретение относится к .вычисли-тельной технике и может быть использовано при построении ЭВМ различных классов и, в частности, однокристальных эмулирующих микропроцессоров.Известно микропрограммное устройство управления, построенное с использованием памяти микропрограмм и содержащее регистр адреса микрокоманд, матрицу памяти и регистр микрокоманд. 1 В соответствии с кодом регистра адреса из памяти микропрограмм на регистр выбираются коды микрокоманд. Каждая микрокоманда состоит из операционной и адресной частей. Операционная часть 15 формирует микроприказы, управляющие вентилями процессора, а адресная- адрес следующей микрокоманды. Послед.ний в общем случае зависит от кода команды или признаков условий пере хода, сформированных при выполнении этой или предыд,щих микрокоманд, В качестве памяти микропрограмм исполь-зуется обычно пассивное запоминающее 2устройство или программируемая логическая матрица 1 .Недостатком данного устройства является большой объем памяти микропрограмм при реализации достаточно мощной системы команд либо ограниченные функциональные возможности при удовлетворении требованиям, ограничивающим объем оборудования, что становится особенно существенным при пост рое. нии однокристальных микропроцессоров и приводит к жестким ограничениям мощности реализуемых в них. систем команд.Наиболее близким техническим решением к предлагаемому является микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса микрокманд, регистр микрокоманд,первую группу элементов И, первую и вторую группы элементов, ИЛИ, первые входы элементов ИЛИ первой группы являются входом команд устройства, вторые входы - входом3 94372 условий устройства, информационные входы элементов И первой группы соединены с выходами элементов ИЛИ первой группы, а выходы - с первыми входами элементов ИЛИ второй группы, первый выход которой соединен со входом регистра адреса микрокоманд, выходом соединенного с адресным. входом блока памяти микрокоманд, первый, второй и третий выходы которого соединены с 16 соответствующими входами регистра микрокоманд 2 .Основными недостатками устройства являются большой объем блока памяти микропрограмм и ограниченные Функцио нальные возможности, заключающееся в том, что устройство реализует лишь набор микропрограмм, существенно ограниченный объемом блока памяти.Цель изобретения - расширение Функциональных возможностей устройства за счет структурно-микропрограммной реализации внешнего микро- программирования.г 5Поставленная цель достигается тем, что устройство содержит вторую, третью, четвертую, пятую, шестую, седьмую и восьмую группы элементов И, третью группу элементов ИЛИ, триггер30 блокировки, регистр адреса внешних микрокоманд, регистр сигналов управ-. ления, первыми выходами соединенный с первыми входами элементов И второй группы, выходами соединенных со вторыми входами элементов ИЛИ второй группы, управляющие входы элементов И первой группы соединены с выходами элементов И третьей группы, первые выходы регистра микрокоманд соединены с первыми входами элементов И49 четвертой группы, выходы которых соединены с третьими входами элементов ИЛ 1 второй группы, вторые входы элементов И четвертой группы соединены с первыми входами элементов И третьей группы, с единичным выходом триггера блокировки и с первыми вхо" дами элементов ИЛИ третьей группы, выходы которых соединены с управляющими входами соответствующих элемен тов И пятой группы, информационными входами соединенных с четвертыми выходами блока памяти микрокоманд, а выходами - с четвертым входом регистра микрокоманд, вторые входы эле ментов И третьей группы соединены с соответствующим вторым выходом регистра микрокоманд, третьи входы элементов И третьей группы соединены со вторыми входами соответствующих элементов И шестой группы и со вторым "выходом регистра сигналовуправления, третий выход которогосоединен со вторыми входами элементов И шестой группы и с первыми входами элементов И седьмой группы, выходами соединенных с четвертыми входами элементов ИЛИ второй группы, первые входы элементов И восьмой группы соединены с выходами элементов ИЛИ второй группы, а выходыс первым информационным входом регистра адреса внешних микрокоманд, второй информационный вход которого соединен с выходом шестой группыэлементов И, третий выход регистрамикрокоманд соединен с соответствующими управляющими входами триггера блокировки, регистра адреса внешних микрокоманд, регистра. сигналов управления, элементов И второй, шестой, седьмой и восьмой групп, четвертый выход регистра микрокоманд является выходом устройства, выход регистра адреса внешних микрокоманд является адресным выходом устройства дпя внешней памяти микропрограмм, а управляющие входы регистра сигналов управления являются входами внешних микропрограмм устройстваНа чертеже 1 представлена блоксхема устройства, в которой содержится блок памяти микрокоманд 1, регистр микрокоманд 2, регистр адреса микро- команд 3 первая 4, вторая 5. третья 6, четвертая 7, пятая 8, шестая 9 седьмая 10 и восьмая 11 группы элементов И, первая 12, вторая 13 и третья 14 группы элементов ИЛИ, регистр адреса внешних микрокоманд 15, регистр сигналов управления 16, триггер блокировки 17Устройство работает следующимобразом. По внешнему сигналу в регистрах 3 и 15 устанавливаются начальные адреса, в регистре 16 и триггере 17- нулевые состояния, При этом на нулевых выходах регистра 16 и нулевом выходе триггера 17 устанавливаются потенциалы, открывающие элементы И 7, И 8 и разрешающие прохождение через элементы И 6 на управляющие входы элементов И 4 микроприказов условий с выходов регистра 2.По начальному коду регистра 3 ( в общемслучае отличному от нулевого) с выходов блока памяти микрокоманд 1 снимается и записывается в регистр 2 код микрокоманды, реализующей чтение из внешней памяти и интерпретацию команды. Микрокоманда на регист". ре 2 состоит из основных и дополнительных микроприказов, микроприказов условий и базового адреса группы сле о дующих микрокоманд, Дополнительные микроприказы в микрокомандах, реализующих основные команды процессора, не вырабатываются. В соответствии с основными микроприказами читается из внешней памяти и подается на первый вход первой группы элементов ИЛИ код команды. Иикроприказы условий открывают соответствующие элементы И 1. Адрес следующей микрокоманды Форо мируется, например, логическим сложением разрядов команды, прошедших через открытые элементы И ч, и кода базового адреса с выходов элементов И 7. Сформированный адрес записывается в регистр 3 и является адресом первой внутренней микрокоманды исполнительной части одной из основных команд или адресом внутренней микро- команды, интерпретирующей внешнюю микрокоманду, Одна или несколько следующих микрокоманд могут продолжать интерпретацию команды, ветвясь в микропрограмме с помощью описанного механизма формирования адреса по коду35 в разрядах команды, прошедших через элементы И 1, и коду адреса, указанного в текущей микрокоманде.После окончания интерпретации команды устройство переходит к выполне 40 нию внутренней микропрограммы, содержащейся в блоке памяти 1, либо к выполнению микропрограммы, записанной во внешней памяти.При выполнении внутренней микропрограммы исполнительной части одной4 Я из основных команд работа устройства по существу не отличается от работы известных микропрограммных устройств управления и происходит аналогично описанной при интерпретации команды.При переходе к выполнению интерпретации внешней микрокоманды в регистре адреса 3 устанавливается нулевой код адреса, в соответствии с которым в регистр 2 записывается код микрокоманды содержащей базовый адрес группы следующих микрокоманд, основные микроприказы и дополнитель 27 6ный микроприказ. В соответствии сосновными микроприказами выполняется чтение внешней микрокоманды извнешней памяти по адресу, указанному на регистре 15, и запись ее врегистр сигналов управления 16. Дополнительный микроприказ устанавли-. вает триггер блокировки 17 в нулевоесостояние, увеличивает содержимоерегистра 15, например, на единицумладшего разряда и открывает элементы И 5.Адрес следующей микрокоманды формируется из адреса, содержащегосяв текущЕй микрокоманде, и кода внешней микрокоманды, поступающих соответственно с выходов открытых элементов И 7 и 5, и записывается в регистр 3.функциональные возможности микропрограммного устройства управлениярасширены за счет структурно-микропрограммной реализации внешнего микропрограммирования, использующеговнутренние микропрограммы как библиотеку микрокоманд и наделенного средствами ее расширения. Внутренняя мик-.ропрограмма, кроме того, с помощьюструктурных средств интерпретируетвнешние микрокоманды и реализуетвзаимодействие внутреннего и внешнего микропрограммирования.Формула изобретенияИикропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса микрокоманд, регистр микрокоманд,первую группу элементов И,первую и вторую группы элементов ИЛИ, первые входы элементов ИЛИ первой группы является входом команд устройства, вторые входы - входом условий устройства, информационные входы элементов И первой группы соединены с выходами элементов ИЛИ первой группы, а выходы - с первыми входами элементов ИЛИ второй группы, первый выход которого соединен с вхьдом регистра адреса микрокоманд, выходом соединенного с адресным входом блока памяти микрокоманд, первый, второй и третий выходы которого соединены с соответствующими входами регистра микрокоманд, о т л и ч а ю щ е ес я тем, что, с целью расширения .Функциональных возможностей за счет структурно-микропрограммной реализа 943727ции внешнего микропрограммирования,оно содержит вторую, третью, четвер"тую, пятую, шестую, седьмую и восьмуюгруппы элементов И,.третью группу элементов ИЛИ, триггер блокировки, регистр адреса внешних микрокомандрегистр сигналов управления, первыми выходами соединенный с первыми входами элементов И второй группы, выходами соединенных с вторыми входами Оэлементов ИЛИ второй группы, управляющие входы элементов И первой группысоединены с выходами элементов И третьей группы, первые выходы регистрамикрокоманд соединены с первыми входами элементов И четвертой группы,выходы которых соединены с третьимивходами элементов ИЛИ второй группы,вторые входы элементов И четвертойгруппы соединены с первыми входами 20элементов И третьей группы, с единицным выходом триггера блокировкии с первыми входами элементов ИЛИтретьей группы, выходы которых соединены с управляющими входами соответст.25вующих элементов И пятой группы, информационными входами соединенных сче т ве рт ым и в ыходам и блока пам ят имикрокоманд, а выходами - с четвертым входом регистра микрокоманд, вто- ЗОрые входы элементов И третьей группы соединены с соответствующим вторым выходом регистра микрокоманд,третьи входы элементов И третьейгруппы соединены с вторыми входамисоответствующих элементов И шестой группы и с вторыми выходами регистра сигналов управления, третий выходкоторого, соединен с вторыми входамиэлементов И шестой группы и с первыми входами элементов И седьмой группы, выходами соединенных с четвертыми входами элементов ИЛИ второйгруппы, первые входыэлементов Ивосьмой группы соединены с выходамиэлементов ИЛИ второй группы, а выходы - с первым информационным входом регистра адреса внешних микрокоманд,второй информационный вход которого соединен с выходом шестой группыэлементов И, третий выход регистрамикрокоманд соединен с соответствующими управляющими входами триггераблокировки, регистра адреса внешнихмикрокоманд, регистра сигналов управленив, элементов И второй, шестой,седьмой и восьмой групп, четвертыйоыход регистра микрокоманд являетсявыходом устройства, выход регистраадреса внешних микрокоманд являетсяадресным выходом устройства для внешней памяти микропрограмм, а управляющие входы регистра сигналов управления являются входами внешних микропрограмм устройства. Источники информации,принятые во внимание при экспертизе 1. Булей Г."Микропрограммирование","Мир", 1973 с, 14- 15. 2. "Электроника" 6 6, 1974,с, 50-57 (прототип ),Составитель В. ЕвстиТехреду М. РейвесТираж /31 н в Раушская филиал ППП Патент, г. Ужгород, ул Заказ 5111/56ВНИИПИ Г по де035, Ио ударствен ам изобре ква, Жго комитет ний и откр КорректорУ. ПодписноеССР д ч/5Проектная,ом

СмотретьЗаявка

2479572, 26.04.1977

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР, ПРЕДПРИЯТИЕ ПЯ Х-5263

ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, ДРЯПАК АНАТОЛИЙ ФЕДОРОВИЧ, КУРГАЕВ АЛЕКСАНДР ФИЛИППОВИЧ, ДЕНИСЕНКО ЕВГЕНИЙ ЛЕОНИДОВИЧ, ПРЯДИЛОВА АННА АЛЕКСЕЕВНА, КУЗНЕЦОВ ВЛАДИМИР ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06F 9/46

Метки: микропрограммное

Опубликовано: 15.07.1982

Код ссылки

<a href="https://patents.su/5-943727-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для управления памятью

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ выращивания картофеля