Последовательный двоично-десятичный сумматор-вычитатель

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

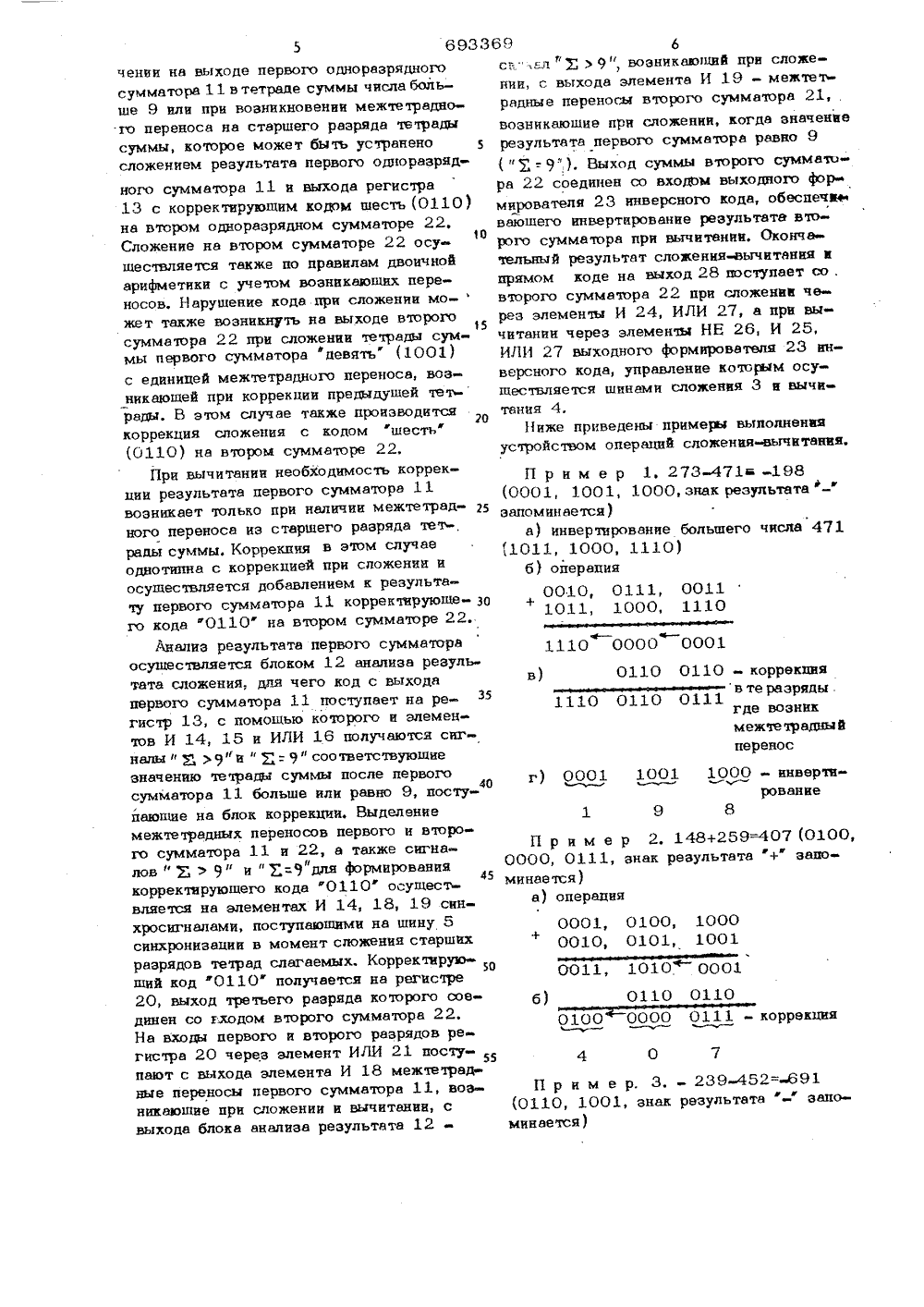

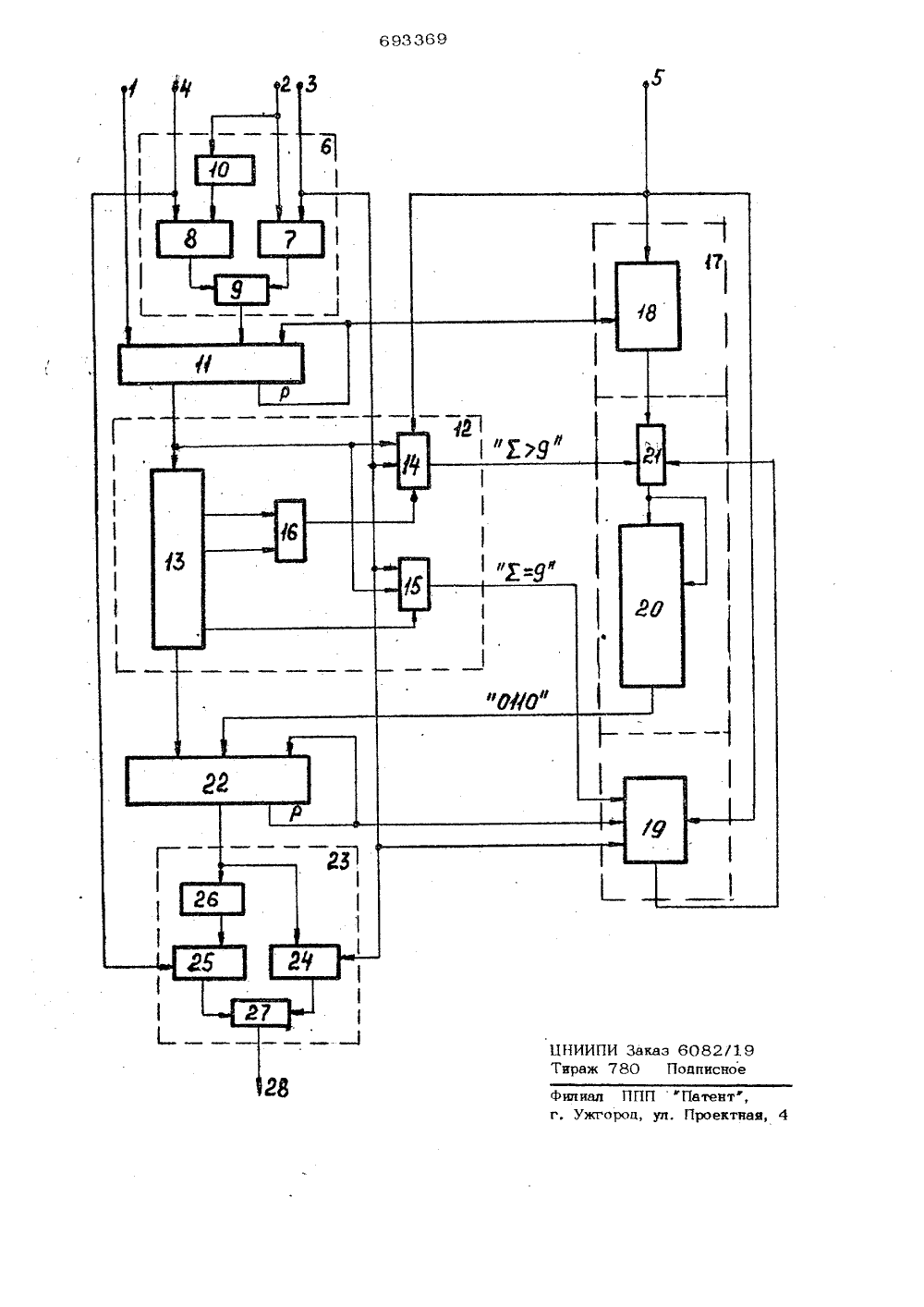

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах для сложения-вычитания двоично-десятичных кодов.Известны устройства для сложения-вы 5 читания двоично-десятичных кодов, в которых операция вычитания реализуется без перевода отрицательного числа в дополнительный код, а с использованием формиро 1 О вателей инверсных кодов и схем коррекции, позволявших производить операции над десятичными числами по правилам дво ичной арифметики с применением соотвев-. ствуюших корректируюших кодов 11 К В ечих устройствах применены входные в выходные блоки инвертирования кодов, первый и второй сумматоры, схемы коррекции и формирования межтетрадиых переносов. Указанные устройства предназна- о чены для сложения-вычитания чисел, представленных двоично десятичным параллельным кодом, их реализация требует большого объема оборудования. и затрудняет использование в арифмещческих устройствах посл Ъдовательного действия.Наиболее близким по технической супь ности к предлагаемому является последовательный двоично-десячачный сумматор вычитатель, содержащий первый и второй одноразрядные сумматора, входной форми рователь инверсного кода, блок анализа результата сложения и блок коррекции, причем вход входного формирователя инверсного кода подключен к шине одйого из операндов, управляюшие входы к шинам сложения и вычитания,.а выход ко входу первого одноразрядного сумматора, другой вход которого соединен с шиной другого операнда, а выход со входом блока анализа результата сложения, уп равляюшие входы которого соединены с шинами сложения и синхронизации, а выход - со входом второго одноразрядного сумматора, другой вход которого соединен с выходом блока коррекции, первый вход которого подключен к выходу пере носа первого одноразрядного сумматора, 3 693второй вход - к выходу блоке анализа результата сложения, в третий и четвер ыйвходы - к шинам сложения и синхронизации 31.Недостатком данного устройства являются то что В нем используючся двв типа корректирующих кодов: 0110" присложении и 1010 при вычитании, формирование которых осуществляется схемой коррекции с использованием триггера 10и алеманив И, ИЛИ, требующей для управления ее работой четырех синхронизируюших сигналов, сдвинутых во времени.Кроме тогопри вычитании Окончательныйрезультат с выхода второго сумматора 15отличается на единицу младшего десятичйого разрядв от действительного значенияразности, твк квк используется инверсный,а не дополнительный код отрицательногочисла, Поэтому использование этого сум- Омвтора-вычитателя в арифметических устройствах требует дополнительной коррек=ции результата второго сумматора при вычитании, а также дополнительной схемытипа регистра сдвига для формированиясдвинутых во времени синхронизируюшихСИГНВПОВ.Целью настоящего изобретения является упрощение устройства,Для достижения поставленной цели,сумма щр- вычитатель содержит выходнойформирователь инверсного кода, вход кото"рого подключен к выходу второго одноразрядного сумматора,управляющие входыК шинам сложения, и вычитания, в выхрдк выходу сумматора-вычитвтеля, пятыйи шестой входы блока коррекции подключены соответственно ко второму выходу блока анализа результата сложения к выходу40переноса второго одноразрядного суммафйфа.Кроме того, блок коррекции содержитэлементы И и ИЛИ и регистр сдвига, входы первого и вчорого разрядов которого45подключены к выходу элемента ИЛИ, входЫ которого подключены к выходам первого и второго элементов И и второмувходу блока коррекции, первый вход которого подключен к первому входу первогоэлемента: И, второй вход которого соединен с четвертым входом блока коррекции,входы второго элемента И соединены стретьим, четвертым, пядям и шестым входами блока коррекции, к выходу которогоподключен выход регистра сдвига.На чертеже изображена схема предлагаемого последовательного двоично-десятичного сумматора Вычитателя,369 4Устройся содержит Входы 1 и 2 для подачи слагаемых, шины сложения 3 и вычитания 4, шину 5 синхронизации для подачи синхронизируюших импульсов с целью выделения межтетрвдных переносов, входной формирователь 6 инверсного кода, выполненный на элементах И 7 и 8, ИЛИ 9, НЕ 10, выход которого соединенсовходом первого одноразрядного Сумматора 11, с выходом суммы которого соединен вход блока 12 анализа результата сложения, выполненный на четырехразрядном регисъре 13 сдвига и алементах И 14 и 15, ИЛИ 16. Другие входы блока 12 анализа результата сложения соединены с шиной 3 сложения и шиной 5 синхронизации.Выходы блока 1 2 анализа результата сложения соединены со входами блока 17 коррекции выполненного на алементах И 18 и 19 и трехразрядном регистре 20 сдвига и элемента ИЛИ 21. Входы элемента И 18 соединены с выходом переноса первого одноразрядного сумматора 11 и шиной 5 синхронизации, а входы элемента И 19 соединены,с шиной 3 сложения шиной 5 синхронизации, выходом "Е:9 "блока 12 анализа результата. Выходы элементов И 18 и 19 соединены со входом регистра 20 сдвига через элемент ИЛИ 2.1, вход которого соединен также с выходом "9 " блока 12 анализа результатаэ Выход регистра 20 сдвига блока коррекции 17 соединен со входом второго одноразрядного сумматора 22, выход переноса которого соединен СО входом алемента И 19 а выход суммы - со входом выходного формирователя 23 инверсного кода, содержащего элементы И 24 и 25, НЕ 26, ИЛИ 27, выход 28 выдачи Окончательного результата.Два числа в прямом последовательнодвоично-десятичном коде поступают на входы 1 и 2. При одинаковых знаках обо их слагаемых (плюс ипи минус) на управляющей шине сложения 3 устанавливается уровень "1, и сложение в первом однорвзрЯдном сумматоре 11 производится В прямых кодах по правилам двоичной ариф метики с учетом возникающих переносов.При разных знаках слагаемых уровень 1 устанавливается на шине вычитателя 4 и большее по абсолютной. величине слагаемое подается на вход 2, в результаж чего на вход первого суммачора 11 оно посту пает в инверсном коде,При сложении может иметь место нарушение двоично-десятичного кода при поду1110 0000 0001 г) 0001 1001 1000 - инвертирование8 П р и м е р 2. 148+259=407 (0100,0000, 0111, знак реаультатв + запо 45 минае тся )а) операция 0001, 0100, 1000 0010, 0101, 1001 0011, 1010 ф 0001 0110 0110 б) 0100 чении на выходе первого одноразрядного сумматора 11 в тетраде суммы числа больше 9 или при возникновении межтетрвдного переноса на старшего разряда тетрады суммы, которое может быть устранено сложением результата первого одноразрядного сумматора 11 и выхода регистра 13 с корректирующим кодом шесть (0110) на втором одноразрядном сумматоре 22. Сложение на втором сумматоре 22 осу 10 шествляется также по правилам двоичной арифметики с учечом воэниквюших переносов. Нарушение кода при сложении мо-жет также возникнуть на выходе второго5 сумматора 22 цри сложении тетрвды суммы первого сумматора девять" (1001) с единицей межтетрадного переноса, возникающей при коррекции предыдущей тетрады. В атом случае также производится20 коррекция сложения с кодом "шесть (0110) на втором сумматоре 22,При вычитании необходимосчь коррекции результата первого сумматора 11 возникает только при наличии межтетрад ного переноса из старшего разряда тетрады суммы. Коррекция в этом случае однотипна с коррекцией при сложении и осуществляется добавлением к результату первого сумматора 11 корректируюше- з 0 го кода 0110 на втором сумматоре 22.Анализ результата первого сумматора осушеспьляется блоком 12 анализа результата сложения, для чего код с выхода первого сумматора 11 поступает на регистр 13, с помощью которого и элементов И 14, 15 и ИЛИ 16 получаются сигналыЕ" и : " соответствуюшие значению течрвды суммы после первого сумматора 11 больше или равно 9, посту 40 йаюшие на блок коррекции, Выделение межтетрадных переносов первого и второго сумматора 11 и 22, а также сигналов " у, ъ " и =9 для формирования корректирующего кода 0110 осуществляется на элементах И 14, 18, 19 синхросигналами, поступающими на шину 5 синхронизации в момент сложения старших разрядов тетрад слагаемых. Корректирую 50 ший код ф 0110" получается на регистре 20, выход третьего разряда которого соединен со входом второго сумматора 22. На входы первого и второго разрядов регистра 20 через элемент ИЛИ 21 посту пают с выхода элемента И 18 межтетрадные переносы первого сумматора 11, возникающие при сложении и вычитании, с выхода блока анализа результата 12 с;". л ";9", возникающий при сложении, с выхода элемента И 19 - межтет радные переносы второго сумматора 21,возникающие при сложения, когда аначениерезультата первого сумматора равно 9( "Е = 9"). Выход суммы второго суммарнора 22 соединен со входом выходного формирователя 23 инверсного кода, обеспечямваюшего инвертирование результате второго сумматора при вычитании. Окончательный результат сложения-вычитания кпрямом коде на выход 28 поступает со .второго сумматора 22 при сложении через элементы И 24, ИЛИ 27, а при вычитании через элементы НЕ 26, И 25,ИЛИ 27 выходного формирователя 23 инверсного кода, управление которым осуществляется шинами сложения 3 и вычитания 4,Ниже приведены примеры выполненияус тройством операций сложения-вычитания. П р и м е р 1, 273-471 и -198 (0001, 1001, 1000, знак результата -ф запоминается )а) инвертирование большего числа 471 (1011, 1000, 1110)б) операция0010, 0111, 00111011, 1000, 1110 0110 0110 - коррекпня0110 0111где возникмежте традны йперенос 0000 0111 - коррекция П р и м е р. 3. - 239-с 52=-691а) Операция0010, 0011, 1001о 11 о, 1 ооо, 1 о 110110 - коррекция0110, 1001, 0001Использование в данном последователь= ном двоично-десятичном сумматоре-вычитатеде одного типа корректируюшего кода 0110" при сложении-вычитании и учет двоичных переносов в первом и втором сумматорах позволяет упрос пть схему сумматора-вычитателя по сравнению с известным за счет уменьшения числа элементов в блоках коррекции и формирования межтетредных переносов, так как при данном типе коррекции не требуются элементы для игнорирования межтетрадных пере-, носов от коррекции на втором сумматоре и элементы для коммутации различных 25 корректируюших кодов при сложении-вычитании. Кроме того, реализация блока коррекции в данном устройстве не двух элементах И, элементе ИЛИ и трехразрядном регистре сдвига, не уменьшая быстродей- зз ствия блока коррекции по сравненио с из-.- вестным ус:ройством, пс воляет упрос:.ить устройство зе счет жго, что для управ-.ления его работой необходим один синхронизируюший сигнал, а на четыре срвину тых во времени сигцеле (прототип)для формирования которых требуется дополнительная схема типе регистра сдвига, Вве= дение в схему сумматоре-вычитателя выходного формирователя инверсного кода помимо однотипности коррекции позволяет получить правильный окончательный результат без дополнительного учета единицы младшего десятичного разряда при вычитании, чпэ расширяет функциональные Возможности устройства, пОскольку п 1 эед= лагаемый сумматор-вычитатель выполняет функцию, о гсутствуюшую в прототипе, но необходимую в арифметическом устрой- стве для получения правильного резуль.= тата.ФОрмуле изобретения551 ф Послещэветельный двОично,десятич ный сумматор-аычита лиьсодержешг й первый и Второй Одноразрядные сумматоры,входной формирователь инверсэюго кода,блок анализа результата сложения и блоккоррекции, причем вход входного формирователя инверсного кода подключен к шине Одного из операндов, упревляюшие Вхофдд- к шинам сложения и вычитания, авыход ко входу первого однорезряпногосумматора, другой вход которого соединенс шиной другого операнда, е выход - совходом блока анализа результата сложенияуправляюшие входы которого соединены сшинами сложения и синхронизации, а выход - со входом второго одноразрядногосумматора, другой вход которого соединен с выходом блока коррекции, первыйвход которого подключен к выходу переноса первого одноразрядного сумматора,второй вход - к выходу блока анализа результата сложения, а третий и четвертыйвходы - к шинам сложения и синхронизации, о т л и ч а ю ш и й с я тем, что,с целью упрошения сумматора-вычитателя,он содержит выходной формирователь инверсного кода, вход которого подключенк выходу второго одноразрядного сумматора, упревляюшие входы - к н 1 инам сложения и вычитания, а выход - к выходусумматора-вычитателя, пятый и шестойвходы блока коррекции подключены соответственно ко второму выходу блока анализа результате сложения и выходу первносе второго одноразрядного сумматора.2. Сумматор-вычитатель по п, 1, о тл и ч а ю ш и й с я тем, что блок коррекции содержит элементы И и ИЛИ и регистр сдвига, входы первого и второгоразрядов которого подключены к выходуэлемента ИЛИ, входы которого подключенык выходам первого и второго элементовИ и второму входу блока коррекции, перьый вход которого подключен к первомувходу первого элемента И, второй входкоторого соединен с четвертым входомблока коррекции, входы второго элементаИ соединены с третьим, четвертым, пятым и шестым входам блока коррекции,к выходу которого подключен выход регистре сдвига.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРХ 332459, кл. 6,06, Р 7/50, 1972.2, Авторское свидетельство СССРМ 393740, кл. 6 06 Е 7/50, 1973.3. Авторское свиде тельсчво СССР Мв 387364, кл. О 06 Г 7/50, 1973 (прототип).

СмотретьЗаявка

2500392, 27.06.1977

ПРЕДПРИЯТИЕ ПЯ А-3759

МЫМРИКОВ ВЛАДИМИР ВЛАДИМИРОВИЧ, ШВЕЙКО НИНА ПЕТРОВНА

МПК / Метки

МПК: G06F 7/385

Метки: двоично-десятичный, последовательный, сумматор-вычитатель

Опубликовано: 25.10.1979

Код ссылки

<a href="https://patents.su/5-693369-posledovatelnyjj-dvoichno-desyatichnyjj-summator-vychitatel.html" target="_blank" rel="follow" title="База патентов СССР">Последовательный двоично-десятичный сумматор-вычитатель</a>

Предыдущий патент: Арифметико-логическое устройство

Следующий патент: Устройство для вычитания

Случайный патент: Устройство для вращения магнит-ного диска