Накапливающий сумматор с коррекцией ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 647685

Авторы: Петряшов, Толстохатько, Трофимов

Текст

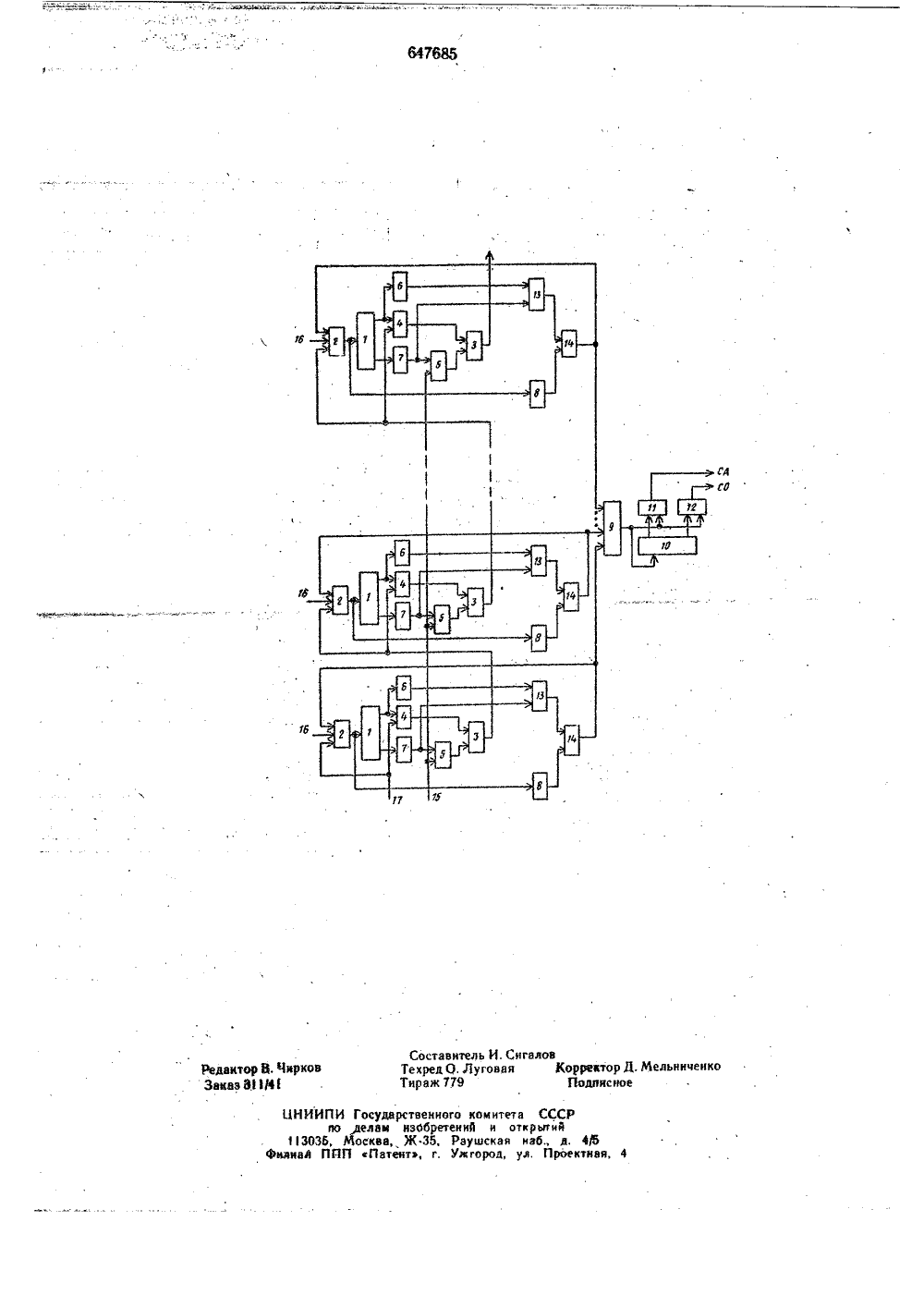

(61) Дополнительное к авт. свид-ву 7.02.77 (21) 2450978/18-2 22) Зая 6 Р,73806 Ф 11/00 ГКУРРСтвееЮ иаетв СССР е доь хзФрове 1 н юРмтФ3) Приорите Опублико ллетеиь 6 ия 20.02.79 вно 15.О 2.791) ЙАКАППИВАЮВИЙ СУММАТОР С КОРРЕКЦИЕЙ ОШИБОК 1Изобретение относитсяк области вычислительной техники и может быть использовано в цифровых вычислительных машинах.Известен накапливающий сумматор с коррекцией ошибок, содержащий п схем суммирования, схему контроля по модулю 3, 5 схему коррекции, схему управления коммутацией и элементы И и ИЛИ , Не. достаток известного устройства состоит в том, что сигналы коррекции зависят от информации, вырабатываемой схемой контроля отчетности номера разрядной схемы, коррекция осуществляется сложной схемой управления коммутацией.Из известных устройств наиболее близким техническйм решением к предлагаемому изобретению является накапливающий сум- В матор с коррекцией ошибок, содержащий в каждом разряде триггер со счетным входом, первый, второй и третий элементы ИЛИ, первый и второй формирователи импульсов, элемент задержки, первый н второй элементы И, блок сравнения, четвертый элемент ИЛИ, триггерфиксации ошибок, третий и четвертый элементы И, причем выход пер. ного элемента ИЛИ каждого разряда сое. динен со счетным входом триггера, единичный выход каждого триггера соединен с первым входом первого элемента И и со входом первого формирователя импульсов; выход которого соединен с первым входом второго элемента ИЛИ, нулевой выход каждоготрнггера соединен со входом второго формирователя импульсов, выход которого соединен первым входом второго элемента И и со вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом блока сравнения, второй вход которого соединен с выходом элемента за. держкн, выходы первого н второго элементов И соединены с первым и вторым входом третьего элемента ИЛИ, выход третьего эле. мента ИЛИ каждого разряда сумматора сое. динен с первым входом первого элемента ИЛИ н вторым входом первого элемвнта И следующего старшего разряда сумматора, вторые входы первых элементов ИЛИ образуют первую группу входов устройства второй вход второго элемента И всех разрядов соединен с управляющим входом устрой. ства, выход каждого. блока сравнения соединен с третьим входом первого элемента ИЛИ каждого разряда и со входом четвер того элемента ИЛИ, выход которого соеди647685неи с единичным входом триггера фиксацииошибок и с первыми входами третьего ичетвертого элементов И, вторые входи кото.рых соединены соответственнос нулевым иединичным выходом триггера фиксации оши збок, выходы третьего и четвертого элементов И соединены соответственно с первым ивторым выходом устройства Щ.Недостатком известного устройства является его сложность,Целью изобретений является экономия 1 фоборудования. Поставленная цель достигаетсятем, чта в каждом разряде выход пер.вого элемента ИЛИ соединен са входом эле.мента задержкиСтруктурная схема предлагаемого сумматара приведена на чертеже.В предлагаемом сумматоре каждый разряд содержйт счетный триггер 1, первый итретий элементы ИЛИ 2 и 3, первый и второй элементы И 4 н 5, формирователи импульсов 6 и 7, элемент задержки 8, четвертый элемент ИЛИ 9, триггер 1 О фиксацииошибок, третий и четвертый элементы И 11и 12, второй элемент ИЛИ 13, блок сравнения 14, шину 15 запрета павтбрнага переноса, управляющий вход устройства,Счетный вход счетного триггера 1 каждого разряда подключен к выходу первогоэлемента ИЛИ 2, входы которого подсоединены к входной шине 16, шине выходаперепаса из предыдущего разряда 17 иквыходу блока сравнения 14, Единичный выход счетного триггерасоединен со входомформирователи импульсов б и с первымвходом первого элемента И 4, ка второмувходу которого подключена шина выходапереноса из предыдущего разряда 17.Нулевой выход счетного триггера 1 соединен со входом второго формирователя имтульсов 7, выход которого подключен к перюму входу второго элемента И 5, второйзход которого соединен с шиной. запрета повторного переноса 15; Выходы элементовИ 4 и 5 подключены к входам третьего эле" -мента ИЛИ 3 выход которогасоединен свиной выхода. переноса в последующий раз)ил. В каждом разрядевыходы формирователей импульсов 6 и 7 соединены с перзым и вторым входами второго элементаИЛИ 13, выходкарого подключен к пер-вому входу блока сравнения 14, второй входкоторого подсаедиией к выходу элеМента за держки 8, входкоторого непосредственносоединен со счетным входом счетного триггера 1 соответствующего разряда. бок), либос выхода третьего элемента ИЛИ 3 предыдущего разряда (сигнал перепаса). ц С выхода элемента ИЛИ 2 сигнал наступает на счетный вход счетного триггера 1 и иа вход элемента задержки 8 этого разря, да, который рассчитан на сумму времен срабатывания счетного триггера, элемента ИЛИ" и формирования импульсов.ф Если при поступлении единичного сигнала счетный триггер 1 срабатывает (изменяет свае состояние на противоположное), то на выходе одного из формирователей импульсов 6 и 7 сформируется сигнал требуемой полярности,который через второй элемент ИЛИ 13 узла коррекции ошибок поступает на первый вход блока сравнения 14 данного раз.- ряда, На второй вход этого же блока сравнения 14 через элемент задержки 8 паступа-""ег едйничный сигнал са счетного -входа 36 счетного триггера 1, При этом на выходеданного блока сравнения 14 сигнал не образуется и, следовательно, будет отсутствоватьсигнал Ошибка (СО) на выходе эле- .мента И 12.35Если при поступлении единичного сигнала. счетный триггер 1 ие сработает, то на выходах формирователей импульсов 6 и 7 сигнал ие формируется; В этом случае на первом входе блока сравнения И сигнал отсутствует, а на его второй вход поступит задержанный единичный сигнал, который приводит к йоявлению сигнала иа выходе блока сравнения 14. Единичный сигнал с выхода этого блока сравнения 14 поступит иа. вход первого элемента ИЛИ. 2 рассматриваемого разряда и иа саатветствую щий вход четвертого элемента ИЛИ 9. Сигнал с выхода элемента ИЛИ 9 одновременно вьщается иа вторые входы элементов И 11, 12 и на вход записи единицы в триггер фиксации ошибок. В результате эгаго на выходе элемента И 12 образуется сигнал,который свидетельствует о наличии ошибкипри суммироваиии чисел, Одновременно сигнал с выхода элемента 14 (сигнал коррекции) поступает через первый элемевг ИЛИ 2иа счетный вход счетиага триггера 1, в код тором зафиксирована ошибка, и через элемент ИЛИ 2 - на вход элемента задержки 8 1 для контроля коррекции),Если ошибка скорректирована, то иа обавхода соответствующего блока сравиеиия И Кроме того, вЫхады блоков сравнения 14 сех подключены ко входам четвертого элемента ИЛИ 9, выход которого соединен с диничным входом триггера фиксации ошиок 10 ивторыми входами элементов И 1112, первые входы каторйх подключены к %иничиому и нулевому выходам триггера иксации ошибок 10 соответственна. Сиг 4палы аварии и ошибка снимаются с выходов элементов И 11, 12 соответственно.Так как все разряды предлагаемого сумматора выполнены идентично, то рабату устройства рассмотрим иа примере одного разряда,Перед началом работы в сумматоре может содержаться результат предыдущей операции, на триггер фиксации ошибок устанавливается в нулевое состояние, На вход первого элемента ИЛИ 2 постуйает единичный сигиал либо со входа 16, либо с выхода блока сравнения 14 (сигнал коррекции ашиодновременно поступят сигналы с выходаэлемента ИЛИ 13 и с выхода элемента задержки 8. В этом случае на выходе блокасравнения 14 и на выходе элемента И 12сигналы отсутствуют.Если же ошибка не скорректировалась,то на входе рассматриваемого блока сравнения 14 повторно образуется единичныйсигнал, который через четвертый элементИЛИ 9 подается на входы элементов И 11и 12, Поскольку триггер фиксации ошибок10 находится в единичном состоянии, тона выходе элемента И 11 образуется сигналАвария (СА),Таким образом, в отличие от прототипа,предлагаемое устройство при меяьшем коли.честве оборудования обладает большими возможностями по обнарунсецию и коррекцииошибок при суммировании числа, благодарячему повышается надежность работы устройства,Формула изобретенияНакапливающий сумматор с коррекцией ошибок, содержащий в каждом разряде три- гер со счетным входом, первый, второй и третий элементы ИЛИ, первый и второй формирователи импульсов, элемент задержки, =плервйй и,втоРай элементы И, блок сРавиенивце четвертый элемент ИЛИ, триггер фиксации ошибок, третий и четвертый элементы И, причем выход первого элемента ИЛИ каждого разряда соединен со счетным входом триггера, единичный выход каждого триггера соединен г первым входом первого элемента И и со входом первого формирователя импульсов, выход которого соединен с первым входом второго элемента ИЛИ, цулевой выход каждого триггера соединен со входом второго формирователя импульсов, выход которого соединен с первым входом второго элемента И со вторым входом вто рого элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом блока сравнения; второй вход которого соединен с выходом элемента задержки, выходы первого и второго элемента И соединены с пер вым и вторым входом третьего элементаИЛИ, выход трегьего элемента ИЛИ каждого разряда сумматора соединен с первым входом первого элемента ИЛИ в вторым входом первогоэлемента И следующего старшего разряда сумматора, вторые входыпервых элементов ИЛИ образуют первую группу входов устройства, второй вход второго элемента И всех разрядов соединен с управляющим входом устройства, выход каждого блока сравнения соединен с третьим входом первого элемента ИЛИ каждого разряда и со входом четвертого элемента ИЛИ, выход которого соединен с единя шым входом фиксации ошибок и с первыми входами третьего ц четвертого элементов И, вторые входы которых соединены соответственно с 25 нулевым и единичным вуходом триггера фиксации ошибок, выходы третьего и четвертого элементов И соединен соответственно с первым ц вторым выходом устройства, отличшо-итилиси тем, ито о целью экономии одрудо.иииии, и кииьдоаю риэриде оьтхтудитириого эле.мента ИЛИ соединен со входом элемента задержки.Источники информации, принятые во внимание при экспертизе. Авторское свидетельство СССР 35 ,Иф 358697 сл Ср 06 Г 7/50 9722. Авторское свидетельство СССР226270, кл. б 06 Г 7/50, 968.гб Г 4 гб гб игал ко осударствеиного комителам изобретений иоскеа, Ж 35, Раушска аПатентэ, г, Уагороа 0 НИИПИзозь, lФилиал ППП Редактор В. Ч Заказ Щ 81 Составитель ИТехред О. ЛуговТираж 779 Корректор Д. Мельииченк Подпяс иое ета СССР отиритиВнаб., д. 45 ул. Проектная,

СмотретьЗаявка

2450978, 07.02.1977

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ ОРДЕНА ОТЕЧЕСТВЕННОЙ ВОЙНЫ АКАДЕМИЯ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

ПЕТРЯШОВ ВЛАДИМИР МИХАЙЛОВИЧ, ТОЛСТОХАТЬКО ВИКТОР АНТОНОВИЧ, ТРОФИМОВ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: коррекцией, накапливающий, ошибок, сумматор

Опубликовано: 15.02.1979

Код ссылки

<a href="https://patents.su/4-647685-nakaplivayushhijj-summator-s-korrekciejj-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Накапливающий сумматор с коррекцией ошибок</a>

Предыдущий патент: Устройство для извлечения квадратного корня

Следующий патент: Устройство для умножения

Случайный патент: Эквивалентный материал для моделирования литосферы