Цифровой демодулятор сигналов фазоразностной модуляции первого и второго порядка

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1838884

Авторы: Горляковский, Крутов, Тримайлов

Текст

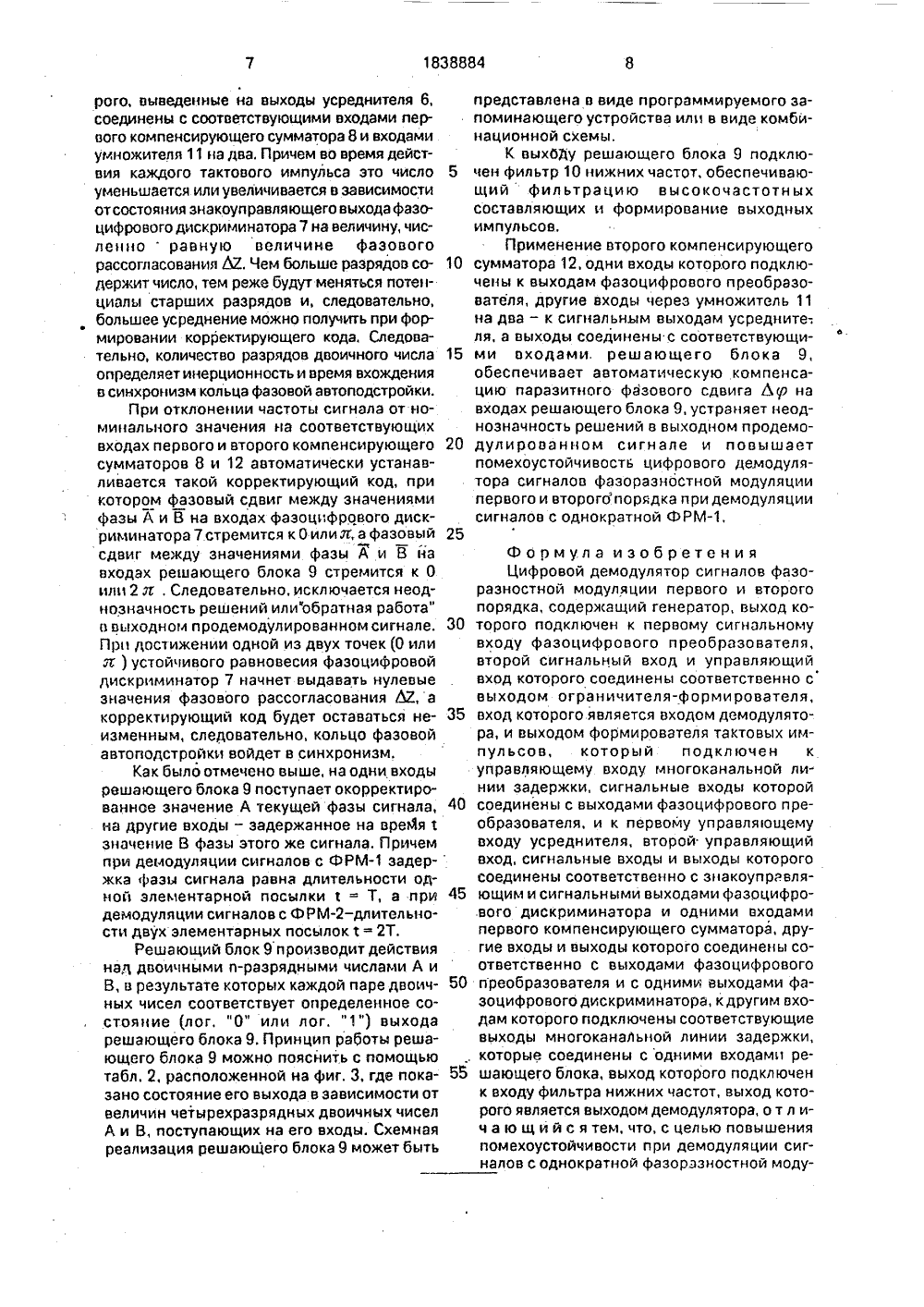

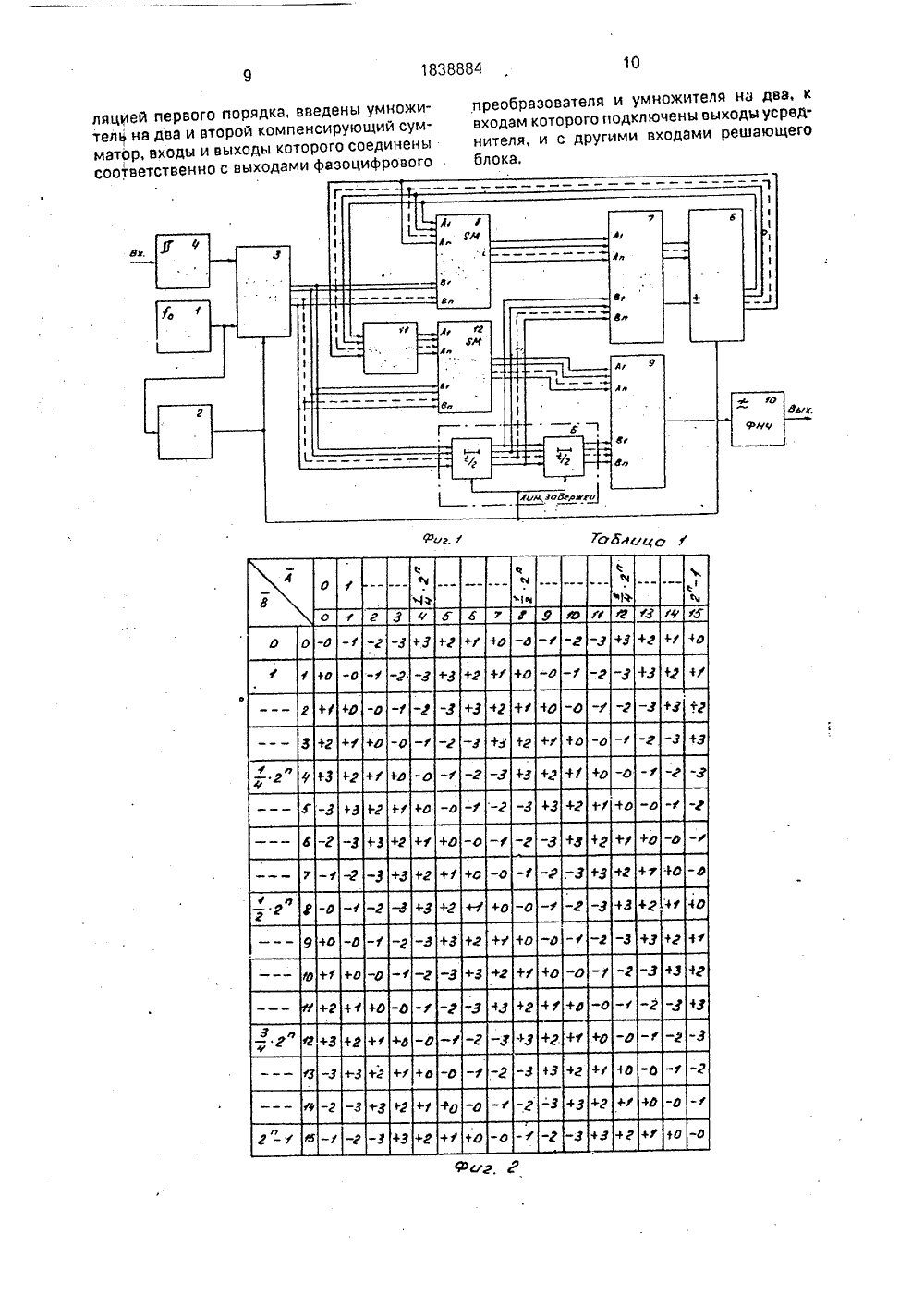

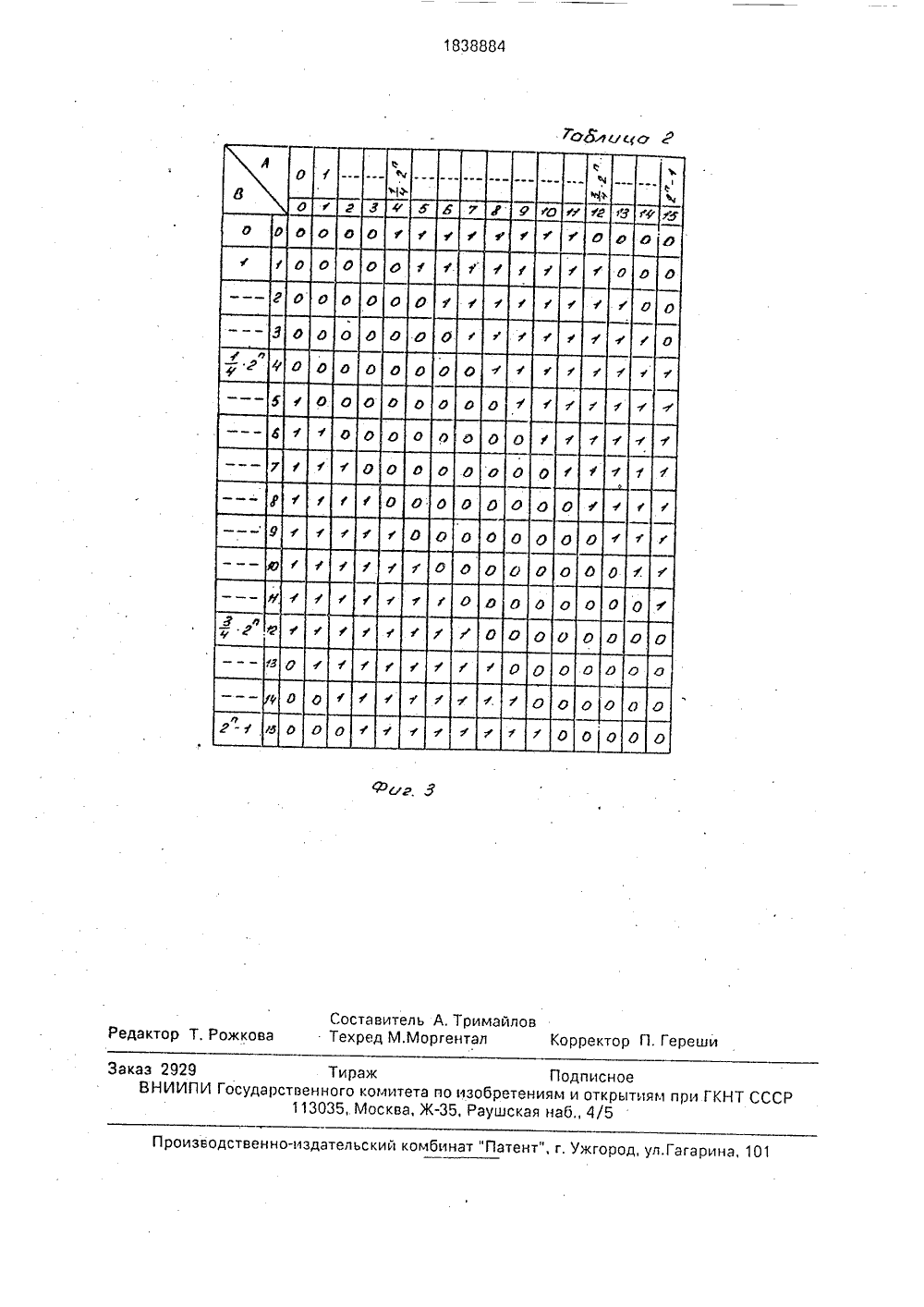

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1838884 АЗ 1)5 Н 04 1 27/2 ПАТЕНТ ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(54) ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИИПЕРВОГО И ВТОРОГО ПОРЯДКА(57) Использование: в радиотехнике, в выходных устройствах для демодуляции сигналов с однократной фазоразностной модуляцией первого (Ф Р М) и второго (ФРМ) порядка и нестабильной частотой несущей, Сущность изобретения: цифровой демодулятор содержит генератор, выход которого подключен к входу формирователя тактовых импульсов и к первому сигнальному входу фазоцифрового преобразователя, второй сигнальный вход и управляющий вход которого соединены соответственно с выходом ограничителя-формирователя, вход которого является входом демодулятора, и выходом формирователятактовых имИзобретение относится к радиотехнике и может использоваться в выходных устройствах для демодуляции сигналов с однократной фазоразностной модуляцией первого (Ф РМ) и второго (Ф РМ) порядка и нестабильной частотой несущей. пульсов, который подключен куправляющему входу многоканальной ли 11 ии задержки, сигнальные входы которой соединены с выходами фазоцифрового преобразователя, и к первому управляющему входу усреднителя, второй управляющий вход, сигнальные входы и выходы которого соединены соответственно со знакоуправляющим и сигнальным выходами фазоцифрового дискримина; ора и одними входами первого компенсирующего сумматора, другие входы и выходы которого соединены соответственно с выходами фазоцифрового преобразователя и с одними входами фазоцифрового дискриминатора, к другим входам которого подключены соотвегствующие выходы многоканальной линии задерж- а ки, которые соединены с одними входами решающего блока, выход которого подклю-; Д чен к входу фильтра нижних частот, выход которого я вля ется в ы ходом демодулятора. , Повышение помехоустойчивости достигается за счет введения второго компенсирую-щего сумматора, одни входы которого подключены к выходам фазоцифрового пре- - а образователя, другие входы через умножи-Со тель на два - к сигнальным выходам усреднителя, а выходы соединены с соответствующими входами решающего блока, 3 ил.СО Цель изобретения - повышение помехоустойчивости при демодуляции сигналов с однократной фазоразностной модуляцией первого порядка. Изобретение поясняется чертежами.На фиг. 1 изображена структурная электрическая схема цифрового демодулятора сигналов фазораэностной модуляции первого и второго порядка.Цифровой демодулятор сигналов фазоразностнай модуляции первого и второго порядка содержит генератор 1, выход которого подключен к входу формирователя 2 тактовых импульсов и первому сигнальному входу фазоцифрового преобразователя 3, второй сигнальный вход и управляющий вход которого соединены соответственно с выходом ограничителя-фбрмирователя 4, вход которого является входом.демодулятора, и выходом формирователя 2 тактовых импульсов, который подключен к управлвощему входу многоканальной линии 5 задержки, сигнальные входы которой соединены с выходами фазоцифроваго преобразователя 3, и к первому управляющему входу усреднителя 6, второй управляющий вход, сигнальные входы и выходы которого соедицены соответственно со знакоуправляющим и сигнальными выходами фазоцифравого дискриминатора 7 и одними входами первого компенсирующего сумматора 8, другие входы и выходы которого соединены соответственно с выходами фазоцифровага преобразователя 3 и с одними входами фазоцифрового дискриминатора 7, к другим входам которого подключены соответствующие выходы многоканальной линии 5 задержки, которые соединены с одними входами решающего блока 9, выход которого подключен ка входу фильтра нижних частот 10, выход которого является выходам демодулятора, умножитель 11 на два и второй компенсирующий сумматор 12, входы и выходы которого соединены соответственно с выходами фазоцифрового преобразователя 3 и умножителя 11 на два, к входам которого подключены выходц усреднителя 6, и с другими входами решающего блока 9,Цифровой демодулятор сигналов фазоразностной модуляции. первого и второго порядка работает следующим образом.Входной си нусоидал ьн ый сигнал с однократной фазоразностной модуляцией первого (ФРМ) или второго (ФРМ) порядка поступает нэ вход ограничителя-формирователя 4, где происходит его ограничение и формирование импульсной последовательности. Причем во время положительных полупериадов сигнала амплитуда импульсов становится равной лог. "1", а во время Отрицательных - лог. "0". С выхода ограничителя 4 ограниченный и сформированный сигнал поступает на второй сигнальный вход фазацифрового преобра 10 зователя 3, на первый сигнальный вход этого же фаэоцифрового преобразователя 3 поступают импульсы с генератора 1 с частотой 1 о, а на управляющий вход поступают тактовые импульсы с формирователя 2 тактовых импульсов. На выходах фээоцифрового преобразователя 3 в момент действия фронтакаждого тактового импульса устанавливается определенное двоичное число, численно равное количеству периодов частоты 1 о, поступивших на фазоцифровой преобразователь 3 в течение интервала времени,начавшегося в момент установления заднего фронта предыдущего тактового импульса15 и заканчивающегося в момент установления ближайшего переднего фронта импульса сигнала..Это двоичное и-разрядное число на выходах фазоцифрового преобразователя 320 будет пропорционально текущему мгновенному значени,о фазы ограниченного и сформированного сигнала, измеренному вмомент действия тактового импульса. Причем максимальному значению двоичногачисла, равному 2, соответствует максиимальное значение фазы сигнала, равное 2 л(360 а),При номинальной частоте сигнала и отсутствии фазовой манипуляции мгновенныезначения фазы сигнала на выходе фазоцифравого преобразователя 3, приняв случайную величину, не изменяются от одноготакта к другому.Текущие мгновенные значения фазы35 сигнала поступают на сигнальные входымногоканальной линии 5 задержки, в каждом из каналов которой осуществляется задержка соответствующего разрядадвоичного числа на величину т, оавную дли 40 тельности одной элементарной посылки т = Т для сигналов с ФРМидлительности 1 = 2 Т для сигналов с ФРМ,Кроме того, каждый канал многоканальной линии 5 задержки имеет выход, обеспечиваащий% задержку сигнала на величину 1/2, равную половине величины задержки одного канала,При номинальной частоте сигнала и равенстве фаз колебаний сравниваемых посылок паразитный фазовый сдвиг Лр, равный50 разности мгновенных значениЙ текущих изадержанных на время 1 фаз сигнала, равеннулю, а мгновенные значения этих фаз одинаковы и неизменны, Также равен нулю па. раэитный фазовый сдвиг ЛО, равный55 разности мгновеннь 1 х значений текущих изадержанных на время 1/2 фаэ сигнала. Если же отклонение Ю частоты сигнала отличается от нуля, то мгновенные значениятекущих и задержанных фаз сигнала начнутЛр=2 ЛИ,510 ЛО=т М 1. 15 20 25 30 35 40 50 55 медленно изменяться с частотой повторения, равной Ю а паразитный фазовый сдвиг Лу) будет оставаться неизменным и равным: где ЬХ - отклонение частоты сигнала от номинального значения, Гц;т - время задержки в одном канале, с, Паразитный фазовый сдвиг ЬО,между текущими и задержанными на время 1/2 значениями фаз сигнала при этом равен: Как было отмечено выше, наличие паразитного фазового сдвига Ьр приводит к значительному ухудшению помехоустойчивости автокорреляционного демодулятора, Поэтому с целью повышения помехоустойчивости при демодуляции сигналов с однокэатной фазоразностной мОдуляцией первого порядка в цифровом демодуляторе сигналов фазоразностной модуляции первого и второго порядка осуществляется автоматическая компенсация паразитного фазового сдвига Лр с помощью второго кОмпенсирующего сумматора 12 умножите-. ля 11 на два и кольца фазовой автоподстройки, содержащего первый компенсирующий сумматор 8, усреднитель 6 и фазоцифровой дискриминатор 7,Текущие значения фазы сигнала с выхода фазоцифрового преобразователя 3 поступают на одни входы первого и второго компенсирующего сумматора 8 и 12, На другие входы компенсирующего сумматора 8 и входы умножителя 11 на два поступает корректирующий код, вырабатываемый в кольце фазовой автоподстройки, С выхода умножителя 11 на два удвоенная величина корректирующего кода поступает на сооответствующие входы второго компенсирующего сумматора 12.Такое подключение сумматоров 8 и 12 к выходам усреднителя 6 приводит к тому, что значение корректирующего кода, суммирующееся с текущим значением фазы сигнала во втором компенсирующем сумматоре 12, будет в два раза больше, чем значение корректирующего кода, суммирующееся с текущим значением фазы сигнала в первом компенсирующем сумматоре 8. Время задержки фаз сигнала, поступающих с многоканальной линии 5 задержки на одни входы решающего блока 9, также в два раза боль-, ше, чем время задержки фаз сигнала, поступающих с выходов многоканальной линии 5 задержки на другие входы фаэоцифрового дискриминатора 7. Следовательно, фазовый сдвиг между откорректированным значением текущей фазы сигнала и задержанным значением фазы сигнала на входах решающего блока 9 будет в два раза больше, чем фазовый сдвиг между откорректированным значением текущей Фазы сигнала и задержанным значением фээы сигнала на входах фазоцифрового дискриминатора 7.Откорректированное значение А текущей фазы сигнала с выходов первого компенсирующего сумматора 8 поступает на одни входы фазоцифрового дискриминатора 7. На другие входы фазоцифрового дискриминатора 7 подается задержанное на время с/2 значение В фазы сигнала, поступающее с выходов многоканальной линии 5 задержки. Фазоцифровой дискриминатор 7 представляет собой устройство, в котором каждой паре двоичных п-рэзрядных чисел А и В, поступающих на его входы, соответствует определенное (и)-разрядное двоичное число Е на его выходе, Это число Е остается неизменным в течение промежутка времени, равного периоду тактовой чэстоты, и может изменяться только и момент действия тактов ых импул ьсов. Старший (и) разряд этого числа Е является энакоуправляющим разрядом, покаэыва ощим иеобходимость увеличения или уменьшения корректирующего кода, Остальные разряды определяют величину фазового рассогласования Ы в виде (и)-разрядного двоичного числа. Схемная реализация флэоцифрового дискриминатора 7 может быть представлена в виде программируемого запоминающего устройства или в виде комбинационной схемы.Принцип работы фазоцифрового дискриминатора 7 можно пояснить с помощью табл. 1, расположенной иа фиг, 2, где показано состояние выходов фазоцифрового дискриминатора 7 в зависимости от величин четырехрээрядных (и = 4) двоичных чисел А и В. Состояние старшего (и) разряда обозначено знаками "+" или "-". Причем знаку "+" соответствует состояние лог, О, а знаку "-"- лог. 1. Величина фазового рассогласования Ы представлена в десятичном коде. Сигнальные выходы фазоцифоового дискриминатора 7 соединены с соответствующими входами усреднителя 6, первый и второй управляющие входы которого соединены соответственно с выходами формирователя 2 тактовых импульсов и со знакоуправляющим выходом фэзоцифрового дискриминатора.Усреднитель 6 представляет собой блок, в который записывается многоразрядное двоичное число, старшие разряды кото 183888445 50 рого, выведенные на выходы усреднителя 6, соединены с соответствующими входами первого компенсирующего сумматора 8 и входами умножителя 11 на два. Причем во время действия каждого тактового импульса это число уменьшается или увеличивается в зависимости отсостояния энакоуправляющего выхода фазоцифрового дискриминатора 7 на величину, численно равную величине фазового рассогласования И. Чем больше разрядов содержит число, тем реже будут меняться потенциалы старших разрядов и, следовательно, большее усреднение можно получить при формировании корректирующего кода, Следовательно, количество разрядов двоичного числа определяет инерционность и время вхождения в синхронизм кольца фаэовой автоподстройки.При отклонении частоты сигнала от номинального значения на соответствующих входах первого и второго компенсирующего сумматоров 8 и 12 автоматически устанавливается такой корректирующий код, при котором фазовый сдвиг между значениями фазы А и В на входах фазоцифрового дискриминатора 7 стремится к О илия,а фазовый сдвиг между значениями фазы А и В йа входах решающего блока 9 стремится к 0 или 2 л . Следовательно, исключается неоднозначность решений или "обратная работа" в выходном продемодулированном сигнале. Прп достижении одной из двух точек 0 или ж ) устойчивого равновесия фазоцифровой дискриминатор 7 начнет выдавать нулевые значения фазового рассогласования Ы, а корректирующий код будет оставаться неизменным, следовательно, кольцо фаэовой автоподстройки войдет в синхронизм,Как было отмечено выше, на одни входы решающего блока 9 поступает окорректированное значение А текущей фазы сигнала,на другие входы - задержанное на вредя 1 значение В фазы этого же сигнала, Причем при демодуляции сигналов с ФРМзадержка фазы сигнала равна длительности одной элементарной посылки т = Т, а при демодуляции сигналов с ФРМ- длительности двух элементарных посылок с - 2 Т.Решающий блок 9 производит действия над двоичными и-разрядными числами А и В, в результате которых каждой паре двоичных чисел соответствует определенное состояние лог, "0" или лог. "1") выхода решающего блока 9. Принцип работы решающего блока 9 можно пояснить с помощью табл. 2, расположенной на фиг, 3, где покаэано состояние его выхода в зависимости от величин четырехразрядных двоичных чисел А и В, поступающих на его входы, Схемная реализация решающего блока 9 может быть 5 10 15 20 25 30 35 40 представлена в виде программируемого запоминающего устройства или в виде комбинационной схемы.К выхбДу решающего блока 9 подключен фильтр 10 нижних частот, обеспечивающий фильтрацию высокочастотных составляющих и формирование выходных импульсов.Применение второго компенсирующего сумматора 12, одни входы которого подключены к выходам фазоцифрового преобразователя, другие входы через умножитель 11 на два - к сигнальным выходам усредните-. ля, а выходы соединены с соответствующими входами. решающего блока 9, обеспечивает автоматическую компенсацию паразитного фазового сдвига Ьр на входах решающего блока 9, устраняет неоднозначность решений в выходном продемодулированном сигнале и повышает помехоустойчивость цифрового демодулятора сигналов фазораэностной модуляции первого и второгопорядка при демодуляции сигналов с однократной ФРМ,Формула изобретения Цифровой демодулятор сигналов фазораэностной модуляции первого и второго порядка, содержащий генератор, выход которого подключен к первому сигнальному входу фазоцифрового преобразователя, второй сигнальный вход и управляющий вход которого соединены соответственно с выходом ограничителя-формирователя, вход которого является входом демодулятора, и выходом формирователя тактовых импульсов, который подключен к управляющему входу многоканальной линии задержки, сигнальные входы которой соединены с выходами фаэоцифрового преобразователя, и к первому управляющему входу усреднителя, второй управляющий вход, сигнальные входы и выходы которого соединены соответственно с знакоуправляющим и сигнальными выходами фазоцифрового дискриминатора и одними входами первого компенсирующего сумматора, другие входы и выходы которого соединены соответственно с выходами фазоцифрового преобразователя и с одними выходами фазоцифрового дискриминатора, к другим входам которого подключены соответствующие выходы многоканальной линии задержки, которые соединены с одними входами решающего блока, выход которого подключен к входу фильтра нижних частот, выход которого является выходом демодулятора, о т л ич а ю щ и й с я тем, что, с целью повышения помехоустойчивости при демодуляции сигналов с однократной фазораэностной моду 1838884 10ляцией первого порядка, введены умножителв на два и второй компенсирующий сумматрр, входы и выходы которого соединены соответственно с выходами фазоцифрового преобразователя и умножителя на два, квходам которого подключены выходы усреднителя, и с другими входами решающегоблока.1838884 7 оИсу ктор П. Гереши Т. Рожкова Реда кт аказ 2929 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035,Москва,Ж, Раушская наб 4/5 изводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагар Составите Техред М,А. Тримайлоргентал

СмотретьЗаявка

4938353, 20.05.1991

ОМСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИБОРОСТРОЕНИЯ

ТРИМАЙЛОВ АЛЕКСАНДР ЕВГЕНЬЕВИЧ, КРУТОВ МИХАИЛ ИВАНОВИЧ, ГОРЛЯКОВСКИЙ ВЛАДИМИР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: второго, демодулятор, модуляции, первого, порядка, сигналов, фазоразностной, цифровой

Опубликовано: 30.08.1993

Код ссылки

<a href="https://patents.su/6-1838884-cifrovojj-demodulyator-signalov-fazoraznostnojj-modulyacii-pervogo-i-vtorogo-poryadka.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор сигналов фазоразностной модуляции первого и второго порядка</a>

Предыдущий патент: Стереодекодер

Следующий патент: Устройство для подключения к телефонной розетке средств обработки и передачи информации

Случайный патент: Способ искусственного опыления растений yicca spp. l.