Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1674122

Авторы: Козюминский, Насимов

Текст

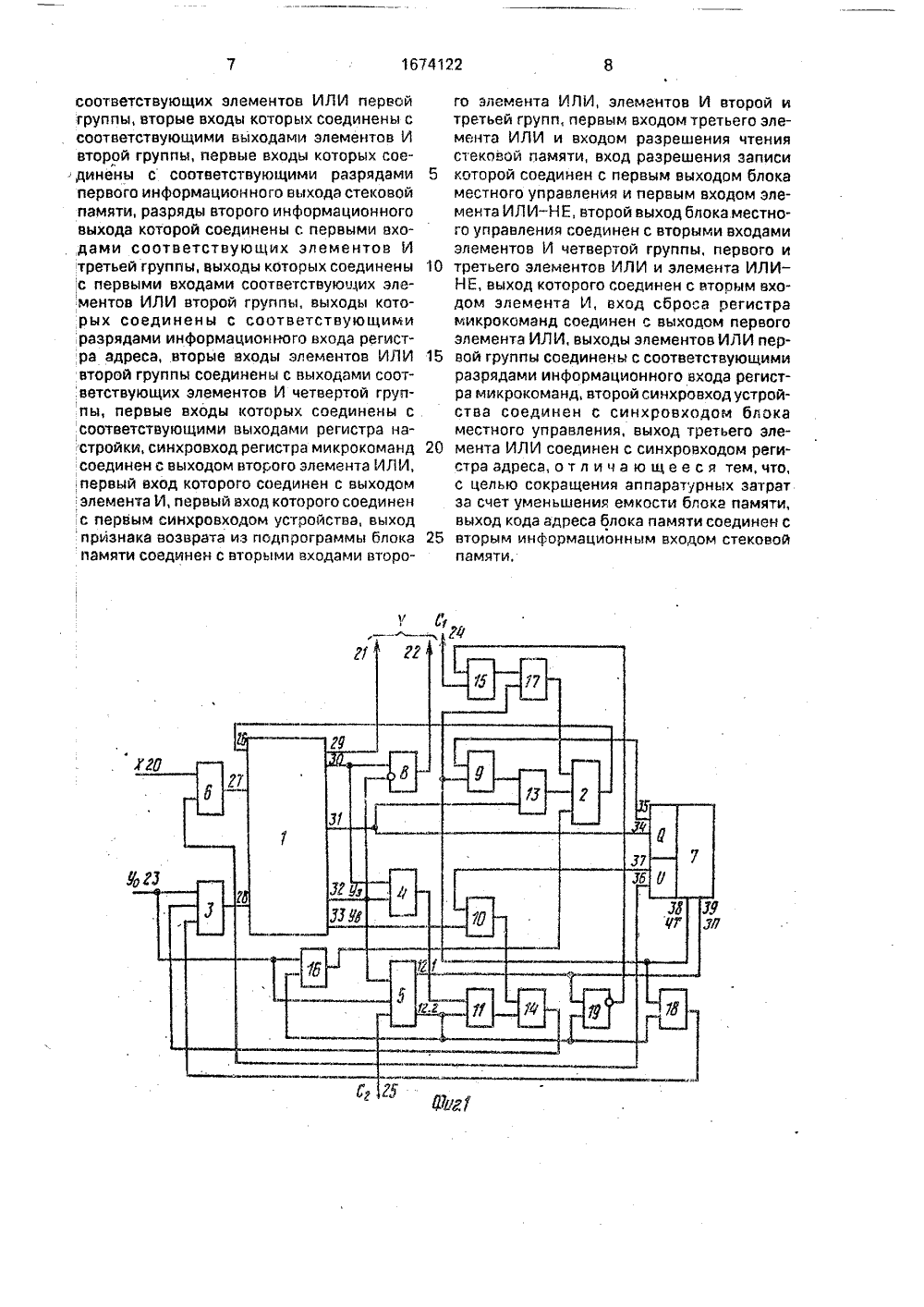

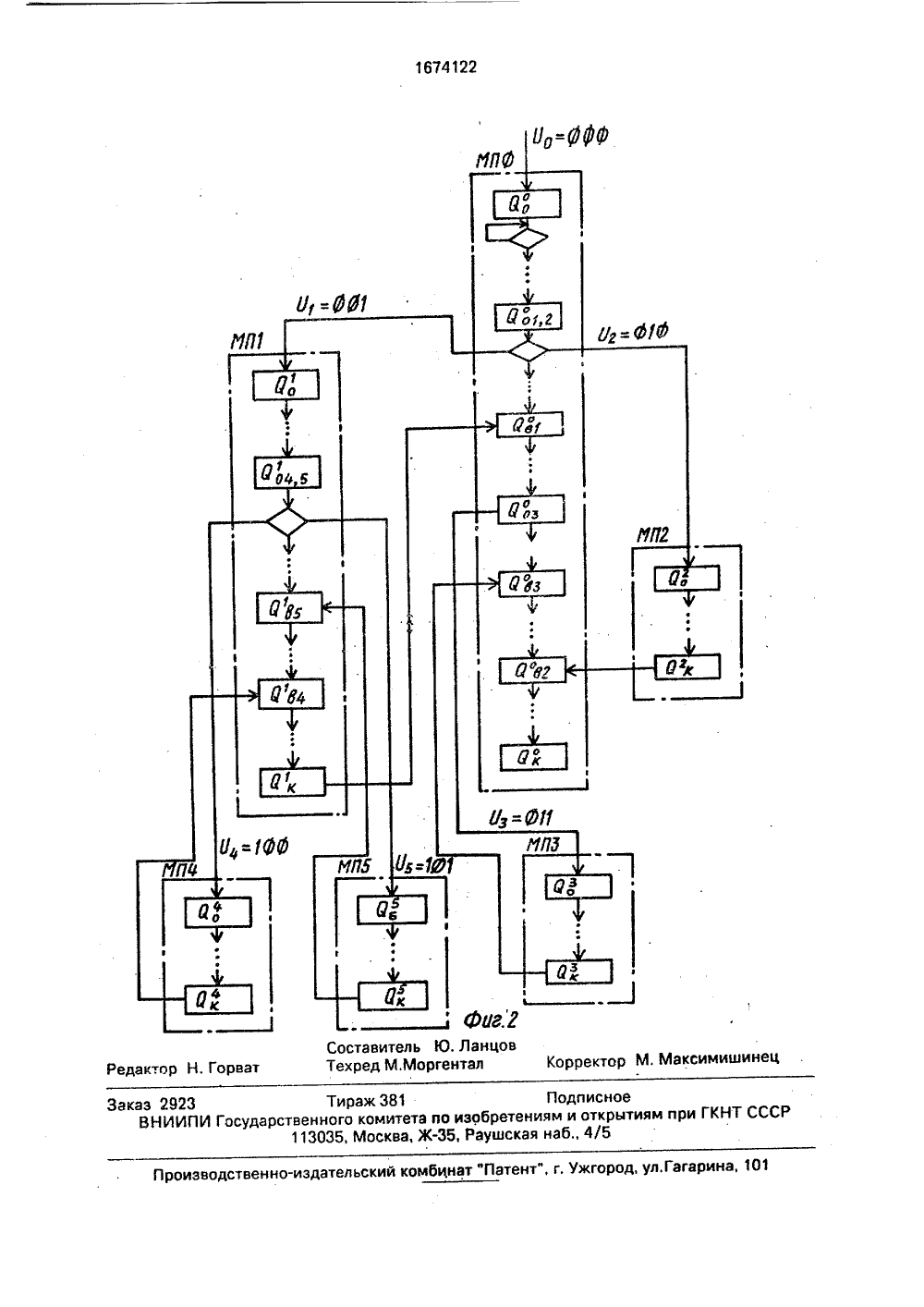

СОВХОЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 412 8 06 Е 9/22 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР САНИЬ ИЗСБ НИ.Я л, ь 32нский и В.Е,Насимов)идетельство СССР06 Г 9/22, 1984.идетельство СССР06 Г 9/00, 1986.идетельство СССР06 Р 9/22, 1987,ГРАММНОЕ УСТРОЙСТВ Изобретение относится к вычислительной технике и обеспечивает построение микропрограммных устройств управления.Целью изобретения является сокращение аппаратурных затрат за счет уменьшения емкости блока памяти.На фиг.1 изображена функциональная схема устройства; на фиг,2 - пример реализации алгоритма управления.Устройство содержит блок памяти 1, регистр микрокоманд 2, регистр адреса 3, регистр настройки 4, блок местного управления 5, мультиплексор 6, стековую память 7, с первой по четвертую группы элементов И 8-11, выходы 12 1, 12.2 блока 5, первую и вторую группы элементов ИЛИ 13, 14, элемент И 15, с первого по третия элементы ИЛИ 16-18, элемент ИЛИ-НЕ 19, вход логических условий 20, первый-и вто. рой выходы 21 и 22, вход начальной установки 23, перый и второй синхровходы 24 и 25,(21) 4638138/24.(57) Изобретениеной технике и мо относится к вычислитель ет быть использовано при построении устройств управления и управляющих автоматов. Целью изобретения является сокращение аппаратурных затрат за счет уменьшения емкости блока памяти. Поставленная цель достигается;ем, что микропрограммное устройство управления содержит блок памяти, регистр микрокоманд, регистр адреса, регистр настройки, блок местного управления, мультиплексор,стековую память, с первой по четвертую группы элементов И, первую и вторую группы элементов ИЛИ, элемент И, с первого по третий элементы ИЛИ и элемент ИЛИ-НЕ.2 ил. Блок памяти 1 имеет трифадресных входа 26 - 28, выход 29 кода микроопераций,.выход 30 кода подпрограммы, выход 31 кода адреса микрокоманд, выход 32 признака подпрограммы и выход 33 признака возврата, Стековая память имеет информационные входы 34 и выход 35, информационные вход 36 и выход 37, входы чтения 38 и записи 39. устроиства рассмотрим на при- ф иэации алгоритма управления, о микропрограммой на фиг,2. данной микропрограммы (МП) пуения на подпрограммы (микроы) приведена к виду, ющему ее реализацию в предларойстве. ом МП имеет головную микроМПо и микропрограммы МП 1 чного уровня иерархии. Для микропрограммах МПО = 9,5 поРаботу мере реал описанног Структура тем разби программ обеспеч ва гаемом уст При эт программу МП 5 рэзли простоты вказаны только начальные сосгояния Оо, конечные состояния Ок, состояния обраше 1ния Оо и состояния возврата О 51 = УП),1Каждая из МП, =: 0,5 реалзуется в цифровом автомате некоторым подавтоматам 5 А 1, В текущий момент времени реализуемый в устройстве подавтомат А 1 (или МП 1) опоеделяется значением текущего кода настройки .51 в регистре адреса 3. Если МП содержитМП 1, то разрядность кода настройки К = 10 ) Оц 2 Ц, где 1 а( означает ближайшее бол ьшее целое число от "а", Для примера= 6, гогда как К = 3, Каждому падае 1 тамату,А 1(или МП 1) присваивается некоторый код настройки О 1, Для простоты положим, чта код настройки 15 соответствует двоичному коду номера , тогда для примера имеем МПо-.о =- ЩЯ: Мг 1- О 1 =,6 О 1МП - Оь = 6 При ятом головной МП (т.е, в данном примере МПо) необходимо назначить код настройкио, 20 совпадающий с кодам исходного состояния регистра 3, устанавливаемым сигналам Уа по входу 23 начальной установки устройства (как правило, это соответствует нулевому коду), 25В СОСтаяНИИ Об 1 рао.ЕНИя Оо 1 а ПадаВтамате А должен вырабатываться (на выходах 30 блока 1) код настройкиОдного или одного из нескольких падавтаматов А;, Последнее означает, что вызов одного из под автоматов А Осуществляется в зависимости от входных условий Х (Х : Х), анализируемых в устройстве в текущий момент времени; Для примера на фиг,2 из состсяния О о 1,2 ПадаатаМата Ао ОСуШЕСтВЛЯЕтея ВЬ 1- 35озав подавтомата А 1 ил А 2, При обращении к подпрограмме на выходах 31 блока памяти 1 формируется код состояния возврата (вг.примере, при вызове УП эта 01, а при вызове МП 2 - Оа ) и сигнал запроса Уз(фар мируется на выходе 32 блока 1), 8 соответствии с этим в МПо в автомате А, в состОЯнии 001,2 (при вызове А 1) на Выходах 30 блока 1 формируется код 01:= ф 1, на высодах 31 - код 031, а на выходе 32 - Уз.45 В подавтомате А каждому состоянию О микропрограммы МП соответствует некоторый ДВОичныЙ кОЦ сост 051 ния регистра 2, В общей случае число состояний Р; микро программ МП 1,= 1может быть различным. В связи с этим разрядность регистра 2 рассчитывается как г =- 1 Оу 2 1 епах (Р 1(. Из этого следует, что при разбиении микропрограммы общего алгоритма на блоки 55 (микропрограммы), которые в устройстве должны реализоваться подавтаматами, неОбходимо стремиться к обеспечению аавенсте 1 а числа сосго янИЙ Р 1 для всех подавтоматов. Кодирование состояний 01 гразрядным двоичньм кодом может бытьпроизвольным, Накладываются ограничения только на коды исходных состояний 0подавтоматав: код состояния Оо должен1совпадать с ходом, устанавливаемым в регистре 2 по сигналу установки Уо (если поэтому сигналу регистр 2 обнуляется, то длявсех подавтаматов Оо =.О.9). Код состояния возврата Ов может быть произволь 1ным, так как он не зависит от кодаобращения ОоВ конечном состоянии О,= 13=1 подавтоматов А наряду с выходными сигналами У на выходах 29 и 30 блока 1формируешься сигнал возврата У. на выходе33 блока 1.Блок памяти 1 устройства реализует систему нулевых функций подавтоматовА 1,=,Р; - 1 с увам входных сигналовнастройки .1, При этом мультиплексор бОбеспечивает подключение на входы 25 блока 1 входных сигналов ХХ, анализируемых в микропрограмме МП 1 исущественных, следовательно, для подавтомата АьВ начальное состояние схема устройства устанавливается по сигналу Уо на входе23 устройства. Па сигналу Уо в регистре 3устанавливается код,б,.Я, что соответствуеткоду нас гройки Оо, а в регистре 2-код,о 9,что соответствует исходному состояниюО Кроме того, синалом Уо обнуляетсяблок местного управления 5, Таким образомсигналом Уо схема устройства подготовленак реализации падавтомата Ао, функционирование которого определяется микропрогРаММОЙ МПо,С приходом синхросигнала С 5 (при этомэлемент И 15 по входу подключается к выходу элемента ИЛИ - -Е 19, является открытым) Осуществляется переход подавтоматаАо в следующее состояние, определяемоевыходными сигналами с выходов 29,30 блока 1, Период следования синхросигналов С 1определяется исходя из обеспечения как устойчивого функционирования объекта управления, на который поступаютуправляющие сигналы У, так и устойчивогопеоехода автомата из одного состояния вдругое,В СОСТОЙНИИ 001,2 ПадаВТОМдта Ао В ЗаВИСИМОСТИ ОТ ВХодНЫХ СИГНВЛОВ Хо ПрОИСХОдит инициализация одного из подавтоматовА 1 или А 2 (пусть зто будет А 1). При этом навыходах 30 блокаВырабатывается код настройки Ъ =-Ф 1, на выходах 31 блока 1 - ,код Ов. а на выходе 32 блока 1- сигнал Уз,Сигиал Уэ разрешает запись кода О 1 в регистр настройки 4 и одновременно запрещает прохождение кода И через группуэлементов И 8 на выход устройства 22. Тем самым исключается влияние выходных сигналов 30 блока 1 при формировании кода настройки на объект управления. При поступлении сигнала Уз на вход местного бло ка управления 5 на первом выходе блока 5 вырабатывается единичный потенциал. Этим сигналом по входу записи 39 стековой памяти 7 будет разрешена запись в стеко- ВуЮ ПаМятЬ КОда СОСтаяи 11 я О 81 о С ВЫХОда .10 31, а по входам 36 - кода настройки . Оо =фф из регистра 3. Ьдно- временно по цепи элементов ИЛИ-НЕ 19 и И 15 блокируется прохождение очередного синхрасигнала С 1 на синхровход регистра 2 15 (тем самым блокируется возможность пеаехода подавтомата Ао в другое состояние), С приходом синхросигнала С 2, который поступает на синхровхад местного блока управления 5, единичный потенциал 20 сбрасывается на первом выходе блока 5 и устанавливается на втором. Единичный сигнал со второго выхода блока 5 осуществляет по цепи элемента ИЛИ 16 обнуление регистра 2; по цепи элементов Иподключе иие выходов регистра 4 к информационным входам регистра 3; по цепи элемента ИЛИ 18 разрешается перезапись кода настройки 01 из регистра 4 в регистр 3, В результате в регистр 3 будет записан код настройки 30 01 =,891. Схема устройства готова к реализации подавтомата А 1. С приходом очеред-. ного синхрасигнала С 2 на втором выходе блока местного управления 5 установится нулевой потенциал, в результате чего поло жительным потенциалом с выхода элемента ИЛИ-НЕ 19 будет разрешено прохождение синхросигналов С 1 на синхровход регистра 2, В дальнейшем устройство реализует подавтомат А 1, 40Аналогичным образам в состоянии Оо 4,5 подавтомата А 1 осуществляется инициализация, например, подавтомата АБ. При этом на выходе 30 блока 1 формируется код 05 = 1 ф 1, а на выходе 31 - код состоя ния возврата О 85 или А 5. Состояние Ов 5 и1 1 код 01 = ДЙ запишутся в первую ячейку СтЕКОВай ПаМЯтИ 7, а КОДЫ Оо =,бф И Ов 1 перезапишутся во вторую ячейку стековойпамяти. Число ячеек стековой памяти 7 кодом состояний и настроек возврата определяется глубиной вложенности (или обращений) микропрограмм алгоритма управления, Например, глубина обращений, аследовательно, число ячеек узла памяти для. 55 изображенной ча фиг.2 микропрограммы равно двум.Я конечном состоянии функционирования подавтомата А 5 в состоянии О микропрограммы МП 5) иа выходе ЗЗ блока 1 будет,сформирован сигнал Ув. Этим сигналом информационные выходы 35 и 37 стековой памяти 7 будут подкл ючены к информационным входам соответственно регистра 2 и регистра 3. Этим же сигналом будет разрешена запись с выхода стековой памяти в регистры 2 и 3. Задним франтом сигнала Ув будет осуществлена перезапись содержимого ячеек стековой памяти, Таким образом, в регистр 2 будет записан код Ов 5 подавтомата А 1, а в регистр 3 - код 01 =,Щ 1, В первую ячейку стековой памяти 7 будут записаны из второй Ячейки коды Ов 1 и Оо =)ЩК В дальнейшем в устройстве реализуется подавтомат А 1, Аналогично осуществляется возврат из подавтамата Ав падавтомат Ао.Таким образом,.в устройстве реализуется иерархически организованная. сеть из Е подавтоматов, технически аеализуемых на основе одного :функционального автомата.Формула изобретения Микропрограммное устройство управления, содержащее блок памяти, регистр микрокоманд. регистр адреса, регистр настройки, блок местного управления, мультиплексор, стековую память, с. первой по четвертую группы элементов И, первую и вторую группы элементов ИЛИ, элемент И, с первого по третий элементы ИЛИ и элемент ИЛИ - НЕ, причем вход логических условий устройства соединен с информационным входом мультиплексора, выход которого соединен с первым адресным входом блока памяти, выход кода микроопераций которого соединен с первым выходом микроопераций устройства, выход регистра адреса соединен с управляющим входам мультиплексора, с первым информационным входом стековой памяти и с вторым адресным входом блока памяти, третий адресный вход которого соединен с выходом регистра микрокомаида вход начальной установки регистра адреса соединен с одноименным входом блока местного управления, с первым входом первого элемента ИЛИ и с входом начальной установки устройства, второй выход микроопераций которого образуют выходы элементов И первой группы, первые входы которых соединены с выходами кода подпрограммы блока памяти и информационными входами регистра настройки, вход разрешения записи которого соединен с входом задания режима блока местного управления, с вторыми входами элементов И первой группы и с выходом признака подпрограммы блока памяти, выход кода адреса которого поразрядно соединен с первыми входамисоответствующих элементов ИЛИ первой группы, вторые входы которых соединены с соответствующими выходами элементов И второй группы, первые входы которых соединены с соответствующими разрядами первого информационного выхода стековой памяти, разряды второго информационного выхода которой соединены с первыми входами соответствующих элементов И третьей группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с соответствующими разрядами информационного входа регистра адреса, .вторые входы элементов ИЛИ второй группы соединены с выходами соответствующих элементов И четвертой группы, первые входы которых соединены с соответствующими выходами регистра настройки, синхровход регистра микрокоманд соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом элемента И, первый вход которого соединен с первым синхровходом устройства, выход признака возврата иэ псдпрограммы блока памяти соединен с вторыми входами второго элемента ИЛИ, элементов И второй и третьей групп, первым входом третьего элемента ИЛИ и входом разрешения чтения стековой памяти, вход разрешения записи 5 которой соединен с первым выходом блокаместного управления и первым входом элемента ИЛИ - НЕ, второй выход блока местного управления соединен с вторыми входами элементов И четвертой группы, первого и 1 О третьего элементов ИЛИ и элемента ИЛИНЕ, выход которого соединен с втооым входом элемента И, вход сброса регистра микрокоманд соединен с выходом первого элемента ИЛИ, выходы элементов ИЛИ пер вой группы соединены с соответствующимиразрядами информационного входа регистра микрокоманд, второй синхровход устройства соединен с синхровходом блока местного управления, выход третьего зле мента ИЛИ соединен с синхровходом регистраадреса,отличающееся тем,что, с целью сокращения аппаратурных затрат эа счет уменьшения емкости блока памяти, выход кода адреса блока памяти соединен с 25 вторым информационным входом стековойпамяти.ьский комбинат "Петен ород, ул.Гагарина, 10 Производственно-и каз 2923 ВНИИПИ Тираж 381арственного комитета по изобр 113035, Москва, Ж-З 5, Рауш Подписноениям и открытиям при ГКНТ СССая наб., 4/5

СмотретьЗаявка

4638138, 16.01.1989

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ, НАСИМОВ ВЛАДИМИР ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.08.1991

Код ссылки

<a href="https://patents.su/5-1674122-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для определения знака числа, представленного в системе остаточных классов

Следующий патент: Устройство динамического приоритета

Случайный патент: Н. п. капицынамосковский лесотехнический институт