Параллельный сумматор кодов фибоначчи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

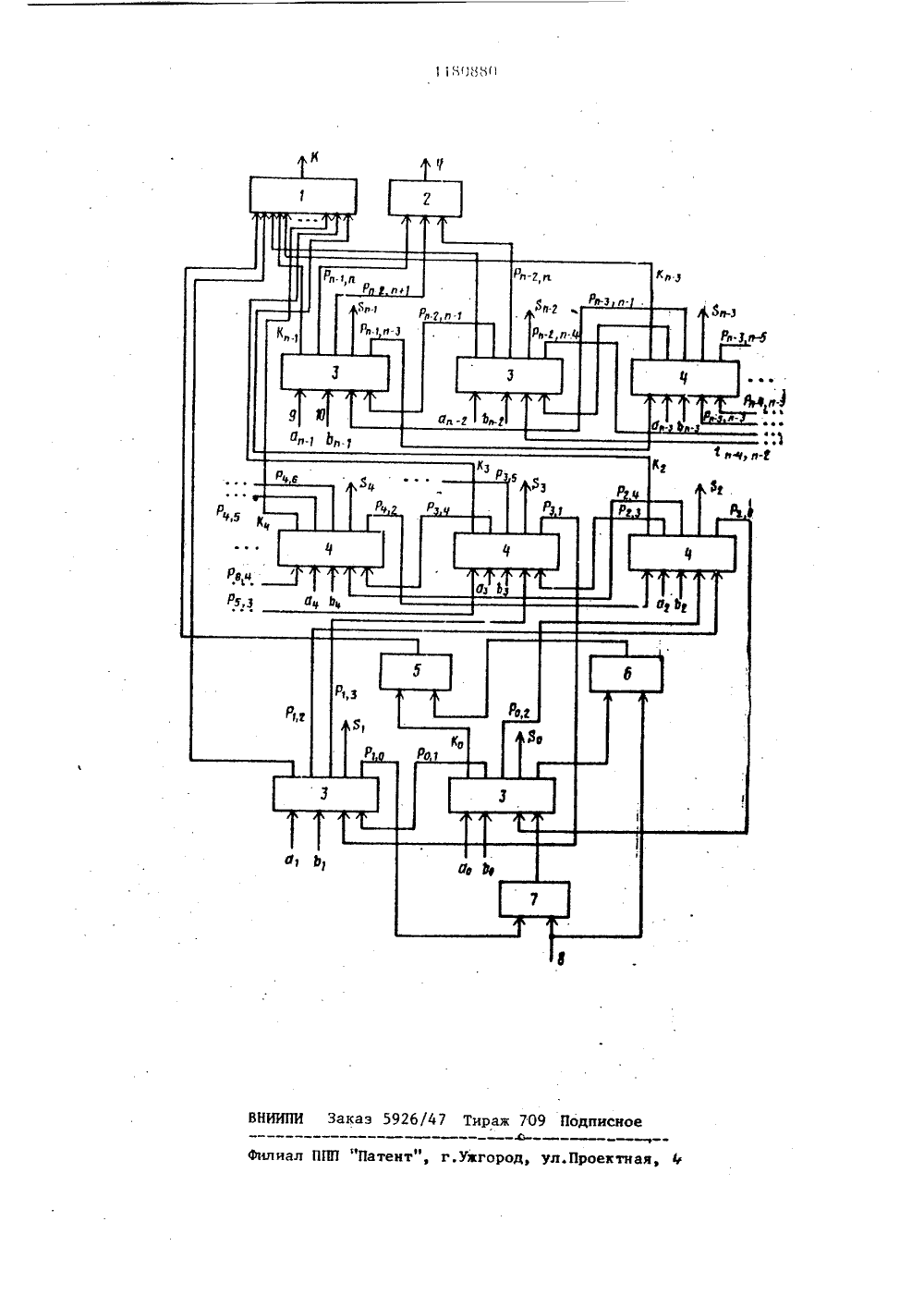

(56)кл. С У 2375655,79.ВОСУДАРСТНЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ торское свидетельство СССР993, кл. С 06 Р 7/49, 1982.57) ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ У 981(54) (ФИБОНАЧЧИ, содержащий пятивходовые одноразрядные сумматоры и первый элемент ИЛИ, причем первый и второй входы слагаемых пятивходовых одноразрядных сумматоров каждого (; -го разряда, где (, = 2п, 0)-1) разрядность параллельного сумматора, подключены к соответствующим разрядам первой и второй шин слагаемых параллельного сумматора, первый вход переноса пятивходового одноразрядного сумматора (, -го разряда подключен к первому выходу переноса пятивходового одноразрядного сумматора (3-1)-го разряда, а второй вход пе- реноса соединен с вторым выходом переноса пятивходового одноразряд" ного сумматора+2)-го разряда, третий вход переноса пятивходового одноразрядного сумматора (; -го разряда подключен к третьему выходу пере носа пятивходового одноразрядного сумматора ;-2)-го разряда, выход суммы пятивходового одноразрядного сумматора каждого ( -го разряда подключен к соответствующему разряду . выходной шины суммы параллельного сумматор, а контрольный выход соединен с соответствующим входом первогоэлемента ИЛИ, выход которого соединен с выходом контроля параллельногосумматора, о т л и ч а ю щ и й с ятем, что, с целью расширения егофункциональных возможностей путемосуществления суммирования кодов"золотой" 1-й пропорции, параллельный сумматор содержит два элемента,И, второй и третий элементы ИЛИ ичетыре четырехвходовых одноразрядныхсумматора, первый и второй входыслагаемых которых соединены соответственно с (П)-м и (й)-м первыми нулевым разрядами первой и второйшин слагаемых параллельного сумматора, выходы суммы соединены с соответствующими разрядами выходной шины суммы параллельного сумматора,а контрольные выходы первого, второго и третьего четырехвходовых одноразрядных сумматоров соединены с соответствующими входами первого элемента ИЛИ, первые входы переносовпервого и второго четырехвходовыходноразрядных сумматоров подключенысоответственно к первым выходампереноса второго четырехвходовогоодноразрядного сумматора и пятивходового одноразрядного сумматора (й)го разряда, вторые входы переносовпервого и второго четырехвходовыходноразрядных сумматоров соединены стретьими выходами переносов пятивхоЦовых одноразрядных сумматоров (й)и (й)-го разрядов соответственно,первый выход переноса пеового четырехвходового одноразрядного сумматорасоединен с первым входом второго элемента ИЛИ, выход которого соединенс выходом переполнения параллельного1180880 10 сумматора, вторые выходы переносапервого и второго четырехвходовыходноразрядных сумматоров подключенык третьим входам переносов пятивходовых одноразрядных сумматоров (и)-гои (П)-го разрядов соответственно,третьи выходы переноса первого и второго четырехвходовых одноразрядныхсумматоров соединены соответственнос вторым и третьим входами второгоэлемента ИЛИ, первый вход переносатретьего четырехвходового одноразрядного сумматора подключен к первомувыходу переноса четвертого четырехвходового одноразрядного сумматора,первый вход переноса которого подключен к выходу первого элемента И, вто-рые входы переносов третьего и четвертого четырехвходовых одноразрядныхсумматоров соединены с вторыми выходами переносов пятивходовых одноразряд-,ных сумматоров третьего и второгоразрядов соответственно, первый выходпереноса третьего четырехвходовогоодноразрядного сумматора соединен сИэобретецие относится к автоматике и вычислительной технике и может быть использовано в специализирован-ных вычислительных машинах.Целью изобретения является расширение функциональных возможностей параллельцого сумматора кодов фибоцаччи за счет осуществления суммирования кодов "золотой" 1-й пропорции. На чертеже приведена структурнаясхема параллельного сумматора кодовФибоцаччи. Параллельцый сумматор содержит 15элемент ИЛИ 1 ца и входов (и - числоразрядов суммируемых кодов), элементИЛИ 2 на трн входа, четыре четырехвходовых одцораэрядных сумматора 3,(и) пятив:одовых одноразрядных сумматора 4, элемент ИЛИ 5 на двавхода, элемент И 6 ца два входа,второй вход которого является инверсным, элемент И l ца два входа, входзадания р:жюд сумматора 8 и шины 9 25и 10 слав,1 1 ых. первым нходом переноса пятивходоногоодцоразрядцого сумматора второго разряда, а второй выход переноса соединен с первым входом первого элементаИ, второй вход которого подключен квходу задания режима параллельногосумматора, второй выход переносачетвертого четырехвходового одноразрядного сумматора подключен к первомувходу второго элемента И, второй входкоторого соединен с вторым входомпервого элемента И,третьи выходы переносов третьего и четвертого четырехвходовых одноразрядных сумматоровподключены к третьим входам переносовпятивходовых одноразрядных сумматоров третьего и второго разрядов соответственно, выход второго элемента Исоединен с первым входом третьегоэлемента ИЛИ, второй вход которогосоединен с контрольным выходом четвертого четырехвходового одноразрядного сумматора, а выход подключен ксоответствующему входу первого элемента ИЛИ. 2Элемент ИЛИ 1 предназначен для сборки сигналов контроля К(Й = = О, 1,2п) от всех одноразряд- ных сумматоров и формирования общего сигнала о 1 дибки в работе устройства.Элемент ИЛИ 2 .служит для сборки сигналов переносов, которые выходят за пределы старшего разряда, и формирования сигнала переполнения ( разрядной сетки сумматора.Четырехвходовые одноразрядные сумматоры 3 предназначены для суммирования сигналов переносов и цифр слагаемых в двух старших и двух млад. ших разрядах кодов слагаемых, а также для фиксации ошибок в работе устройства Пятивходовые одноразрядные сумматоры 4 служат для суммирования сигналов переносов и цифр слагаемых во.2-(и) разрядах кодов слагаемых, а также для фиксации ошибок в работе устройства.Элемент ИЛИ 5 предназначен для сборки сигналов контроля одноразряд11808 1 О ного сумматора младшего разряда при различных режимах работы устройства и формирования общего сигнала ошибки.Элемент И 6 служит для формирования сигнала ошибки в младшем разряде устройства в режиме суммирования кодов Фибоначчи, Второй вход данного элемента является инверсным.Элемент И 7 предназначен для выполнения округления кода результата в режиме суммирования кодов "золотой" 1-й пропорции посредством передачи сигнала переноса в ( С)-й разряд из первого разряда в нулевой. Вход задания режима сумматора 8 служит для задания путем установки на нем "О" или "1" режима суммирова 11 ния кодов Фибоначчи или кодов золотой" 1-й пропорции соответственно.На чертеже переносы, сформированные в С-м одноразрядном сумматоре и поступающие на вход ш-го одноразрядного сумматора, обозначаются Рф ыОдноразрядные четырех- и пятивходовые сумматоры могут быть построены, например, на базе постоянного запоминающего устройства, где входачи слагаемых являются адресные входы.Устройство работает следующим образом.Так как слагаемые поступают на вход сумматора в нормальной форме, т.е. в двух соседних разрядах кода слагаемого одновременно не могут на ходиться единицы, то при исправной работе сумматора на входах четырехвходовых одноразрядных сумматоров не могут появиться четыре единичных сигнала одновременно, а на входах пяти входовых одноразрядных сумматоров - пять единичных сигналов, данное свойство используется для контроля одноразрядных сумматоров.С учетом изложенного выше суммиро вание в -м одноразрядном сумматоре происходит следующим образом:если на входах сумматора единичных сигналов нет, то единичные Сигналы переносов в другие разряды не воз. 50 никают, и формируется нулевой сигнал суммы в разряде;если на входах сумматора один единичный сигнал, то единичные сигналы переносов не возникают, формируется 55 единичный сигнал суммы в разряде;если на входах сумматора два единичных сигнала, то формируются еди 80 4ничные сигналы переносов в (С+1) "й и в (7-2)-й разряды и нулевой сигнал суммы в данном разряде;если на входах сумматора три единичных сигнала, то формируются единичные сигналы переносов в (9+2)-й и (-2)-й разряды и нулевой сигнал суммы в данном разряде;если на входах сумматора четыре единичных сигнала при исправной работе (этот случай возможен только в пятивходовых одноразрядных сумматорах), то формируются единичные сигналы переносов в ( С+2)-й и (С)-й разряды и единичный сигнал суммы в данном разряде.Кроме того, режим сложения кодов "золотой" 1-й пропорции реализуется за счет организации цепей переносов из нулевого в первый и второй разряды, а также из первого разряда в ну-, левой. При этом осуществляется округление результата посредством отбрасывания переноса из нулевого разряда в (-2)-й разряд и подсуммирование переноса из первого разряда в ( С)-й разряд на сумматоре нулевого разряда.На основе данной логики строится параллельный сумматор для кодов Фибоначчи и "золотой" 1-й пропорции,Перед началом суммирования посредством входа 8 задания режима работы устанавливается режим суммирования кодов Фибоначчи или "золотой" 1-й пропорции.В случае суммирования кодов Фибоначчи на входе 8 устанавливается нулевой сигнал, в результате чего посредством элемента И 1.от первого входа переноса одноразрядного сумматора нулевого разряда отключаетсяФцепь переноса первого разряда. Кроме того, нулевой сигнал поступает на инверсный вход элемента И 6, в результате на выходе элемента ИЛИ 5 формируется сигнал ошибки в младшем разряде сумматора, если на вход одноразрядного сумматора нулевого разряда одновременно поступает больше одного единичного сигнала.1В случае суммирования кодов золотой" 1-й пропорции на входе 8 устанавливается единичный сигнал, в результате цепь переноса первого разряда подключается к входу одноразрядного сумматора нулевого раз. ряда, а сйгнал ошибки в младше;:разряде сумматора формируется на выходе элемента ИЛИ 5, если навходы одноразрядного сумматора нулевого разряда одновременно поступают четыре единичных сигнала,Затем на шины 9 и 10 слагаемыхпоступают коды слагаемых в нормальной форме (А и В):10А = а,а,а а,.аВ Ь Ьпр рЬЪ 1 Ьгде аВ,Ъ - двоичные цифры в 1-м раз.ряде кода ( = 0,1и) .Далее формируются переносы вкаждом одноразрядном сумматоре и первая промежуточная сумма, осуществляется подсуммирование переносов, образование второй промежуточной сум мы и новых переносов; И так до тех пор, пока не прекратится образование переносов и на выходах одноразрядных сумматоров 3 и 4 не образует ся код суммы8-1 Во-т 8 о-з 8 х 8 огде Ы - двоичные цифры в 1-м разряде кода ( = 0,1 п).В дальнейшем этот код переписывается из сумматора на нормализатор,где с помощью операции свертки происходит нормализация кода результата.Если при суммировании нарушено контрольное соотношение, то формируется соответствующий единичный сигнал К, который поступает на соответствующий вход элемента ИЛИ 1 и40 порождает на его выходе сигнал ошибки К. При этом сигнал ошибки в нулевом разряде устройства, в случае суммирования кодов Фибоначчи, формируется исходя из того, что в45 нулевых разрядах суммируемых кодов должны быть нули и заблокированацепь переноса из первого разряда в нулевой, а следовательно, при исправной работе устройства на входах одноразрядного сумматора нулевого разряда не может одновременно появиться более одного единичного сигнала, т.е. единичный сигнал на вьюходах Ко или Р эданного одноразрядного сумматора сигнализирует об ошибке.Если при суммировании возникают переносы, которые выходят за пределы старшего разряда сумматора, то посредством элемента ИЛИ 2 формируется сигнал переполнения разрядной сетки устройства Я .П р и м е р 1. Сложение кодовФибоначчи А = 000101010 и В =000100000:1-я промежуточнаясумма 000001010возникшие переносы 1 12-я промежуточнаясумма 001000010возникшие переносы 13-я промежуточнаясумма 001010 СООвозникшие переносы 1код суммы 001010100В данном случае код суммы полученв нормальной форме.П р и м е р 2. Сложение кодовМ ю 31 -й акаэ 5926/47 Тираж 709 Подпнсн иал ППП "Патент", г.Ужгород, ул.Проектн

СмотретьЗаявка

3726204, 06.04.1984

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

КРЕМЕЗ ГЕОРГИЙ ВАЛЬТЕРОВИЧ, БАРАНОВ ИГОРЬ АЛЕКСЕЕВИЧ, РОЗДОБАРА ВИТАЛИЙ ВЛАДИМИРОВИЧ, ПЕХТЕРЕВ ЮРИЙ ГАВРИЛОВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: кодов, параллельный, сумматор, фибоначчи

Опубликовано: 23.09.1985

Код ссылки

<a href="https://patents.su/5-1180880-parallelnyjj-summator-kodov-fibonachchi.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный сумматор кодов фибоначчи</a>

Предыдущий патент: Устройство для сравнения кодов

Следующий патент: Устройство для умножения

Случайный патент: Способ раскатки колец и оправка для его осуществления