Сумматор в коде “м из

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

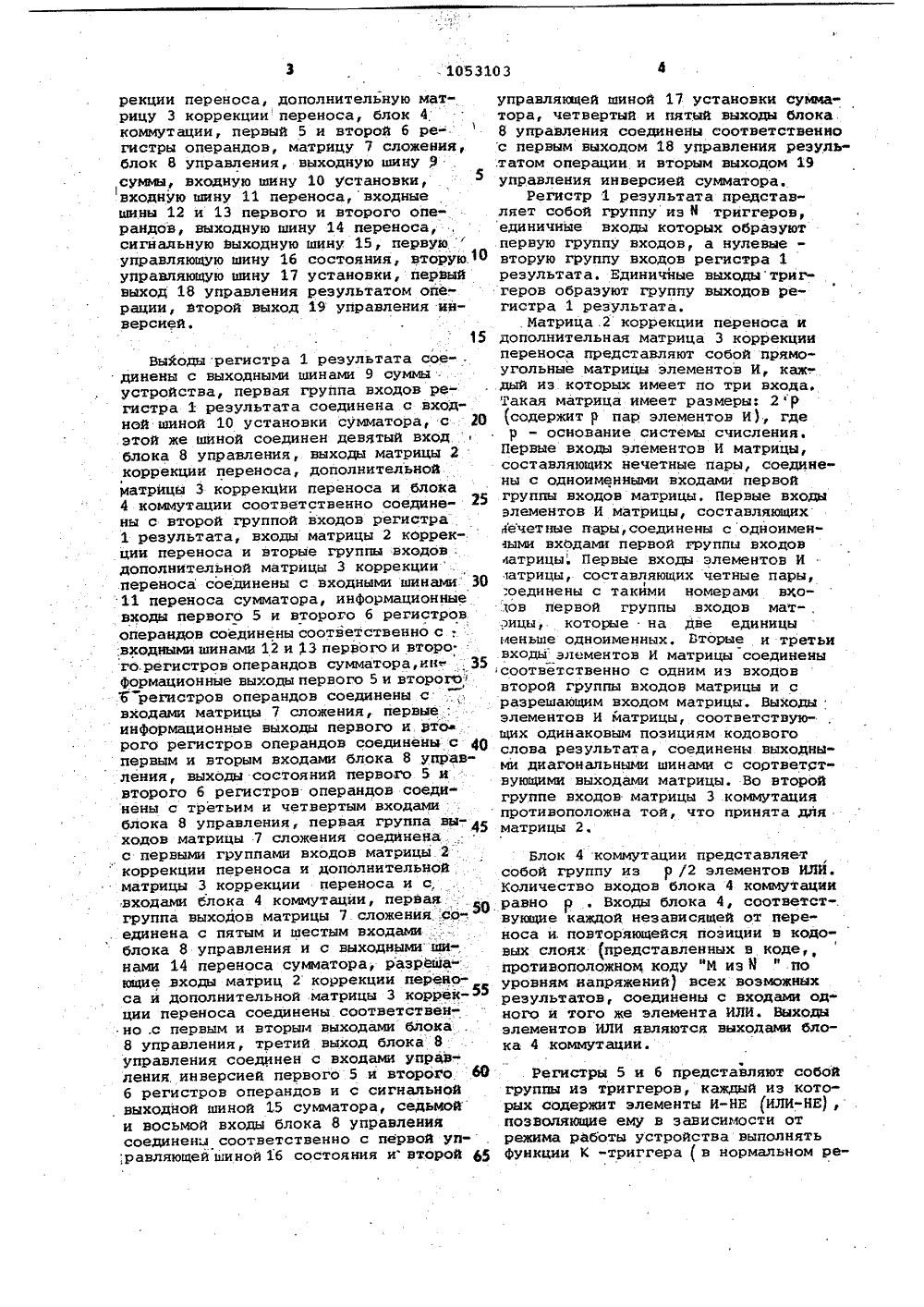

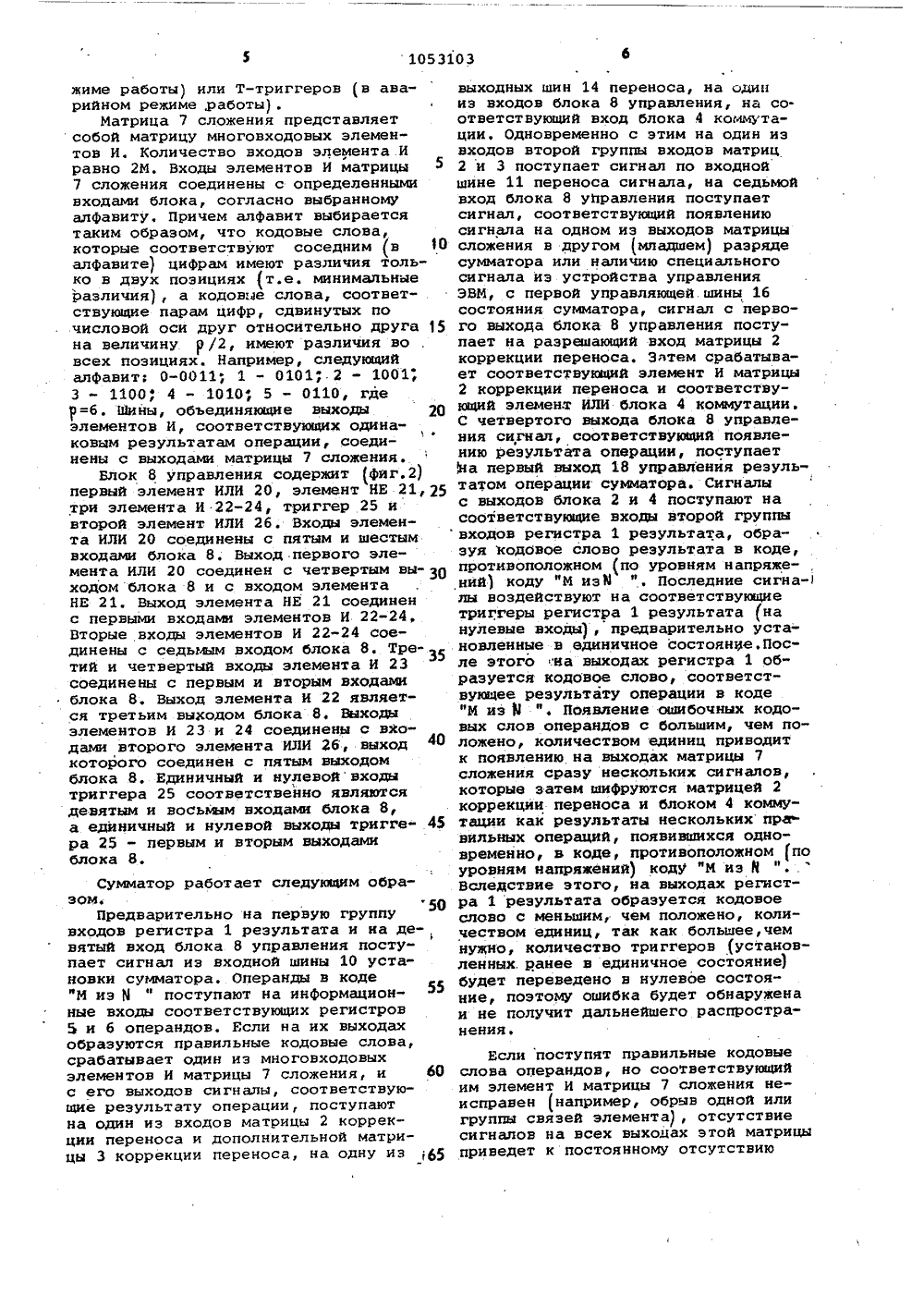

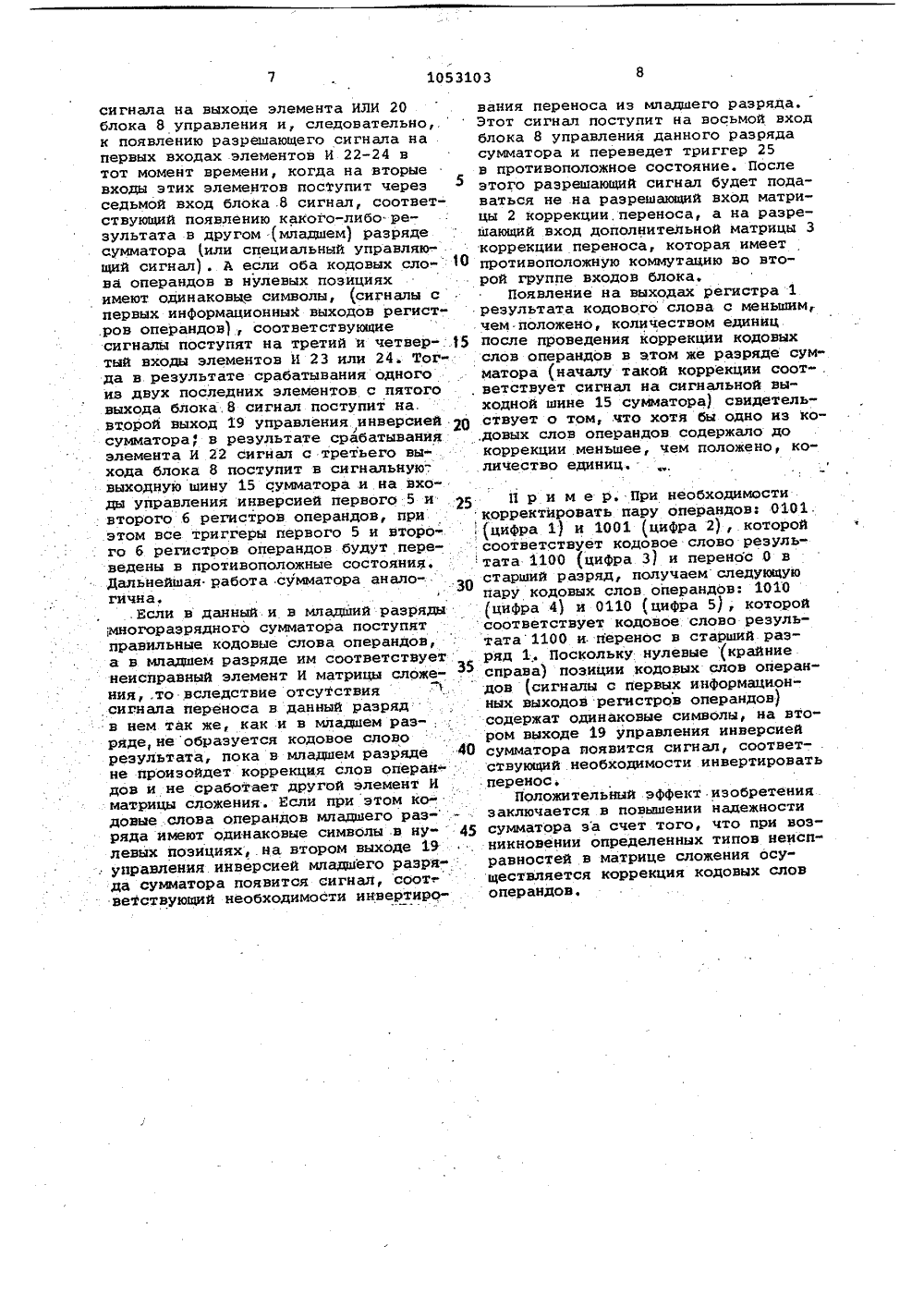

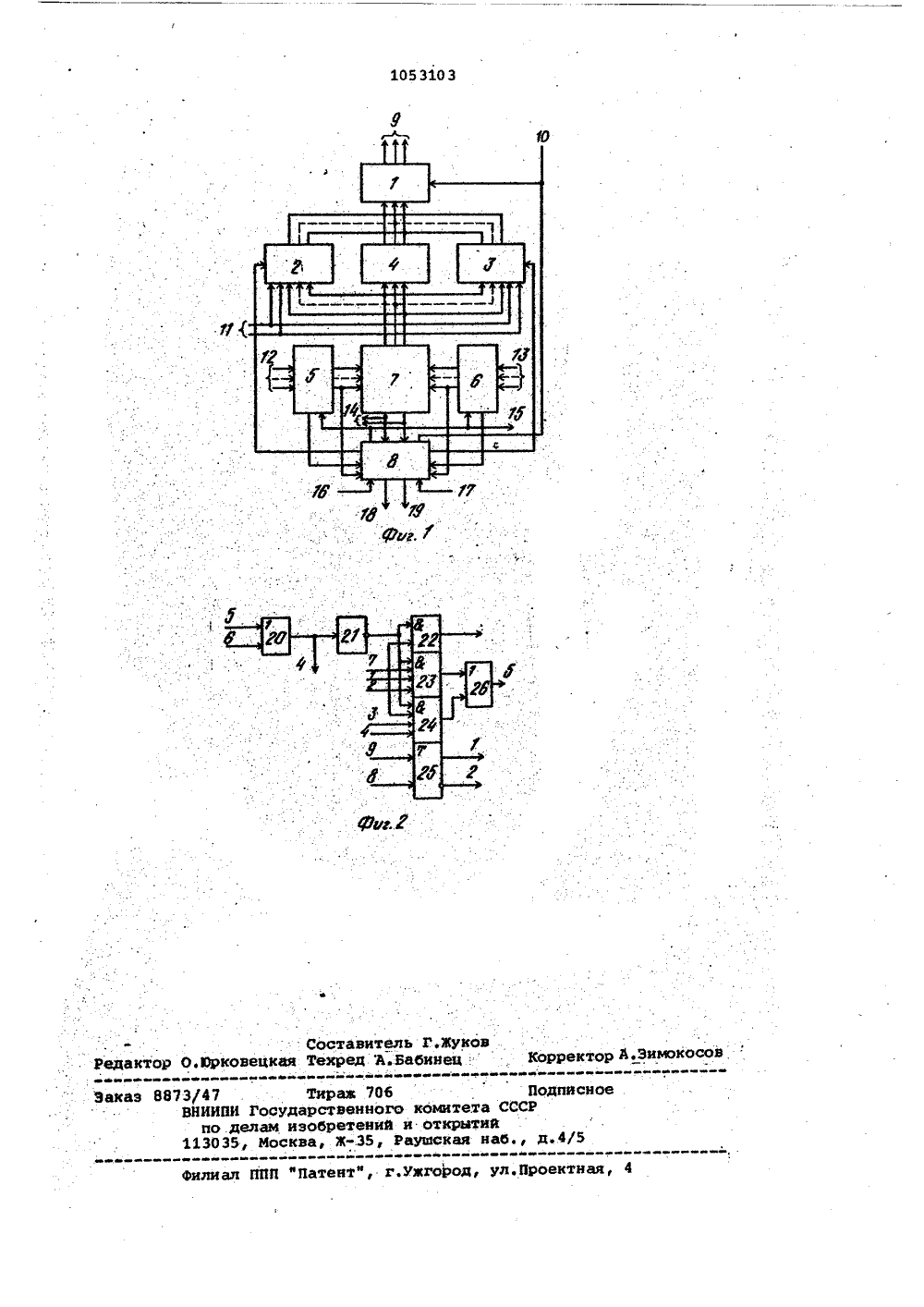

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 19) Я 3(51) б 06 Р ВУ мвыв ды тре- треть- выся третього и ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМУСВИДЕТ(72) В.А.Гуменюк и Н.Н.Сиверская (71) Киевский ордена Трудового Красного Знамени институт инженеров гражданской авиации(56) 1. Авторское свидетельство СССР 9 873238,кл. 6 06 Г 7/49,1980 прототип (54) (57) СУММАТОР В КОДЕ "М ИЗ М " по автсв, В 873238, о т л и ч а ю щ и йс я тем, что, с целью повышения его надежности за счет коррекции кодовыхслов операндов, он содержит дополнительную матрицу коррекции переноса, первый и второй регистры операндов и блок управления, причем выходы до- полнительной матрицы коррекции переноса соответственно соединены с второй группой входов регистра результата, первая и вторая группы входов дополнительной матрицы коррекции переноса соединены соответственно с второй группой выходов матрицы сложения и с входными шинами переноса . сумматора, информационные входы первого и второго регистров операндов соединены соответственно с входными шинами первого и второго регистров операндов сумматора, информационные входы первого и второго регистров операндов соединены с входами матри цы сложения, первые информационные выходы первого и второго регистров операндов соединены с первым и вторым входами блока управления, выходы состояйий первого и второго регистров операндов соединены с третьим и четвертым входами блока управления, первая группа выходов матриц сложения соединена с пятым и шестым входаьы блока управления, седьмой, восьмой и девятый входы блока управления соединены соответственно с первой управляющей шиной состояния, с второй управляющей шиной установки и с входной шиной установки суююатора, первый и второй выходы блока управления соединены с разрешающими входами соответственно матрицы коррекции переноса и дополнительной атрицы коррекции перекоса, третийход блока управления соединен сходами управления инверсией первого и второго регистров операндов и с сигнальной выходной шиной .сумматора, четвертый и пятый выходы блока управления соединены соответственно с первым выходом управления результатом операции и вторым выходом уп-равления инверсией сумматора, причем блок управления содержит элементы ИЛИ, элемент НЕ, три элемента И и триггер, входы первого элемента ИЛИ соединены с пятым и шестым входами блока, выход первого элемен- ф та ИЛИ соединен с четвертым выходом блока и с входом элемента НЕ, выход элемента НЕ соединен с первыми входами всех элементов И, вторые входы всех элементов И соединены с седьмым входом блока, третий и четвертый входы второго элемента И соединены с первым и вторым входами блока, третий и четвертый вхо тьего элемента И соединены с им и четвертым входами блока, ход первого элемента И являет им выходом блока выходы втор третьего элементов И соединены с входами второго элемента ИЛИ, выход которого соецинен с пятым выходом блока, единичный и нулевой входы триггера являются соответственно девятым и восььим входами блока, еди-. ничный и нулевой выходы триггера являются срответственно первым и вторым выходами блока,1 О 531 О 3 Изобретение относится к вычислительной технике и предназначено для суммирования чисел, представленных в коде "М из 8 " (где И - количество позиций в кодовом слове, М -,количество единиц в кодовом слове) .По основному авт.св, Р 873238 известен сумматор в коде "М из И содержащий регистр результата, матрицу сложения, матрицу коррекции переноса и блок коммутации, причем 1 О входы матрицы сложения соединены соответственно с входными шинами первого и второго операндов сумматора, выходы;регистра результата - с выходными шинами сумматора, первая 15 группа входов регистра результата соединена с входной шиной установки сумматора, первая группа выходов матрицы сложения - с выходными шинами сумматора, вторая группа выходов 20 матрицы сложения - с первой группой . входов матрицы коррекции переноса., те из этих выходов, которым соответствуют независимые от переноса не- повторяющиеся позиции в кодовых сло-. 25 вах всех возможных результатов, соединены непосредственно с соответст. вующими входами второй группы входов регистра результата, другие выходы второй группы выходов матрицы сло.- жения, которым соответствуют независимые от переноса повторяющиеся позиции в кодовых словах всех возможных результатов, соединены с входами блока коммутации, выходы блока коммутации соединены с соответствующими входами второй группы входов регистра результата, вторая группа входов матрицы коррекции переноса .соединена с входными шинами перено- са сумматора 11 .40 Недостатком устройства является то, что возникновение неисправностей, например обрыв любой связи в матрице сложения, содержащей большую 45 часть элементов устройства, приводит к потере функциональной полноты последним, т,ек выходу из строя всего устройства.Целью изобретения является повы,шение надежности сумматора в коде "М из К ф за счет коррекции кодовыхслов операндов.Поставленная цель достигается тем, что сумматор в коде "М из Ю " содержит дополнительную матрицу коррекции переноса, первый и второй регистры операндов и блок управления, причем выходы дополнительной матрицы коррекции переноса соответственно соединены с второй группой входов бО регистра результата, первая и вторая группы входов дополнительной матрицы коррекции переноса соединены соответственно с второй группой выходов матрицы сложения и с входными шиками переноса сумматора, информационные входы первого и второго регистров операндов соединены соответственно с входными шинами первого и второго регистров операндов сумматора,информационные входы первого и второго регистров операндов соединены свходами матрицы сложения, первые инФормационные выходы первого и второго регистров операндов соединены спервым и вторым входами блока управления, выходы состояний первого ивторого регистров операндов соединены с третьим и четвертым входамиблока управления, первая группа выходов матрицы сложения соединена спятым и шестым входами блока управления, седьмой, восьмой .и девятыйвходы блока управления соединены соответственно с первой управляющей шиной состояния, с второй управляющейшиной установки и с входной. шинойустановки сумматора, первый и второйвыходы блока управления соединены сразрешающими входами соответственноматрицы коррекции переноса и дополнительной матрицы коРрекции переноса,третий выход блока управления соединен с входами управления инверсиейпервого и второго регистров операн- .дов и с сигнальной выходной шинойсумматора, четвертый и пятый выходы блока управления соединены соответственно с первым выкодом управления результатом операции и вторым выходом управления инверсией с 3 ммато.- ра, причем блок управления содержит элементы ИЛИ, эЛемент НБ, три элемента И и триггер, входы первого элемента ИлИсоединены с пятым и шестым входами блока, выход первого элемента ИЛИ соединен с четвертым выходом блока и с входом элемента НВ, выход элемента НЕ .соединен с первыми входами всех элементов И, вторые входы всех элементов И соединены с седьмым входом блока, третий и четвертый входы второго элемента И соединены с первым и вторым входами блока третйй и четвертый входы третьего элемента И соединены с третьим и четвертым входами блока, выход первого элемента И является третьим выходом блока, выходы второго и третьего элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с пятым выходом блока, единичный и нулевой входы триггера являются соответственно девятым и восьмым входами блока, единичный и нулевбй выходи триггера - первым и вторым выходами блока.На Фиг.1 изображена блок-схема, сумматора в коде "М из И "; на Фиг,2- схема блока управленйя. Сумматор Фиг,. 1 содержит регистр 1 результата, матрицу 2 коррекции переноса, дополнительную матрицу 3 коррекциипереноса, блок 4 коммутации, первый 5 и второй б регистры операндов, матрицу 7 сложения, блок 8 управления, выходную шину Я суммы, входную шину 10 установки, входную шину 11 переноса,входные шины 12 и 13 первого и второго операндов, выходную шину 14 переноса, сигнальную выходную шину 15, первуюуправляющую шину 16 состояния, вторую 1 О управляющую шину 17 установки, первый выход 18 управления результатом операции, второй выход 19 управления инверсией.15Выходы регистра 1 результата сое- .динены с выходными шинами 9 суммыустройства, первая группа входов регистра 1 результата соединена с вход-.ной шиной 10 установки сумматора, с 30этой же шиной соединен девятый входблока 8 управления, выходы матрицы 2коррекции переноса, дополнительнойматрицы 3 коррекцИи переноса и блока4 коммутации соответственно соединены с второй группой входов регистра1 результата, входы матрицы 2 коррек.ции переноса и вторые группы входов: дополнительной матрицы 3 коррекции переноса соединены с входными шинами 3011 переноса сумматора, информационныевходы первого 5 и второго б регистров. операндов соединены соответственно с;. входными шинами 12 и 13 первого и второго,регистров операндов сумматора,ин 35 формационные выходы первого 5 и второгоб регистров операндов соединены с входами матрицы 7 сложения, первые: информационные выходы первого и это рого регистров операндов соединены с 4 О первым и вторым входами блока 8 управления, выходы состояний первого 5 и второго б регистров операндов соединены с третьим и четвертым входами блока 8 управления, первая группа вы ходов матрицы 7 сложения соединена с первыми группами входов матрицы 2 коррекции переноса и дополнительной матрицы 3 коррекции переноса и с, входами блока 4 коммутации, первая группа выходов матрицы 7 сложения .со-, . единена с пятым и шестым входами; блока 8 управления и с выходными ши нами 14 переноса сумматора, разреша"ющие входы матриц 2 коррекции переноса и дополнительной .матрицы 3 коррекции переноса соединены соответствен- но,с первым и вторым выходами блока 8 управления, третий выход блока 8 управления соединен с входаьи управления, инверсией первого 5 и второго 66 б регистров операндов и с сигнальной , выходной шиной 15 сумматора, седьмой и восьмой входы блока 8 управления соединены соответственно с первой уп,равляющей шиной 16 состояния и второй я управляющей шиной 17 установки сумма" тора, четвертый и пятый выходы блока 8 управления соединены соответственно с первым выходом 18 управления резуль.татом операции и вторым выходом 19 управления инверсией сумматора,Регистр 1 результата представляет собой группу из М триггеров, единичные входы которых образуют первую группу входов, а нулевыевторую группу входов регистра 1 результата, Единичные выходытриггеров образуют группу выходов регистра 1 результата.Матрица.2 коррекции переноса и дополнительная матрица 3 коррекции переноса представляют собой прямоугольные матрицы элементов И, каж-. дый из которых имеет по три входа. Такая матрица имеет размерыг 2 содержитпар элементов И), где р - основание системы счисления.Первые входц элементов И матрицы, составляющих нечетные пары, соединены с одноименными входами первой группы входов матрицы. Первые входы элементов И матрицы, составляющих нечетные нары, соединены содноименными входами первой группы входов матрицы. Первые входы элементов И атриды, составляющих четные пары, :оединены с такими номерами вхоюв первой группы входов мат-, рицы,. которые на две единицы меньше одноименных. Вторые и третьи входы элементов И матрицы соединены соответственно с одним из входов второй группы входов матрицы и с разрешающим входом матрицы. Выходы элементов И матрицы, соответствующих одинаковым позициям кодового слова результата, соединены выходными диагональными шинами с сортветствующими выходами матрицы. Во второй группе входов матрицы 3 коммутация противоположна той, что принята для матрицы 2. Блок 4 коммутации представляет собой группу из р /2 элементов ИЛИ. Количество входов блока 4 коммутации равно р . Входы блока 4, соответст-. вующие каждой независящей от иере- носа и. повторяющейся позиции в кодовых слоях представленных в коде противоположном коду "И из М ф по уровням напряжений) всех возможных результатов, соединены с входами одного и того же элемента ИЛИ, Выходы элементов ИЛИ являются выходами блока 4 коммутации.Регистры 5 и б представляют собой группы из триггеров, каждый из которых содержит элементы И-НЕ ИЛИ-НЕ), позволяющие ему в зависимости от режима работы устройства выполнять Функции К -триггера ( в нормальном ре1053103 жиме работы) или Т-триггеров (в аварийном режиме, работы).Матрица 7 сложения представляет собой матрицу многовходовых элементов И. Количество входов элемента И равно 2 М. Входы элементов И матрицы 7 сложения соединены с определенными входами блока, согласно выбранному алфавиту. Причем алфавит выбирается таким образом, что кодовые слова, которые соответствуют соседним (в 10 алфавите) цифрам имеют различия только в двух позициях (т,е. минимальные различия), а кодовые слова, соответствующие парам цифр, сдвинутых по ние, поэтому ошибка будет обнаруженаи не получит дальнейшего распространения,60 сигналов на всех выходах этой матрицыприведет к постоянному отсутствию с 65 числовой оси друг относительно друга 15 на величину /2, имеют различия во всех позициях. Например, следующий алфавит: 0-0011; 1 - 0101; 2 - 1001;, 3 - 1100 ф 4 - 1010; 5 - 0110, где =6. Шины, объединяющие выходы 20 элементов И, соответствующих одинаковым результатам операции, соединены с выходами матрицы 7 сложения.Блок 8 управления содержит фиг.2) первый элемент ИЛИ 20, элемент НЕ 21, 25 три элемента И 22-24, триггер 25 и второй элемент ИЛИ 26, Входы элемента ИЛИ 20 соединены с пятым и шестым входами блока 8. Выход первого элемента ИЛИ 20 соединен с четвертым вы- З 0 ходом блока 8 и с входом элементаНЕ 21Выход элемента НЕ 21 соединенс первыми входами элементов И 22-24,Вторые входы элементов И 22-24 соединены с седьмым входом блока 8. Тре- З 5тий и четвертый входы элемента И 23соединены с первым и вторым входамиблока 8. Выход элемента И 22 является третьим выходом блока 8. Выходыэлементов И 23 и 24 соединены с входами второго элемента ИЛИ 26, выход 40которого соединен с пятым выходомблока 8. Единичный и нулевой входытриггера 25 соответственно являютсядевятым и восьмым входами блока 8,а единичный и нулевой выходы триггера 25 - первым и вторым выходамиблока 8. Сумматор работает следующим образом. 50 Предварительно на первую группу входов регистра 1 результата и иа де-, вятый вход блока 8 управления поступает сигнал из входной шины 10 уста" новки сумматора, Операнды в коде фМ из М " поступают на информационные входы соответствующих регистров Ь и 6 операндов, Если на их выходах образуются правильные кодовые слова,срабатывает один из многовходовыхэлементов И матрицы 7 сложения, ис его выходов сигналы, соответствующие результату операции, поступаютна один из входов матрицы 2 коррекции переноса и дополнительной матрицы 3 коррекции переноса, на одну из выходных шин 14 переноса, на одиниз входов блока 8 управления, на соответствующий вход блока 4 коммутации, Одновременно с этим на один извходов второй группы входов матриц2 и 3 поступает сигнал по входнойшине 11 переноса сигнала, на седьмойвход блока 8 управления поступаетсигнал, соответствующий появлениюсигнала на одном из выходов матрицысложения в другом младшем) разрядесумматора или наличию специальногосигнала из устройства управленияЭВМ, с первой управляющей. шины 16состояния сумматора, сигнал с первого выхода блока 8 управления поступает на разрешающий вход матрицы 2коррекции переноса, Зачтем срабатывает соответствующий элемент И матрицы2 коррекции переноса и соответствующий элемент ИЛИ блока 4 коммутации.С четвертого выхода блока 8 управления сигнал, соответствующий появлению результата операции, поступаетЬа первый выход 18 управления результатом операции сумматора. Сигналыс выходов блока 2 и 4 поступают насоответствующие входы второй группывходов регистра 1 результата, образуя кодовое слово результата в коде,противоположном (по уровням напряжений) коду "М изй ф. Последние сигна-лы воздействуют на соответствующиетриггеры регистра 1 результата 1 нанулевые входы), предварительно установленные в единичное состояние.После этого .на выходах регистра 1 образуется кодовое слово, соответствующее результату операции в кодефМ из Й ". Появление ошибочных кодовых слов операндов с большим, чем положено, количеством единиц приводитк появлению на выходах матрицы 7сложения сразу нескольких сигналов,которые затем шифруются матрицей 2коррекции переноса и блоком 4 коммутации как результаты нескольких правильных операций, появившихся одновременно, в коде, противоположном 1 поуровням напряжений) коду "М из яВследствие этого, на выходах регистра 1 результата образуется кодовоеслово с меньшим, чем положено, количеством единиц, так как большее,чемнужно, количество триггеров (установленных, ранее в единичное состояние)будет переведено в нулевое состояЕсли поступят правильные кодовые слова операндов, но соответствующий им элемент И матрицы 7 сложения неисправен (например, обрыв одной или группы связей элемента), отсутствиесигнала на выходе элемента ИЛИ 20блока 8 управления и, следовательнок появлению разрешающего сигнала напервых входах элементов И 22-24 втот момент времени, когда на вторыевходы этих элементов поступит черезседьмой вход блока .8 сигнал, соответствующий появлению какого-либо результата в другом (младшем) разрядесумматора 1 или специальный управляю-.щий сигнал), А если оба кодовых слова операндов в нулевых позицияхимеют одинаковые символы, (сигналы спервых информационных выходов регист.ров операндов), соответствующиесигналы поступят на третий и четвер-:15тый входы элементов И 23 или 24. Тогда в результате срабатывания одногоив двух последних элементов с пятоговыхода блока,8 сигнал поступит на.второй выход 19 управления инверсией росумматорами в результате срабатыванияэлемента Й 22 сигнал с третьего выхода блока 8 поступит в сигнальную-.выходную шину 15 сумматора и на входы управления инверсией первого 5 и 25второго б регистров операндов, приэтом все триггеры первого 5 и второ-.го б регистров операндов будут переведены в противоположные состояния.Дальнейшая работа сумматора анало"гична,;многоразрядного сумматора поступятправильные кодовые слова операндов,а в младшем разряде им соответствуетнеисправный элемент И матрицы сложениято вследствие отсутствиясигйала переноса в данный разрядв нем так же, как и в младшем раз-,ряде, не образуется кодовое словорезультата, пока в младшем разряде 40не произойдет коррекция слов операндов и не сработает другой элемент Иматрицы сложения. Если при этом кодовые слова операндов младшего раз-. -ряда имеют одинаковые символы в нулевых позициях, на втором выходе 19: управления инверсией младшего разря:да сумматора появится сигнал, соот-,ветствующий необходимости инвертирования переноса из младшего разряда,Этот сигнал поступит на восьмой входблока 8 управления данного разрядасумматора и переведет триггер 25в противоположное состояние. Послеэтого разрешающий сигнал будет подаваться не на разрешающий вход матрицы 2 коррекции, переноса, а на разрешающий вход дополнительной матрицы 3коррекции переноса, которая имеетпротивоположную коммутацию во второй группе входов блока.Появление на выходах регистра 1результата кодового слова с меньшим,чем положено, количеством единицпосле проведения коррекции кодовыхслов операндов в этом же разряде сумматора (началу такой коррекции соот- .ветствует сигнал на сигнальной выходной шине 15 сумматора) свидетельствует о том, .что хотя бы одно из кодовых слов операндов содержало докоррекции .меньшее, чем положено, количество единиц,П р и м е р. При необходимостикорректировать пару операндов: 0101.(цифра 1) и 1001 цифра 2), которойсоответствует кодовое слово результата 1100 (цифра 3) и перенос 0 встарший разряд, получаем следующуюпару кодовых слов операндов: 1010(цифра 4) и 0110 (цифра 5), которойсоответствует кодовое слово результата 1100 и перенос в старший разряд 1 Поскольку нулевые (крайниесправа) позиции кодовых слов операндов (сигналы с первых информационных выходов регистров операндов)содержат одинаковые символы, на втором выходе 19 управления инверсиейсумматора появится сигнал, соответ- .ствующий необходимости инвертироватьперенос,ПОложительный эффект изобретениязаключается в повышении надежностисумматора за счет того, что при возникновении определенных типов неисправностей в матрице сложения осуществляется коррекция кодовых словоперандов,105 310 3 РР. Р Зимокосон конецкая юю ввюььееав Ю Ю ю Ю В Ю ВВФ Ю7ИПИ Госудо делам и035, Моск/5в Фв ав ю ва в в ю ю е ва вв е в ю ю т ю в Ьв т в ю ю е в ю ю е т Вв ав ав в ВЮЮ ЮЬВЮВВФилиал ППП фПатентф, г.ужгород, ул.Проектная, 4 втетеВававве Редактор а.врвВьВеееввеювВев Закан 8873/4ВНИ Составител Техред А,Бвююввтеею Тираж 706 рственного обретенийа, 3.35, Р Г.ЖуковбинецКорректоВююеюВЮЮЮВЬЮВВЕЮВВЕПодписноомитета СССРоткрытийуюская наб., д,4

СмотретьЗаявка

3457383, 25.06.1982

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ГУМЕНЮК ВИТАЛИЙ АЛЕКСАНДРОВИЧ, СИВЕРСКАЯ НОННА НИКОЛАЕВНА

МПК / Метки

МПК: G06F 7/49

Опубликовано: 07.11.1983

Код ссылки

<a href="https://patents.su/6-1053103-summator-v-kode-m-iz.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор в коде “м из</a>

Предыдущий патент: Одноразрядный адаптируемый четверичный сумматор

Следующий патент: Множительное устройство

Случайный патент: Рабочее оборудование экскаватора обратная лопата