Сумматор в коде “м из n

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 981992

Автор: Гуменюк

Текст

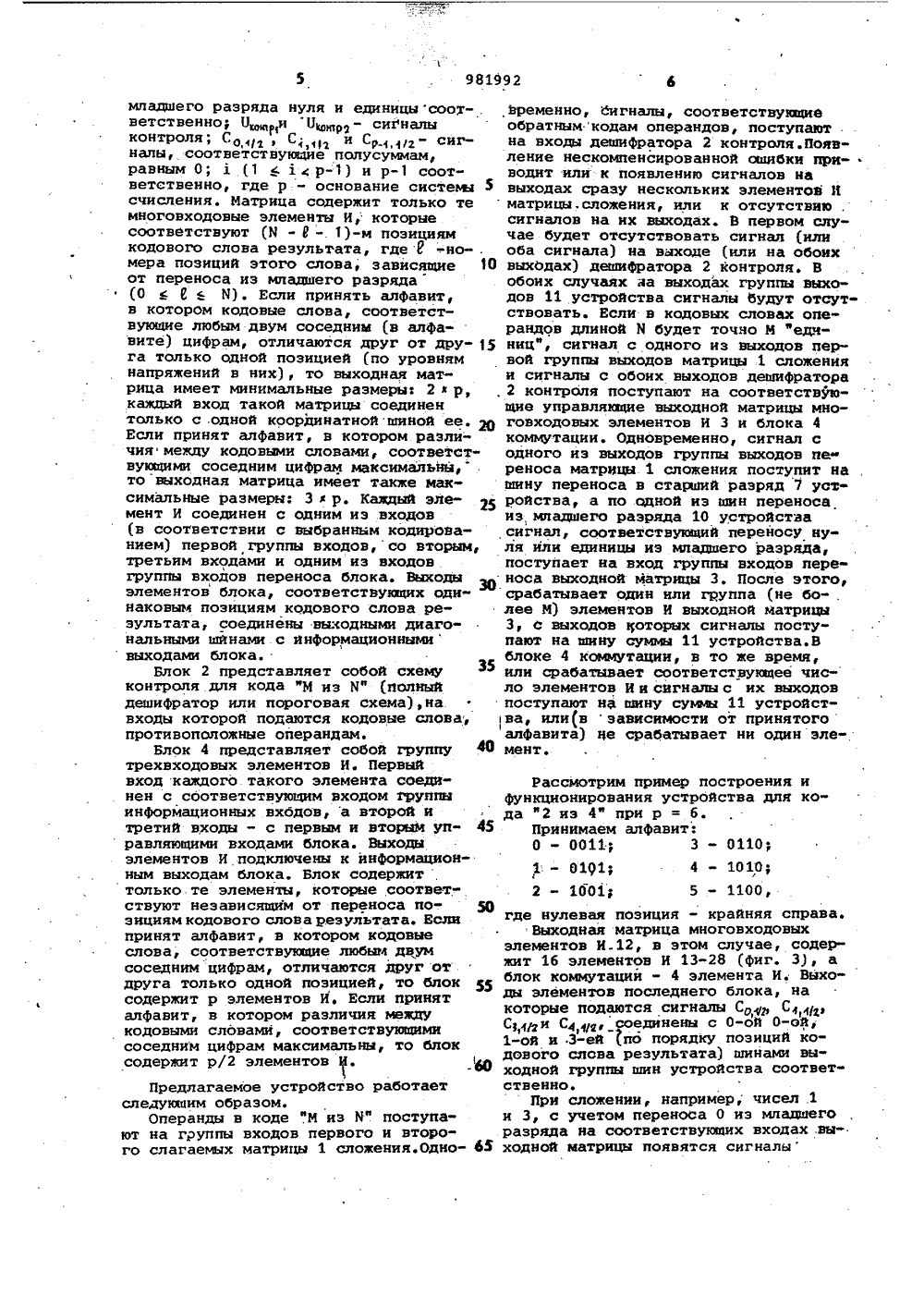

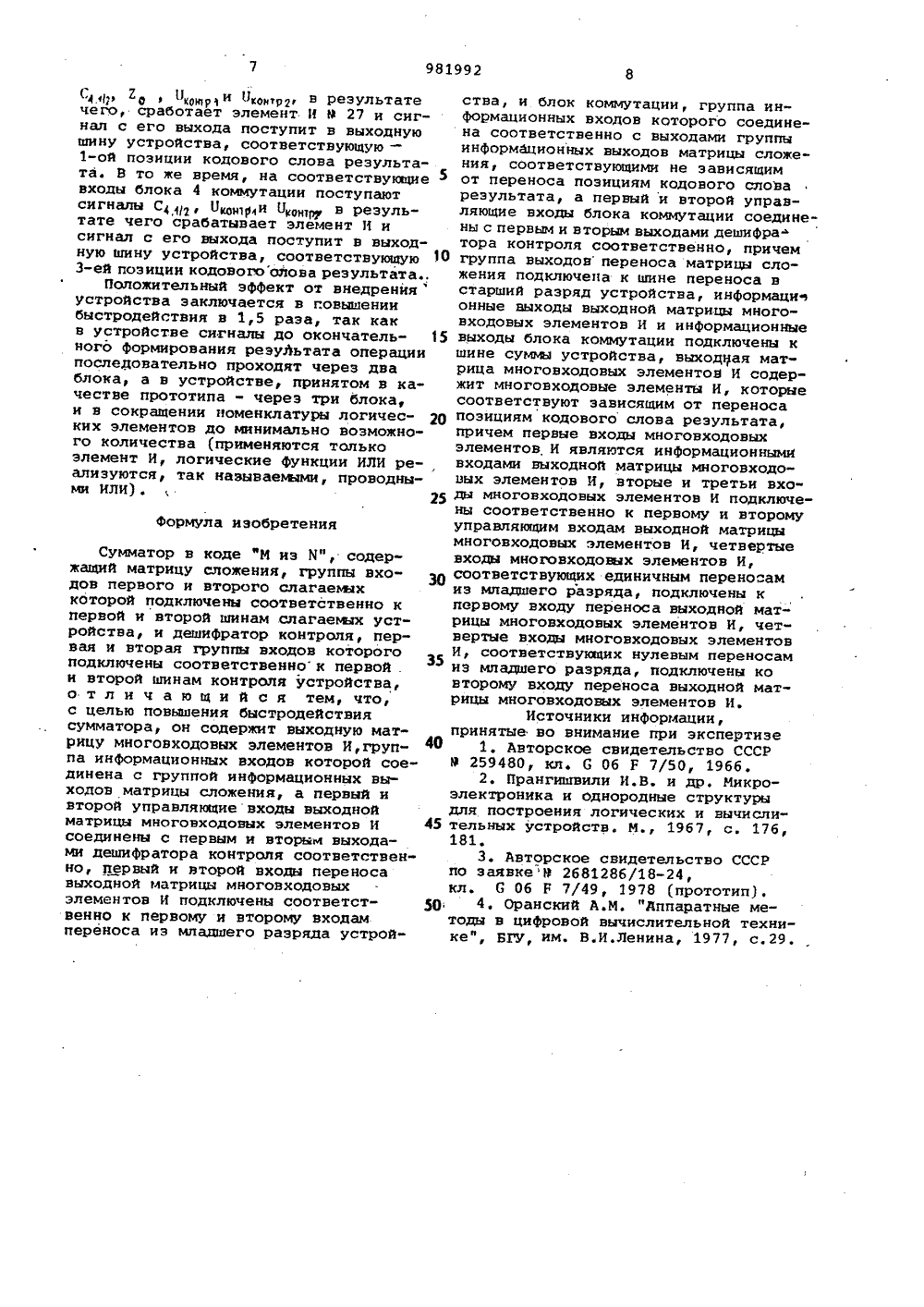

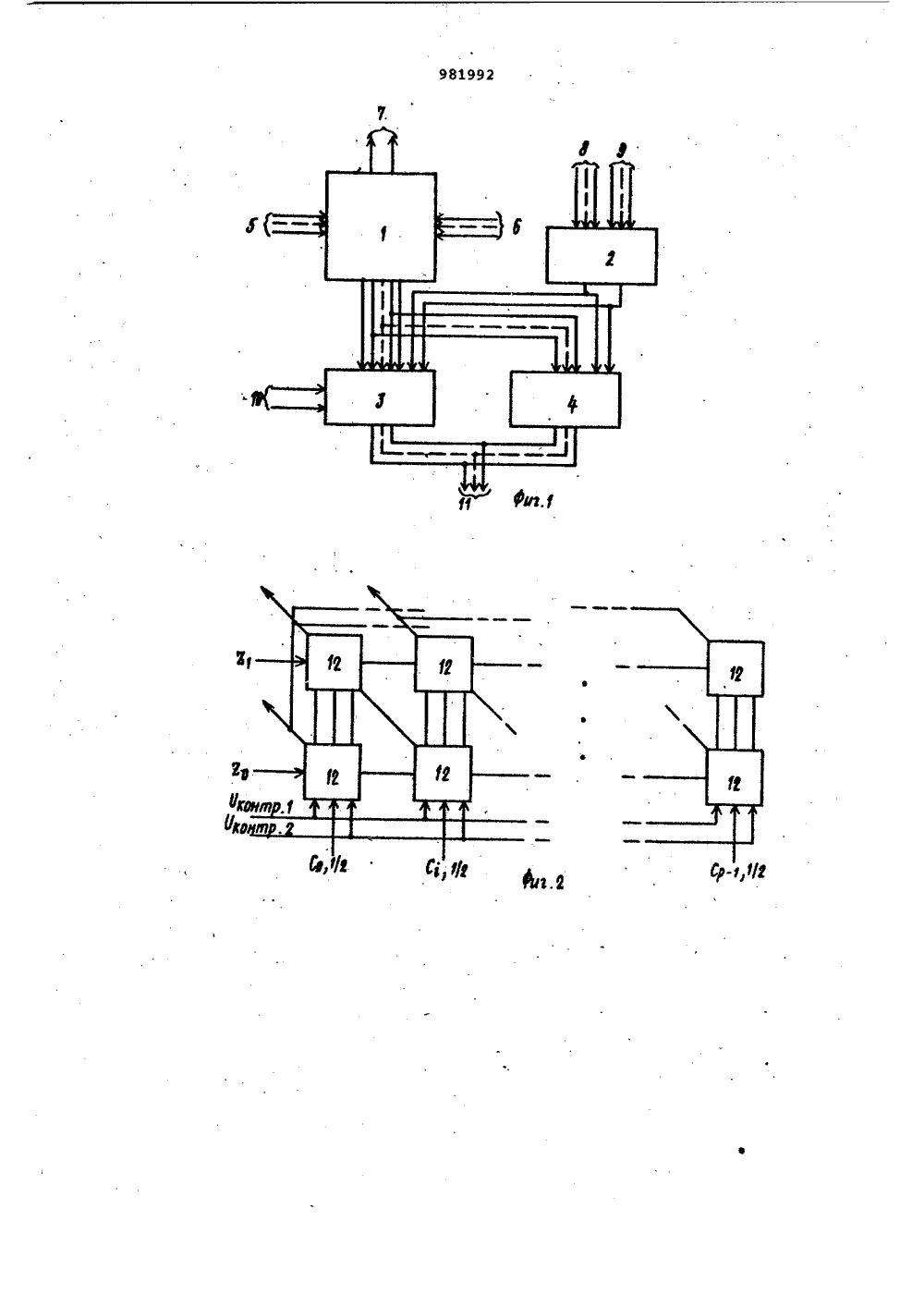

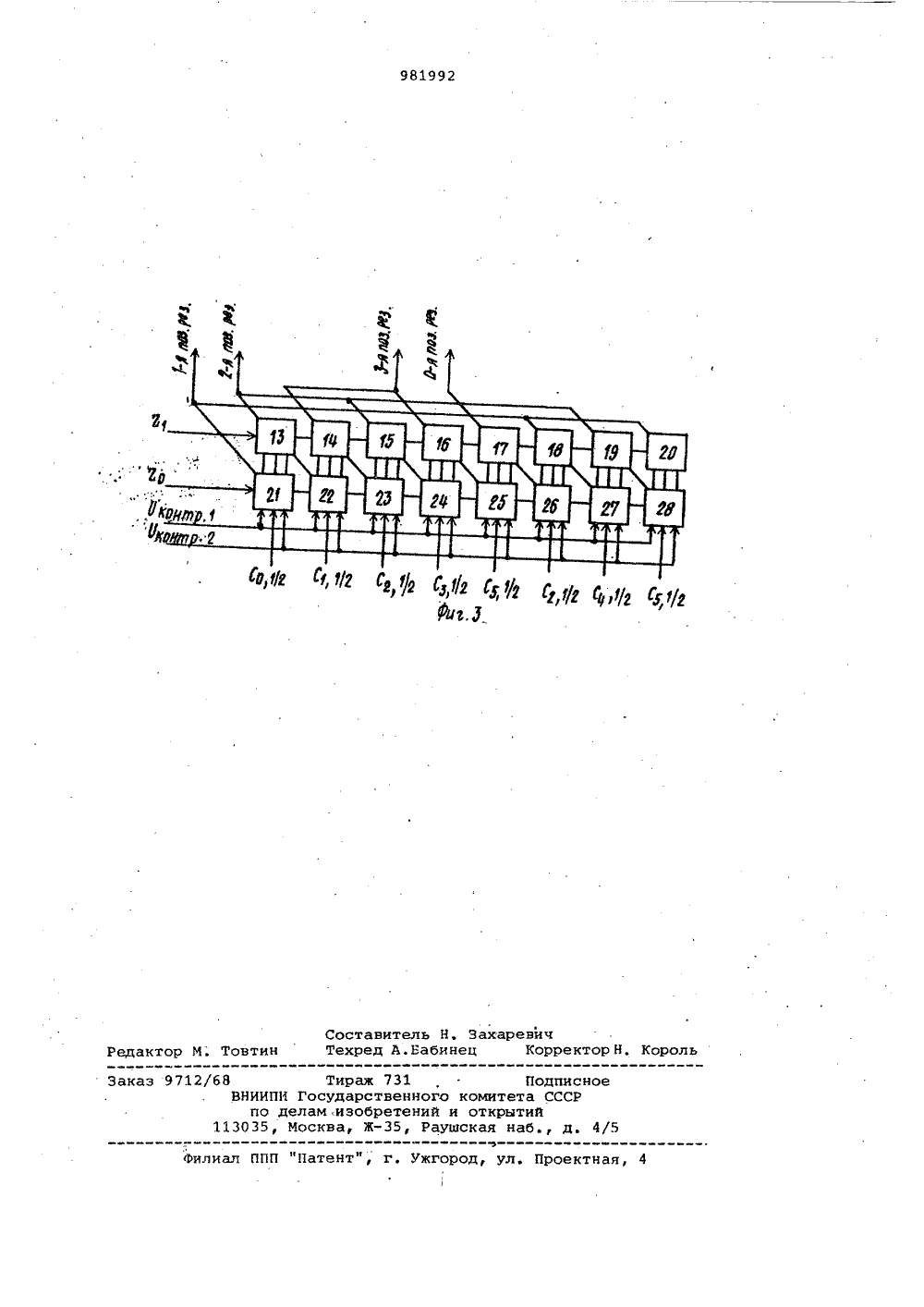

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскикСоциалистическихРеспублик нц 981992 К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22 Заявлено 25, 02. 81 (21 3251777/18-24 Р 1 М К з с присоединением заявки Йо(23) Приоритет -С Об Р 7/49 Государственный комитет СССР но делам изобретений и открытийОпубликовано 15,12,82.Бюллетень йо 46 Дата опубликования описания 15.12,82 53) УДК б 81.325(71) Заявитель вский ордена Трудового Красного Знинститут инженеров гражданской авиации(54) аевтоР в кодк ии из Кп Изобретение относится к вычислительной технике и предназначено для выполнения арифметических операций с числами, представленными в коде вМ из М"ф где Х - количество позиций в кодовом слове; М - количество единиц в кодовом слове.Известен двухразрядный сумматор в коде "2 из 5", содержащий местное уст ройство управления,преобразователи кодов операндов, матрицы элемЕнтов И, блоки коррекции, блоки переноса, шифратор младшего разряда и блоки выдачи старшего разряда сумьы ЯНедостатком этого устройства является низкое быстродействие, вследствие преобразования кодов операндов передподачей их на матрицы элементов И, прохождения сигналов, соответствующих по-. лусумме через двухступенчатый блок выдачи результата, состоящий иэ шифраторов н схем выдачи разряда суюи, а также низкого быстродействия самой матрицы элементов И.Известно также устройство для сум мнровання чисел, представленных в коде "1 иэ 10", содержащее матрицу сложения и матрицу сложения переносовГ 21 .Недостатком этого устройства является отсутствие контроля за выполне- З 0 нием арифметических операций. Кроме тогоу оно не предназначено для выполнения этих операций с числами, представленными в коде.вМ из Ив при М ъ 1, так как указанных вьаае блоков и свя эей между ними недостаточно для устранения недопустиьих гальванических связей между отдельными элементамн.входящими в состав блоков (связей, которые возникают при использовании кода вМ из И", где и1)Наиболее близким к изобретению является двухразрядный сумматор в коде фМ иэ Ми, старший разряд которого содержит матрицу сложения, блок переноса, шифраторы, блок контроля и блоки выдачи результата, причем две группы входов матрицы сложения соединены со входными шинами устройства, выходы матрицы сложения соединены со входаьщ блока переноса и шифрато- рОВ, выходы блока переноса соединены с выходными шинами устройства, выходы шифраторов соединены с первыми группами входов соответствующих блоков выдачи результата, две группы входов блока контроля соединены со входными шинами устройства, выходы блока контроля соединены со вторыми группами входов блоков выдачи результата, 3 981992третьи входы блоков выдачи результата соединены с соответствующими входами группы входов устройства, а вы ходы этих блоков являются выходами устройства ЗД .Недостатками этого устройства яв ляются сравнительно невысокое быстродействие из-за необходимости прохож. дения сигналов, соответствующих полу- суммам (с выходов матрицы сложения), через двухступенчатый блок выдачи результата, а также сравнительно сложная структура этого блока.Цель изобретения - повышение быстродействия сумматора в коде "М из И".15Поставленная цель достигается тем, что сумматор в коде "М из Я", содержащий матрицу сложения, группы входов первого и второго слагаемых которой подключены соответственно к первой и второй шинам слагаежх 0 устройства, и дешифратор контроля, первая и вторая группы входов которого подключены соответственно к первой и второй шинамконтроля устройства, содержит. выходную матрицу 25 многовходовых элементов И, группа инФормационных входов которой соединена с группой информационных выходов матрицы сложения,а первый и второй управляющие входы выходной матрицы 30 многовходовых элементов И соединены с первым;и вторым выходами дешифратора контроля соответственно, первый и второй входы переноса выходной матрицы многовходовых элементов И 35 подключены соответственно к первому и второму входам переноса из младшего разряда устройства, и блок коммутации, группа информационных входов которого соединена соответственно с 40 выходами группы информационных выходов матрицы сложения, соответствующими не зависящим от переноса позициям кодового слоя результата, а первый и второй управляющие входы блока коммутации соединены с первым и вторым выходами дешифратора контроля соответственно, причем группа выхо" дов переноса матрицы сложения подключена к шине переноса в старший разряд устройства, информационные выходы выходной матрицы многовходовых элементов И и информационные выходы блока коммутации подключены к шине суммы устройства, выходная матрица много- вхоцовых элементов И содержит много входовые элементы И, которые соответствуют зависящим от переноса позициям кодового слова результата, причем первые входы многовходовых элементов И являются информационными входами вы ходной матрицы многовходовых элементов И, вторые и третьи входы многовходовых элементов И подключены соответственно к первому и второму. управляющим входам выходной матрицы много входовых элементов И, четвертые входы многовходовых элементов И, состветствующих единичным переносам из младшего разряда, подключены к первому входу переноса выходной матрицы многовходовых элементов И, четвертые входы многовходовых элементов И,соответствующих нулевым переносам из юищшего разряда, подключены ко второму входу переноса выходной матрицы многовходовых элементов И.На Фиг. 1 представлена блок-схема сумматора в коде "М из Х"; на фиг.2 и 3 - схема выходной матрицы.Устройство содержит матрицу 1 сложения, дешифратор 2 контроля, выходную матрицу многовходовых элементов И 3 и блок 4 коммутации.Группы входов первого и второго слагаемых блока 1 подключены к первой и второй шинам слагаеиях 5, б устройства, группа информационных входов блока 3 соединена с группой информационных выходов блока 1,первый и второй управляющий входы блока 3 соединены с первым и вторымвыходами блока 2 соответственно, группавыходов переноса блока 1 подключенак шине переноса в старший разряд 7устройства, первая и вторая группывходов блока 2 подключены к первойи второй шинам контроля 8 и 9 устройства, группа входов переноса блока 3 подключена к шине переноса из младшего разряда устройства 10, группа информационных входов 4 соединена с выходами группы информационных выходов матрицы сложения, соответствукщими независящими от переноса позициям кодового слова результата, а первый и второй управляющие входы блока 4 подключены к первому и второму выходам блока 2 соответственно, информационные выходы блоков 3 и 4 подключены к шинам суьвк 11 устройства,Блок 1 представляет собой матрицу многовходовых элементов И, каждый из которых имеет по два гальванически независимых выхода 4 . Количество входов каждого элемента И равно 2 М. Входы элементов И блока соединены с шинами кодов операндов согласно выбранному алфавиту. Шины кодов операндов соединены со входами слагаемых блока. Шины, объединяющие первые выходы элементов, соответствуецих одинаковым значениям полусуюы, соединены с группой информационных выходов блока. Шины, объединяющие вторые выходы элемейтов, соответствующих одинаковым переносам встарший разряд, соединены с группой выходов переноса блока. Блок 3 представляет собой прямоугольную матрицу многовходовых элементов И 12 (фиг, 2), где Еа и Я в сигналы, соответствукщие переносу из981992 6временно, сигналы, соответствующиеобратным кодам операндов, поступаютна входы дешифратора 2 контроля.Появление нескомпенсированной сшибки приводят или к появлению сигналов на 5 выходах сразу нескольких элементов Иматрицы. сложения, или к отсутствию .сигналов на их выходах. В первом случае будет отсутствовать сигнал (илиоба сигнала) на выходе (нли на обоих 10 выходах) дешифратора 2 контроля. Вобоих случаях иа выходах группы выходов 11 устройства сигналы будут отсутствовать. Если в кодовых словах операндов длиной М будет точно И феди ниц", сигнал с одного из выходов первой группы выходов матрицы 1 сложенияи сигналы с обоих выходов дешифратора, 2 контроля поступают на соответствующие управляющие выходной матрицы многовходовых элементов И 3 и блока 4коммутации. Одновременно, сигнал содного из выходов группы выходов пе"реноса матрицы. 1 сложения поступит нашину переноса в старший разряд 7 устройства, а по одной из шин переносаиз,младшего разряда 10 устройствасигнал, соотэетствукнций переносу нуля или единицы из младшего разряда,поступает на вход группы входов переЗ 0 носа выходной матрицы 3. После этого,срабатывает один или группа (не бо-,лее М) элементов И выходной матрицЫ3, с выходов которых сигналы поступают на шину суммы 11 устройства.Вблоке 4 коьюкутации, в то же время,или срабатывает соответствующее число элементов И и сигналы с их выходовпоступают на шину суввы 11 устройства, или(в зависимости от принятого1алфавита) це срабатывает ни один эле мент. Рассмотрим пример построения ифункционирования устройства для кода ф 2 из 4 ф при р = б.Принимаем алфавит.0 - 0011, 3 - 0110 р019134 - 1010 у2 - 1001 у 5 - 1100,где нулевая позиция - крайняя справа.Выходная матрица многовходовыхэлементов И 12, в этом случае, содержит 16 элементов И 13-28 (фиг. 3), аблок коюутации - 4 элемента И. Выходы элементов последнего блока, накоторые подаются сигналы С 0 ССуди С 4 к,соединены с 0-ой О-оий,1-ой и 3-ей (по порядку позиций кодового слова результата) шинами выходной группы шин устройства соответственно.При сложении, например, чисел .1и 3, с учетом переноса 0 из младшегоразряда на соответствующих входах .вы-.ходной матрицы появятся сигналы45 50 55 60 65 младшего разряда нуля н единицы соответственно; Ои Ц - сигвалыконтроля; С 0 С;, и Ср., - сигналы, соответствующие полусуммам,равным 0; 1 (1 с 1 с р) и рсоответственно, где р - основание системысчисления. Матрица содержит только темноговходовые элементы И, которыесоответствуют (И - 3 -. 1)-м позициямкодового слова результата, где 8 в .номера позиций этого слова, зависящиеот переноса из младшего разряда(О с Я с И). Если принять алфавит,в котором кодовые слова, соответствующие любым двум соседним (э алфавите) цифрам, отличаются друг от друга только одной позицией (по уровнямнапряжений в них), то выходная матрица имеет минимальные размеры 2 й р,каждый вход такой матрицы соединентолько с .одной координатной шиной ее. 20Если принят алфавит, в котором различия между кодовыми словами, соответствующими соседним цифрам максимальны,то выходная матрица имеет также максимальные размеры: 3 ю р. Каждый элемент И соединен с одним из входов(в соответствии с выбранным кодированием) первой группы входов,со вторым,третьим входами и одним из входовгруппы входов переноса блока. Выходыэлементов блока, соответствующих одинаковым позициям кодового слова результата, соединены выходными диаго" нальными шйнами с информационнымивыходами блока.Блок 2 представляет собой схемуконтроля для кода фМ из М" (полный дешифратор или пороговая схема),на входы которой подаются кодовые слова, противоположные операндам.Блок 4 представляет собой группу ф трехвходовых элементов И. Первый вход каждого такого элемента соединен с соответствующим входом группы информационных вхбдов, а второй и третий входы - с первым и втором уп равляющими входами блока. Выходы элементов И подключены к информационным выходам блока. Блок содержит только те элементы, которые соответствуют независящИм от перекоса позициям кодового слова результата. Если принят алфавит, в котором кодовое слова, соответствующие любым двум соседним цифрам, отличаются друг от друга только одной позицией, то блок содержит р элементов И. Если принят алфавит, в котором различия между кодовыми словами, соответствующими соседним цифрам максимальны, то блок содержит р/2 элементов 1.Предлагаемое устройство работает следунвим образом.Операнды в коде "М из М" поступают на группы входов первого и второго слагаемых матрицы 1 сложения.Одио

СмотретьЗаявка

3251777, 25.02.1981

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ГУМЕНЮК ВИТАЛИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/49

Опубликовано: 15.12.1982

Код ссылки

<a href="https://patents.su/6-981992-summator-v-kode-m-iz-n.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор в коде “м из n</a>

Предыдущий патент: Устройство для умножения по модулю

Следующий патент: Сумматор кодов фибоначчи

Случайный патент: Способ оценки интенсивности изнашивания при кавитационном воздействии