Устройство для вычисления функции х= а + в

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

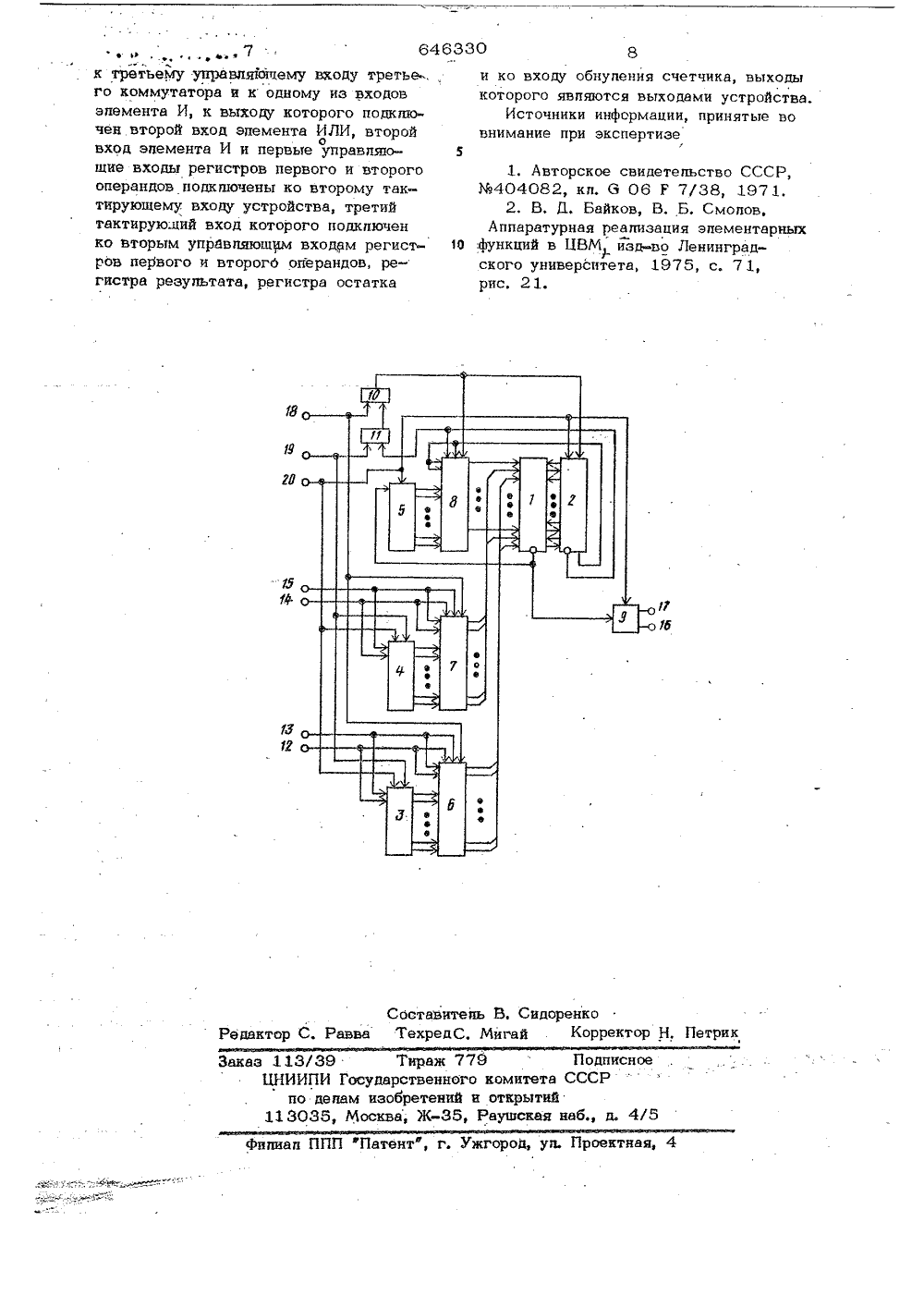

(72) Авторы изобретения Киевский ордена Ленина попитехнический институтим, 50-петин Великой Октябрьской социапистической ревопюцин(54) УСТРОЙСТВО ДЛЯ ВЬ 1 Ч 11 СЛ 1.11 ИЯ фУ 11 К 1111 И Х = ъА+В Изобретение относится к обпасти Ьычиспитепьной техники и может быть п 1.именено в цифровых вычиспитепьных машинах, специапизированных вычислительных устройствах и вычислительных средах, построенных на больших интегральных схемах. Известны уст ойства дпя вычисле.-.йия функции Х-" А+ , которые позвощпот выпопнять вычисления в том случае, когда все цифры операндов, имеются перед началом вычислений первой цифры резупьтата ( 11.Недостатком известного устройства явпяется невысокое быстродействие при работе в реальном масштабе времени.Наиболее бпизким техническим решением к предпоженному явпяется устройство, содержашее регистры первого и второго операндов, регистр ПЗУ, первый,второй и третий сумматоры 2).Недостатком известного устройства является низкое быстродействие. Цепью изобретения является повышение быстродействия,Эта цепь достигается тем, что вустройство введены регистр резупьтата,счетчик, элементы 11, ИЛИ, первый5 второй и третий коммутаторы, вторая,третья и четвертая группы. входов блокасуммирования соединены соответственнос выходами первого, второго и третьего коммутаторов, ко входам которых1 О подкпючены соответственно выходы регистров первого и второго операндови регистра результате, первый управпяюший вход которого и вход счетчика подкпючены к инверсному выходубпока суммирования, входы двух миадших разрядов регистров первого и вто.рого операндов, входы двух мпадшихразрядов, первый и второй управляющие входы первого и второго коммутаторов подкпючены к первому и второмувходам соответственно первого и второго операндов, первый тактирующий входсдвига регистров 2 и 5 и на цепь обнуления счетчика 9. В результате этогок содержимому регистров 3 и 4 прибавляются соответственно цифры ц, иЬ 1 содержимое регистра 2 сдвигаетсяна два разряда влево, содержимое регистра 5 сдвигается на один разрядвлево, а счетчик 9 устанавливается внулевое состояние. При сдвиге отрицательных чисел в регистре 2 на дваразряда влево в два младших разрядаэтого регистра записг 4 ваются единицы.На этом заканчивается один цикп вычислений, Дпя получения п разрядоврезультата необходимо выполнить Ициклов вычиспений. Уст ойство дпя вычисления функции Уй Л+ Вх, содержащее блок суммирования, первая группа входов которс- го подключена к выходам регистра остатка, а выходы - -ко входам регистра остатка, регистры первого и второго операндов, о т и и ч а ю ш е е с я тем, что, с целью повышения быстродействия, в него введены регистр резупьтата, счетчик, элементы И, ИЛИ,первый, второй и третий коммутаторы,вторая, третья и четвертая группы входов блока суммирования соединены соответственно с выходами первого, второгои третьего кбммутаторов, ко входамкоторьгх подкпючены соответственно вы-ходы регистров первогои второго операндов и регистра резудьтата; первыйуправляющий вход которого и входсчетчика подкпючены к инверсному выходу блока суммирования, входы двухмладших разрядов регистров первого ивторого операндов, входы двух младших разрядов, первый и второй управпяюшие входы первого и второго коммутаторов подкпючеиы к первому и второму входам регистров соответственно первого и второго операндов, первый тактируюший вход устройства соединен стретьими управпяюшими входами первого и второго коммутаторов и через эпемент ИЛИ - с первыми управпяюшимивходами третьего коммутатора и регистра остатка, прямой и инверсный выходы старшего разряда которого подключены ко второму управпяюшему входу и входам двух младших разрядов третьего коммутатора .и, соответственно,5 646330авертой группы блока суммирования 1,не связанные с выходами коммут.тора 8,передается код старшего разряда этогокоммутатора. Если существует сигнална входе 33/15/, то через коммутатор 56/7/ на вторую(третью) группу входовблока суммирования 1 передается прямой код. Еспи существует сигнал навходе 12/14/, то через коммутатор6/7/ на вторую (третью) группу вхо-. 0дов блока суммирования 1 передаетсяудвоенный прямой код, Если сигнал навходах 12, 13 и 14,15 отсутствует,то коммутаторы 6 и 7 кодов не передают. На входы второй и третьей группыблока суммирования .1,не связанные.с выходами коммутаторов 6 и 7, подаются, нулевые сигналы, Одновременнос этим, если прп выполнении суммирования в бпоке суммирования 1 результат положительный (сушествует сигнална инверсном выходе старшего разрядаблока суммирования 1), то к содержимому регистра 5 и счетчика 9 прибавляется 1. Если результат отрицатель- .25ный (соответствующий сигнал отсутствует) то регистр 5 и счетчик 9 неизменяет своего состояния, Во второмтакте цикла вычислений сигналсвхода 19 поступает на цепи певого30сдвига регистров .3 и 4 и на вход элемента И 1 1. В результате этого происходи, сдвиг на один разряд влевосодержимого регистров 3 и 4. Одновременно с этим, если существует сигнапна втором входе элемента И 11,т, е, если код в регистре 2 положительный, то сигнал с выхода элемента И 11поступает на вход элемента ИЛИ 10,40с выхода которого сигнал поступает нацепи выдачи кода регистра 2 и коммутатора 8. В резупьтате этого в блокесуммирования 1 происходит спожениекодов, подученных на выходах регистра452 и коммутатора 8, и изменение состояния регистра Б и счетчика 9 аналогично предыдущему такту. Если же сигнална втором входе элемента И 11 отсутствует (код в регистре 2 отрицательный), то суммирования в блоке суммирования 1 не происходит в регистр 5и счетчик 9 не изменяет своего состояния. После выполнения двух тактов 1 гоцикла в счетчике 9 находится пифраХ очередного разряда результата, Втретьем такте цикла вычислений поступает сигналс входа 20 на цепиприема кода регистров 3 и 4, на пепи форму па изобретенияаказ 113/39 Тираж 77 ЦНИИПИ Государственного по депам изобретений и 113035, Москва, Ж, Подписноекомитета СССРоткрытийаушская наб., д. 4/5 и ППП фПатентф, г. Ужгород, уп. Проектная, 1, , 4 В64633 к третьему управпякйчему входу третье-. го коммутатора и к одному из входов эпемента И, к выходу которого подкшочен второй вход эпемента ИЛИ, второйовход эпемента И и первые управпяо щие входы регистров первого и второго операндов подкпючены ко второму тактирующему входу устройства, третий тактирующий вход которого подключен ко вторым управпяюшум входам регист ров первого и второго операндов, регистра результата, регистра остатка и ко входу обнуления счетчика, выходыкоторого явпяются выходами устройства.Источники информации, принятые вовнимание при экспертизеI 1. Авторское свидетепьство СССР, %404082, кл. б 06 Р 7/38, 1971.2. В, Д. Байков, В. Б, Смолов, Аппаратурная реапизация элементарных функций в ЦВМйзд-во Ленинградского университета, 1975, с. 71, рис. 21.

СмотретьЗаявка

2393765, 03.08.1976

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50 ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ЖАБИН ВАЛЕРИЙ ИВАНОВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, СИДОРЕНКО ВИКТОР АНДРЕЕВИЧ, ТАРАСЕНКО ВЛАДИМИР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: вычисления, функции

Опубликовано: 05.02.1979

Код ссылки

<a href="https://patents.su/4-646330-ustrojjstvo-dlya-vychisleniya-funkcii-kh-a-v.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции х= а + в</a>

Предыдущий патент: Устройство для сравнения двоичных чисел

Следующий патент: Устройство для деления двоичных чисел

Случайный патент: Способ весового порционного дозиро-вания кусковых материалов