Устройство для обработки чисел в избыточном последовательном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1330629

Авторы: Золотовский, Коробков

Текст

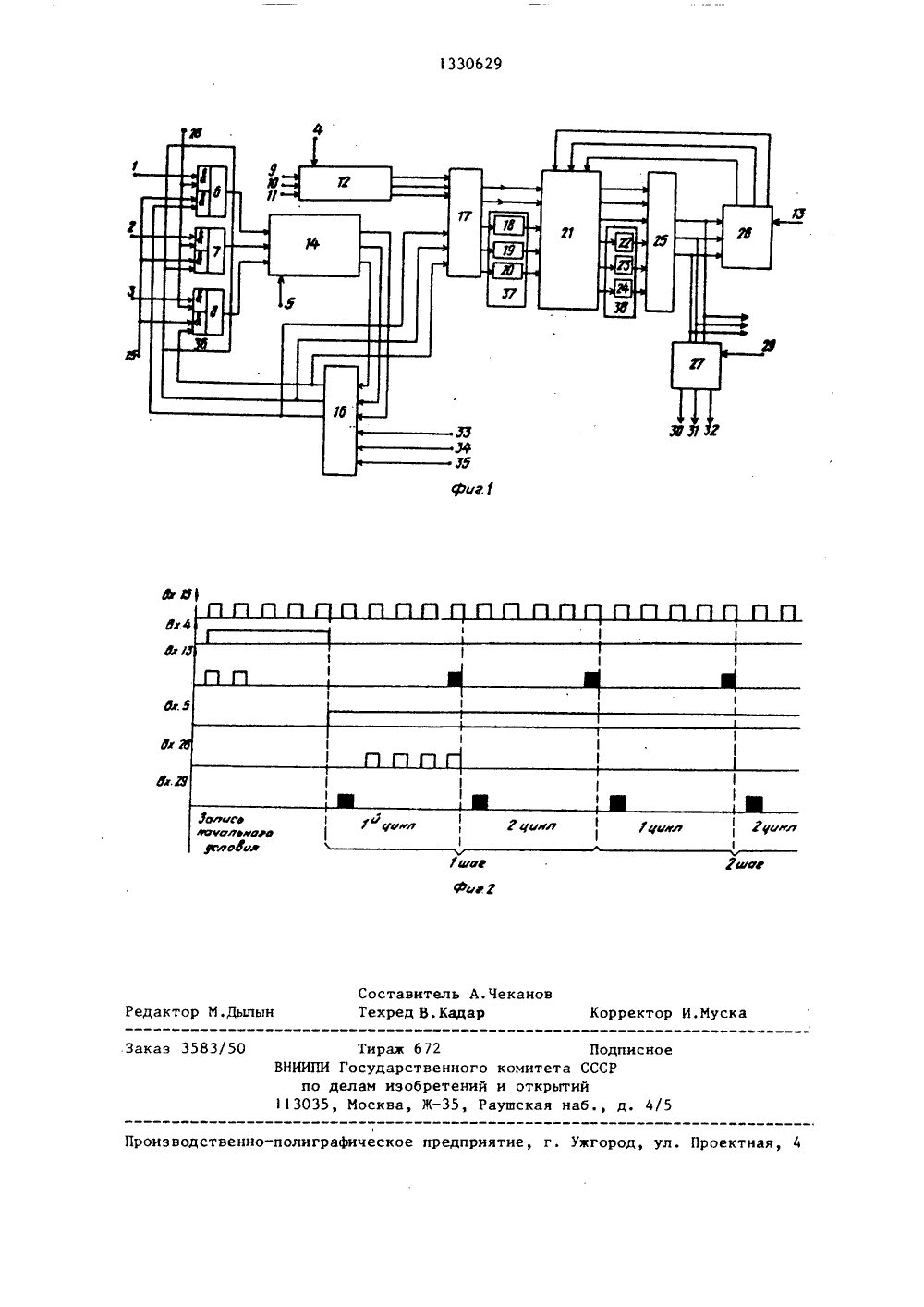

/64, 11.09,84. с СУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЧИСЕЛВ ИЗБЫТОЧНОМ ПОСЛЕДОВАТЕЛЬНОМ КОДЕ(57) Изобретение относится к областивычислительной техники и может бытьиспользовано при решении задач моделирования. Цель изобретения - расшинение функциональных возможностей.Устройство содержит регистр приращений аргумента, регистр подынтегральной функции, регистр остатка интеграла, регистр результата, два блоказадержки, блок памяти таблицы умножения, блок памяти таблицы сложения,сумматор подынтегральной функции икоммутатор. Устройство позволяет реа.лизовать наряду с умножением операции интегрирования. 2 ил.-ь 1квантованное приращение;45 текущий остаток;указатель выделения разрядов с К по 3 (знак минус указывает, что эти разряды находятся после запятой). По сигналу на входе 4 начальное значение Г поступает на вход регист-, ра 14 и по серии, поступающей на вход 5, записывается в регистр 14. Одновременно приращение рУ, записывается в регистр 12 по серии сигналов, поступающих на вход 4. На фиг.2 призовано для моделирования решения сис- тем дифференциальных уравнений.Цель изобретения - расширение функциональных воэможностей за счет реализации операции интегрирования.На фиг.1 приведена структурная схема устройства; на фиг,2 - его вре- и менная диаграмма.Устройство (фиг. ) содержит входы 1, 2 и 3 начальных условий, первый и второй входы 4 и 5 синхронизации устройства, элементы И-ИЛИ 6, 7 и 8, 6 входы 9, 10 и 11 приращений аргумента, регистр 12 приращений аргумента, третий вход 13 синхронизации устройства, регистр 14 подынтегральной функции, четвертый вход 15 синхрони зации устройства, сумматор 16 подынтегральной функции, блок 17 памяти таблицы умножения, элементы 18, 19 и 20 задержки первого блока задержки, блок 21 памяти таблицы сложения, эле менты 22, 23 и 24 задержки второго блока задержки, сумматор 25 приращений интеграла, регистр 26 остатка интеграла, регистр 27 результата, пятый вход 28 синхронизации устройства, 30 шестой вход 29 синхронизации устройства, выходы 30, 31 и 32 устройства, входы 33, 34 и 35 приращения подынтегральной функции, коммутатор 36, первый и второй блоки 37 и 38 задержки.Схема работает в соответствии с алгоритмом ведена временная диаграмма работы устройства для случая двухразрядных приращений и лятираэрядных чисел. За два такта происходит запись приращения и эа пять тактов - запись начального значения. Затем сигнал на входе 4 становится равным нулю, а на входе 5 - единице.Вся диаграмма разбита на шаги. Выполнение шага соответствует определению приращения. Каждый шаг разбит на циклы. Один цикл - это выполнение операции умножения на один разряд приращения р 1;, , Число циклов равно числу разрядов приращения рК (в нашем случае два).Следовательно, после записи начальных условий начинается работа. Старший разряд приращения, представленного в четвертичном избыточном коде, поступает на вход блока 17. Кодировка цифр разряда следующая: 0=0.00, 1=0.01, 2=0.О, 3=0.11, -1=1.01, -2=1.10.На второй вход поступает старший разряд подынтегральной функции Г. с выхода сумматора 16, где происходит сложение старших разрядов функции Г;, и приращения рГ,.1В блоке 17 записана таблица перемножения цифр в избыточной четверичной системе счисления. Полученное произведение имеет два разряда. Старший рязряд поступает непосредственно на блок 21, а второй разряд через элементы задержки 18, 19 и 20. В блок 21 записана таблица слоения трех цифр. Третья цифра есть цифра остатка, поступающего иэ регистра 26. Ре" зультат сложения трех цифр есть двухраэрядная сумма, старший разряд которого поступает на сумматор 25 непосредственно, а мпадший разряд через элементы задержки 22, 23 и 24. В сумматоре 25 происходит сложение старшего текущего разряда и младшего предыдущего ряэряда. Полученный самый старший разряд является разрядом приращения и записывается в регистр 27 по сигналу с входа 29, Остальные младшие разряды есть разрыды остатка, они записываются в регистр 26 по сигналам с входа 13. После того, как происходит умножение и разрядов функции Г на разряд приращения чУ, цикл заканчивается.Подачей сигнала на вход 4 содержимое регистра 12 сдвигается на разряди выполняется следующий цикл аналогично указанному. Формула изобретения Устройство для обработки чисел в избыточном последовательном коде, содержащее регистр приращений аргумента, регистр подынтегральной функции, два блока задержки, блок памяти, таблицы умножения, блок памяти таблицы сложения, регистр остатка интеграла, сумматор подынтегральной функции, причем входы приращения аргумента устройства соединены с информационными входами регистра приращений аргумента, выходы которого соединены с первой группой адресных входов блока памяти таблицы умножения, выходы старших разрядов которого соединены с первой группой адресных входов блока памяти таблицы сложения, входы приращения подынтегральной функции устройства соединены с входами первого слагаемого сумматора подынтегральной функции, выходы которого соединены с второй группой адресных входов блока памяти таблицы умножения, выходы младших разрядов которого через первый блок задержки соединены с второй группой адресных входов блока памяти таблицы сложения, выходы младших разрядов которого соединены с входами второго блока задержки, третья группа адресных входов блока памяти таблицы сложения соеДинена с выходами регистра остатка интеграла, выходы регистра подынтегральной функ 5 10 15 20 25 30 35 ции подключены к входам второго сла"гаемого сумматора подынтегральной функции, первый, второй и третий входы синхронизации устройства подключены к входам синхронизации регистра приращений аргумента, регистра подынтегральной функции и регистра остатка интеграла соответственно, о т л ич а ю щ е е с я тем, что, с цельюрасширения функциональных воэможностей эа счет реализации операции интегрирования, оно содержит коммутатор, регистр результата и сумматорприращений интеграла, причем входыначальных условий устройства соединены с первой группой информационныхвходов коммутатора, выходы которогосоединены с информационными входамирегистра подынтегральной функции, выходы сумматора подынтегральной функции соединены с второй группой информационных входов коммутатора, выходыстарших разрядов блока памяти таблицы сложения соединены с входами первого слагаемого сумматора приращенийинтеграла, выходы которого соединеныс входами регистра остатка интегралаи регистра результата, выходы которого соединены с выходами устройства,выходы второго блока задержки соединены с входами второго слагаемогосумматора приращений интеграла, четвертый вход синхронизации устройстваподключен к входу синхронизации регистра результата, четвертый и пятьгйвходы синхронизации устройства соединены соответственно с первым и вторым управляющими входами коммутатора..Чекано ставител хред В,К орректор И.Муск М.Дылы еда аказ 3583/50 Тирам 672 осударственно елам иэобретени Москва, %-35, нсное омитета ССС открытий

СмотретьЗаявка

3882496, 10.04.1985

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ

МПК / Метки

Метки: избыточном, коде, последовательном, чисел

Опубликовано: 15.08.1987

Код ссылки

<a href="https://patents.su/4-1330629-ustrojjstvo-dlya-obrabotki-chisel-v-izbytochnom-posledovatelnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обработки чисел в избыточном последовательном коде</a>

Предыдущий патент: Синусно-косинусный преобразователь

Следующий патент: Устройство для сравнения двух частот

Случайный патент: Шихта для изготовления пористых керамических форм