Устройство для вычисления функций двух аргументов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1191917

Автор: Флоренсов

Текст

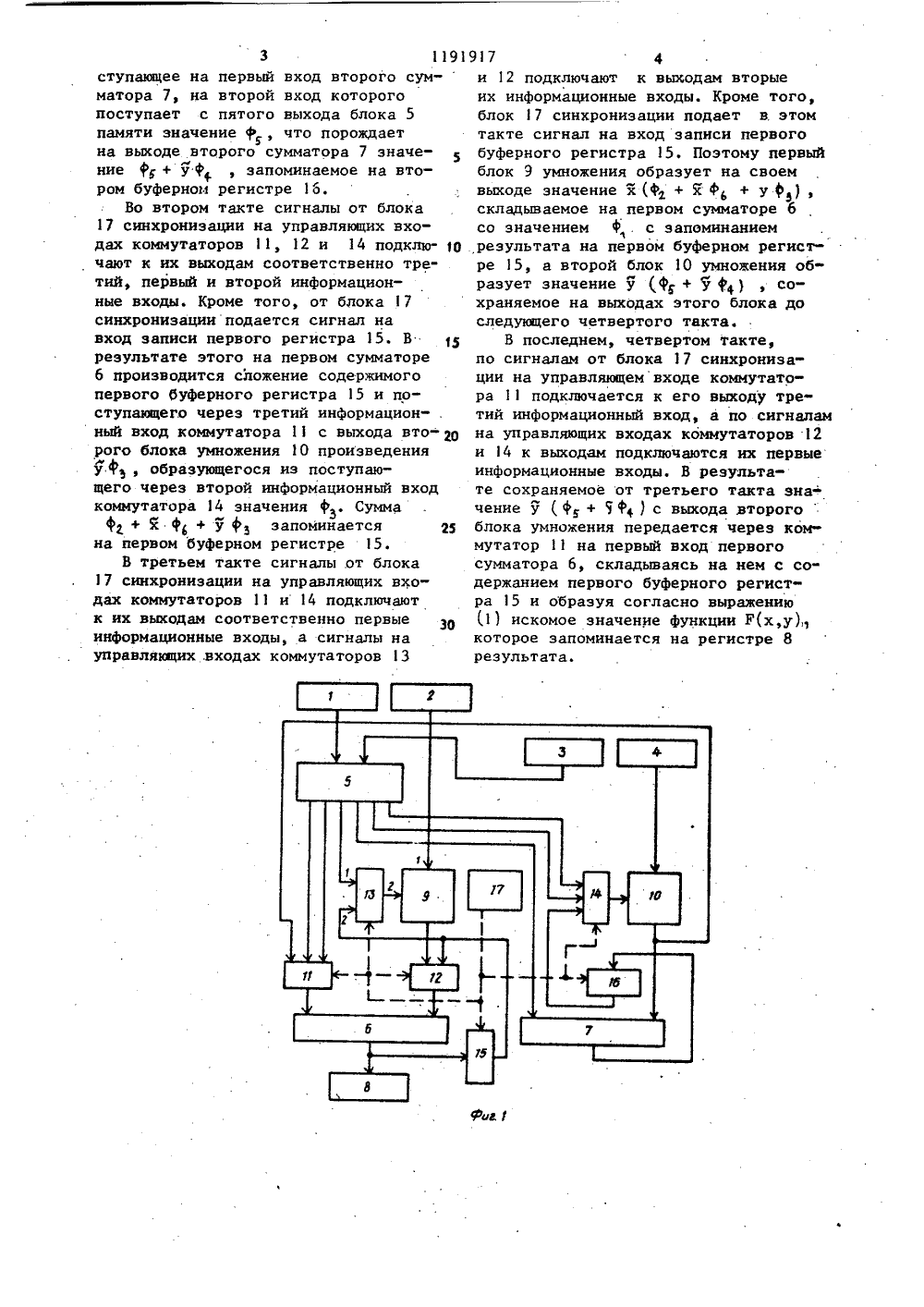

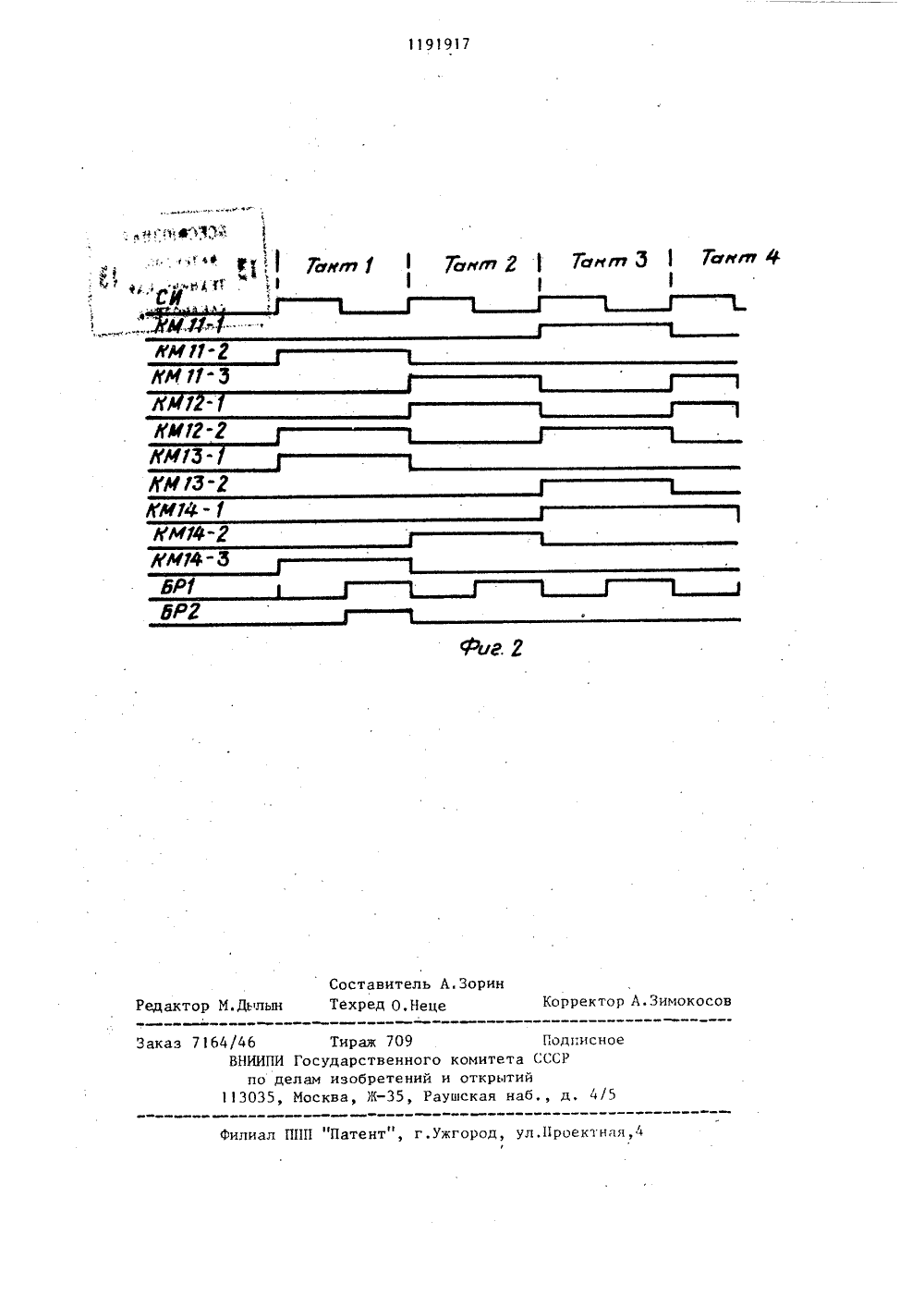

(54)(57),УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ ДВУХ АРГУМЕНТОВ, содержащее регистр старших разрядов первого аргумента, регистр младших разрядов первого аргумента, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента, блок памяти, два блока умножения, блок синхронизации, пер сумматор, регистр результата, два коммутатора и первый буферный регистр, причем выходы регистра старших разрядов первого аргумента и регистра старших разрядов второго аргумента соедйнены с входами соответственно первой и второй групп разрядов адреса блока памяти, выходы полей первой и второй составляющих которого соединены соответственно с первым и вторым информационными входами первого коммутатора,выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом второго коммутатора, первый информационный вход которого соединен с выходом первого буферного регистра, вход разрешения записи которого соединен с первым выходом выи ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ОПИСАНИЕ ИЗ,801191917 А блока синхронизации, второй и тре-ьтий выходы которого соединены соответственно с управляющими входамипервого и второго коммутаторов, выхопервого сумматора соединен с информационными входами первого буферного регистра и регистра результатвыходы регистра младших разрядов первого аргумента и регистра младшихразрядов второго аргумента соединены с первыми входами соответственнопервого и второго блоков умножения,о т л и ч а ю щ е е с я тем, что,с целью повышения точности, в неговведены второй сумматор, второй бу-ферный регистр, третий и четвертыйкоммутаторы, причем выход второгосумматора соединен с информационнымвходом второго буферного регистра,вход разрешения записи и выход которого соединены соответственно счетвертым выходом блока синхронизации и первым информационным входомтретьего коммутатора, второй и тре-тий информационные входы которогосоединены с выходами полей соответственно третьей и четвертой составляющих блока памяти, выходы полейпятой и шестой составляющих которогосоединены соответственно с первымвходом второго сумматора и первым информационным входом четвертого коммутатора, второй информационный входкоторого соединен с выходом первогобуферного регистра, выходы третьегои четвертого коммутаторов соединены свторыми входами соответственно второгои первого блоков умножения, выход первого блока умножения соединен с вторым информационным входом второго1 коммутатора, выход второго блока умножения соединен с вторым входом второго сумматора и третьим информационным входом первого коммутатора,191917управляющие входы третьего и четвер.того коммутаторов соединены соответственно с пятым и шестым выходами .блока синхронизации.,тов х и у, а х и у " младшими разРядами. аргументов х,и у,В предположении О -х, у.( 1 по-45 грешность аппроксимации (.1 ) определя 1Изобретение относится к вычислительной технике и может быть использовано для ускоренного вычисления произвольной функции двух аргументов, в частности для вычисления Функции: 5хагсСд , необходимой при выполненииупреобразования декартовых координат в полярные координаты.Цель изобретения - повышение точ . ностиНа фиг.1 изображена блок-схема предлагаемого устройства;,на фиг,2- временные диаграммы работы блока синхронизации, 15Устройство содержит регистр 1 старших разрядов первого аргумента, регистр 2 младших разрядов первого . аргумента, регистр 3 старших разрядов второго аргумента, регистр 4 20 Млад 1 пих разрядов второго аргумента, блок 5 памяти, первый сумматор 6, вто. рой сумматор 7, регистр 8 результата первый блок 9 умножения, второй блок . 10 умножения, коммутаторы 11 - 14, 25 буферные регистры 5 и 16, блок 17синхронизации.Вычисление значения функции Р(х,у) и устройстве производится на основе соотноиения 2ется соответствующим остаточным членом ряда Тейлора функции и имеет поэтому порядок М 2 З", М выражается через частные производные третьего порядка функции Р(х,у). Поэтому надлежащим выбором параметра К можно сделать погрешность аппроксимации (1),выходящей за пределы используемой Разрядной сетки.Устройство работает в четыре такта, определяемые блоком 17 синхронизации. Блок 5 памяти хранит таблицы значений коэффициентов Ф - ф, снимаемых соответственно с выходов 1 - 6-го этого блока и зависящих от поступающих на вход блока 5 памяти значений х и у старших разрядов ар" гументов х и у.В первом такте сигналы от блока 7 синхронизации на управляющих входах коммутаторов 11 - 14 подключают к их выходам соответственно второй, второй первый и третий информационные входы. Кроме того, блок 17 синхронизации выдает сигналы на входы записи первого и второго буферных регистров 15 и 16. Поэтому на второй вход первого блока 9 умножения поступает с шестого выхода блока 5 памяти значение Ф, которое, умножаясь на значение х, через второй информационный вход коммутатора 12 поступает на второй вход первого сумматора 6, на первый вход которого через второй информационный вход коммутатора 11 подается значение , что приводит к образованию на информационном входе первого буферного регистра 15 значения ф+ + х ф, запоминаемого на нем. Одновременно в этом же такте через третий информационный вход коммутатора 14 на второй вход второго блока О умножения поступает значение ф 1, умно- . жающееся на значение у с первого входа второго блока 1 О умножения и по3 1191 ступающее на первый вход второго сум-матора 7, на второй вход которого поступает с пятого выхода блока 5 памяти значение ф , что порождаетЭна выходе второго сумматора 7 значение ф + у ф , запоминаемое на втором буферном регистре 16.Во втором такте сигналы от блока 17 синхронизации на управляющих входах коммутаторов 11, 12 и 14 подклю чают к их выходам соответственно третий, первый и второй информационные входы. Кроме того, от блока 17 синхронизации подается сигнал на вход записи первого регистра 15В результате этого на первом сумматоре 6 производится сложение содержимого первого буферного регистра 15 и поступающего через третий информацион- . ный вход коммутатора 11 с выхода вто- о рого блока умножения 10 произведения у ф, образующегося иэ поступающего через второй информационный вход коммутатора 4 значения ф, Сумма ф + х ф + у ф запомийается д на первом буферном регистре 15.В третьем такте сигналы .от блока 17 синхронизации на управляющих входах коммутаторов 11 и 14 подключают к их выходам соответственно первые информационные входы, а сигналы на управляющих .входах коммутаторов 3 917 4и 12 подключают к выходам вторые их информационные входы. Кроме того, блок 7 синхронизации подает в. этом такте сигнал на вход записи первого буферного регистра 15. Поэтому первый блок 9 умножения образует на своем выходе значение х (Ф + с Ф + у Ф)складываемое на первом сумматоре 6 со значением Ф. с запоминанием результата на первом буферном регистре 15, а второй блок 10 умножения образует значение у (ф + у Ф) , сохраняемое на выходах этого блока до следующего четвертого такта.В последнем, четвертом такте, по сигналам от блока 17 синхронизации на управляющем входе коммутатора 11 подключается к его выходу третий информационный вход, а по сигналам на управляющих входах коммутаторов 12 и 14 к выходам подключаются их первые информационные входы. В результате сохраняемое от третьего такта зна- чение у ( Ф +ф ) с выхода второгоблока умножения передается через коммутатор 11 на первый вход первого сумматора 6, складываясь на нем с со" держанием первого буферного регистра 15 и образуя согласно выражению (1) искомое значение функции Р(х,у) которое запоминается на регистре 8 результата.1191917 ЮОюм 77 3 Ф 7 ЯфМ 78-ГМфМРЗЮВ/74-ЛАММ Я Составитель А.Зорин Техред О.Неце Корректор А.Зимокосов Редактор М.Двлын Заказ 7164/46 Тираж 709 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий13035, Москва, Ж, Раушская наб д. 4/5 Филиал ППП "Патент", г,ужгород, ул.Проектная,4Ф ФЮ 3фФ7 аюп 1л4.уд;" - Тонт яТонт 3 1 Тают1

СмотретьЗаявка

3638491, 02.09.1983

ОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ФЛОРЕНСОВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 17/10

Метки: аргументов, вычисления, двух, функций

Опубликовано: 15.11.1985

Код ссылки

<a href="https://patents.su/4-1191917-ustrojjstvo-dlya-vychisleniya-funkcijj-dvukh-argumentov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функций двух аргументов</a>

Предыдущий патент: Устройство для моделирования систем массового обслуживания

Следующий патент: Цифровой согласованный фильтр

Случайный патент: Устройство приоритетного доступа к общей памяти