Преобразователь двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

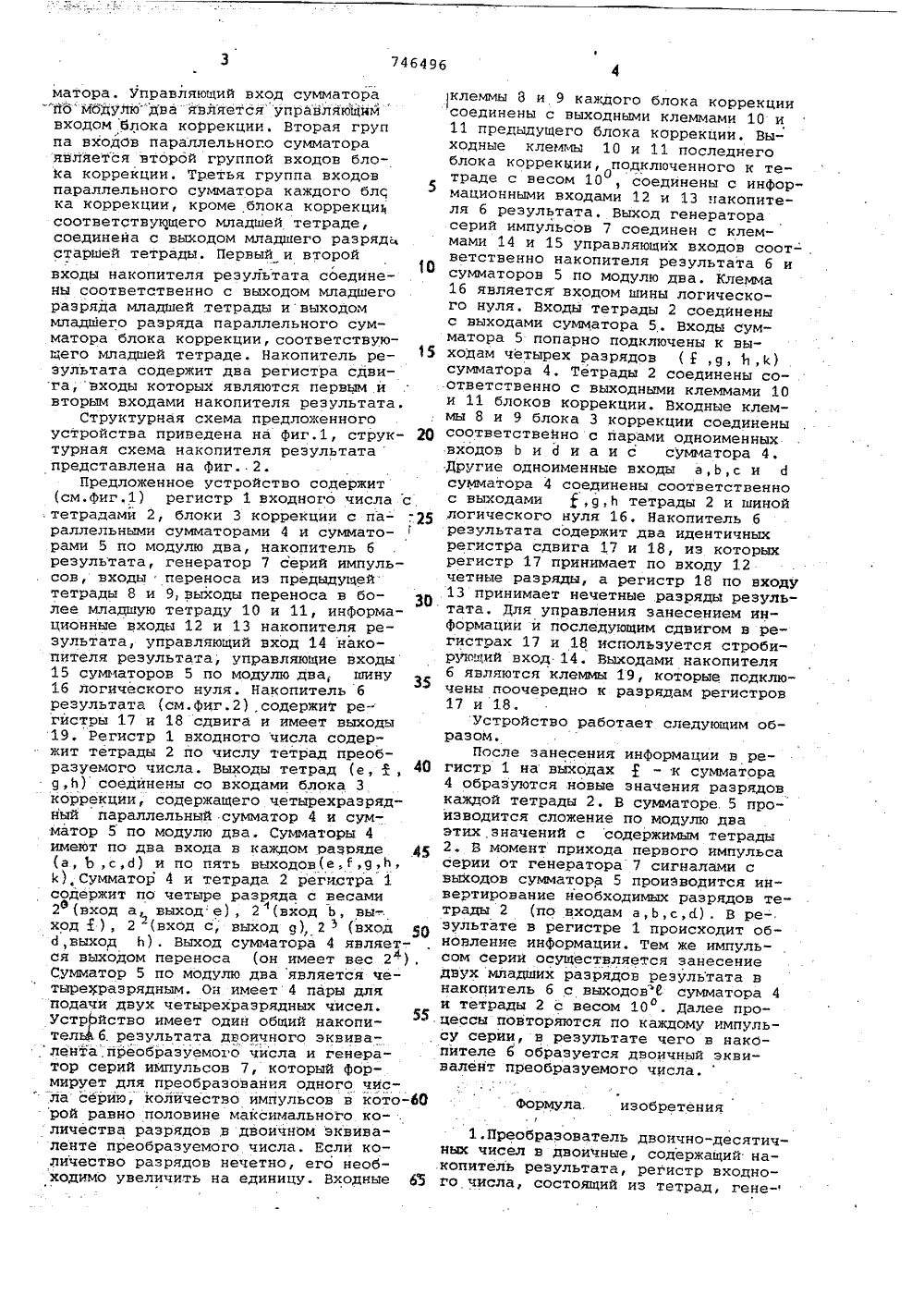

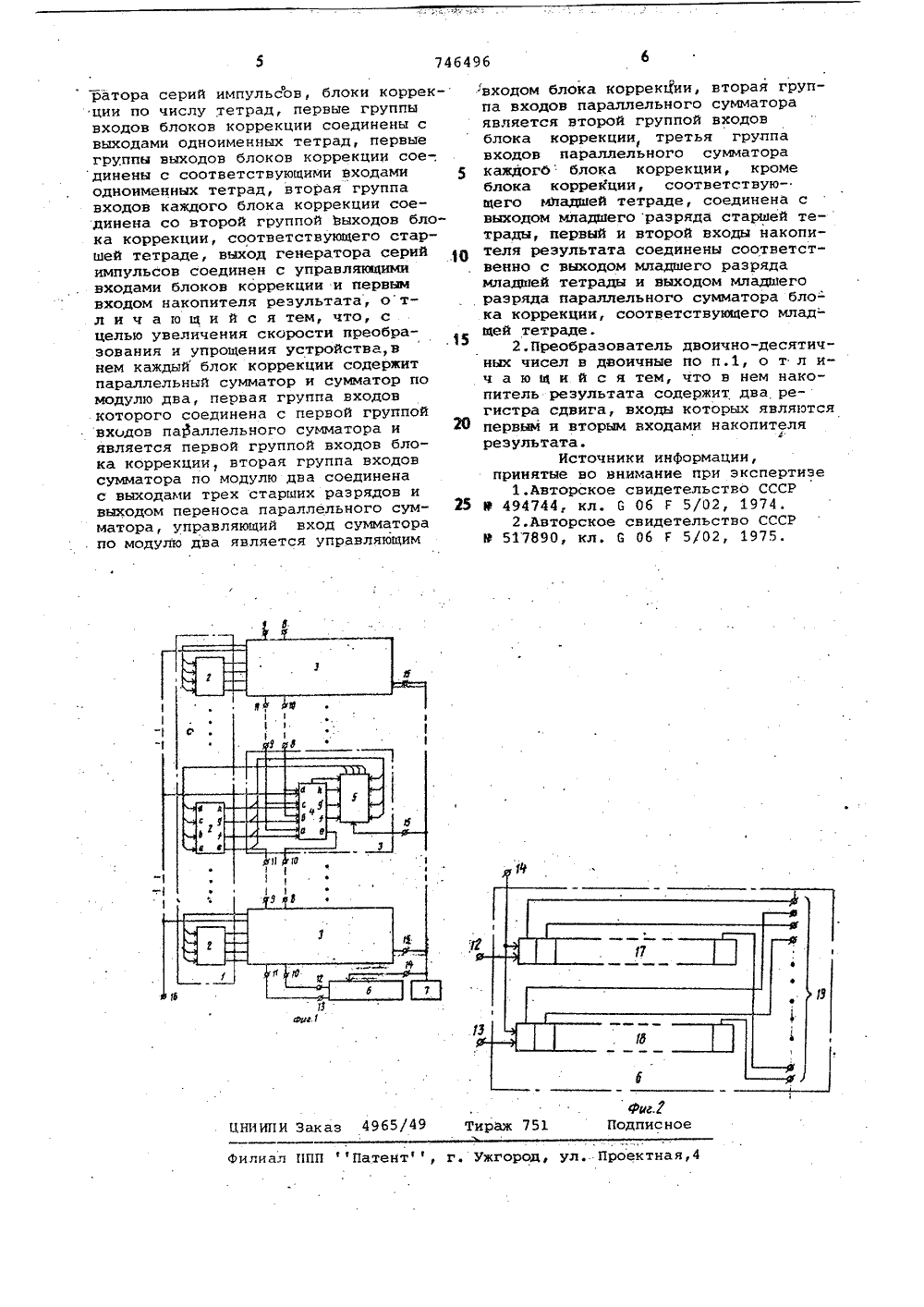

ввтонтко-те:; 1 ескаеОПИ А ЕИЗОБРЕТЕНИЯ Союз Советскик Социалистических республик(51) М. Кл. С Об Р 5/02 с присоединением заявки Нов 1 осударствеииый комитет СССР по делам изобретеиий и открытий( 54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ Изобретение относится к областй автоматики и цифровой вычислительной техники и может быть использовано при построении двоично-десятичных преобразователей в составе вычислительных машин и специальных устройств. Известен преобразователь двоичнодесятичных чисел в двоичные, содержащий регистр сдвига, разделенныйна тетрады, блоки коррекции, входыкоторых соединены с выходами тетрад,а выходы соединены со входами тетрад, регистр результата и блок управления (11,Однако это устройство имеет относительно низкое быстродействие.Наиболее близким по техничеСкойсущности и схемному решению к предложенному является преобразователь,содержащий накопитель результата,регистр входного числа, состоящийиз тетрад, генератор серий импульсов, блоки коррекции по числу тет-.рад. Первые группы входов блоков Кор"рекции соединены с выходами одноименных тетрад. Первые группы выходовблоков коррекции соединены.с соответствующими входами одноименных тетрад,Вторая группа входов каждого блОкакоррекции соединена со второй группой выходов блока коррекции, СОответствующего старшей тетраде. Выходгенератора серий импульсов соединенс управляющйми входами блоков коррекции и первым входом накопителярезультата. Кроме того известноеустройство содержит блок переноса,а регистр входного числа являетсятакже сумматором 21,Однако зто устройство также имеетотносительно низкое быстродействиеи сравнительно большой объем аппаратуры.. Цель изобретения - увеличениескорости преобразования и упрощениепреобразователя.Это достигается тем, что в устройстве каждый блок коррекции содер"жит параллельный сумматор и сумматорпо модулю два, первая группа входовкоторого соединена с первой группойвходов параллельного сумматора иявляется первой группой входов бло,ка коррекции. Вторая группа входовсумматора по модулю два соединена с:выходами трех старших разрядов и746496 матора. Управляющий вход сумматора помбдулю"два является управляющим входом блока коррекции. Вторая груп па входов параллельного сумматора является второй группой входов блоКа коррекции. Третья группа входов параллельного сумматора каждого блс ка коррекции, кроме блока коррекци соответствующего младшей тетраде, соединена с выходом младшего разряд старшей тетрады. Первый и второй10 входы накопителя результата соединены соответственно с выходом младшего разряда младшей тетрады и выходом младшего разряда параллельного сумматора блока коррекции, соответствующего младшей тетраде. Накопитель результата содержит два регистра сдвига, входы которых являются первым и вторым входами накопителя результата.Структурная схема предложенного устройства приведена на фиг.1, струк турная схема накопителя результата представлена на Фиг. 2.Предложенное устройство содержит (см.фиг,1) регистр 1 входного числа с тетрадамй 2, блоки 3 коррекции с па- .-5 раллельными сумматорами 4 и сумматорами 5 по модулю два, накопитель б результата, генератор 7 серий импульсов, входы переноса иэ предыдущей тетрады 8 и 9, выходы переноса в более младшую тетраду 10 и 11, информационные входы 12 и 13 накопителя результата, управляющий вход 14 накопителя результата, управляющие входы 15 сумматоров 5 по модулю два шину 16 логического нуля. Накопитель б результата (см.фиг.2),содержит регистры 17 и 18 сдвига и имеет выходы 19. Регистр 1 входного числа содержит тетрады 2 по числу тетрад преобразуемого числа. Выходы тетрад (е, %, 40 9,Ь) соединены со входами блока 3 коррекции, содержащего четырехразрядный параллельный сумматор 4 и сумматор 5 по модулю два. Сумматоры 4 имеют по два входа в каждом разряде (а, Ь,с,д) и по пять выходов(е,9,Ь М), Сумматор 4 и тетрада 2 регистра 1 содержит по четыре разряда с весами 2 ф(вход а, выходе), 2"(вход Ь, вы- ход), 2 (вход с, выход 9), 2(вход р д,выход Ь). Выход сумматора 4 является выходом переноса (он имеет вес 2 ) . Сумматор 5 по модулю два является четырехразрядным. Он имеет 4 пары для подачи двух четырехраэрядных чисел. Устррйство имеет один общий накопителй б. результата двоичного эквивалента преобразуемого числа и генератор серий импульсов 7, который Формирует для преобразования одного числа серию, количество импульсов в котоО рой равно половине максимального количества разрядов в двоичном эквиваленте преобразуемого числа, Если количество разрядов нечетно, его необходимо увеличить на единицу. Входные Я клеммы 8 и 9 каждого блока коррекции соединены с выходными клеммами 10 и 11 предыдущего блока коррекции. Выходные клеммы 10 и 11 последнего блока коррекции, подключенного к тетраде с весом 10 , соединены с инфор 0мационными входами 12 и 13 накопителя б результата, Выход генератора серий импульсов 7 соединен с клеммами 14 и 15 управляющих входов соот- . ветственно накопителя результата б и сумматоров 5 по модулю два. Клемма 16 является входом шины логического нуля. Входы тетрады 2 соединены с выходами сумматора 5. Входы сумматора 5 попарно подключены к выходам четырех разрядов ( 1,9, Ь,) сумматора 4. Тетрады 2 соединены соответственно с выходными клеммами 10 и 11 блоков коррекции. Входные клеммы 8 и 9 блока 3 коррекции соединены соответственно с парами одноименных входов Ь и д и а и с сумматора 4. Другие одноименные входы аЬ,с и д сумматора 4 соединены соответственно с выходами ,9,Ь тетрады 2 и шиной логического нуля 16, Накопитель б результата содержит два идентичных регистРа сдвига 17 и 18, из которых регистр 17 принимает по входу 12четные разряды, а регистр 18 по входу 13 принимает нечетные .разряды результата. Для управления занесением инФормации и последующим сдвигом в регистрах 17 и 18 используется стробирующий вход 14, Выходами накопителя6 являются клеммы 19, которые подключены поочередно к разрядам регистров 17 и 18.Устройство работает следующим образом.После занесения информации в регистр 1 на вьйодах- к сумматора 4 образуются новые значения разрядов каждой тетрады 2. В сумматоре 5 производится сложение по модулю два этих значений с содержимым тетрады 2. В момент прихода первого импульса серии от генератора 7 сигналами с выходов сумматора 5 производится инвертирование необходимых разрядов тетрады 2 (по входам а,Ь,с,й). В результате в регистре 1 происходит обновление информации. Тем же импульсом серии осуществляется занесение двух младших разрядов результата в накопитель б с выходовс сумматора 4 и тетрады 2 с весом 10 . Далее процессы повторяются по каждому импульсу серии, в результате чего в накопителе 6 образуется двоичный эквивалент преобразуемого числа.Формула. изобретения746496 фиг.РЦНИИПИ Заказ 4965/49 Тираж 751 Подписное иал ППП фПатент, г. Ужгород, ул Проектная,4 ратора серий импульсов, блоки коррекции по числу тетрад, первые группы входов блоков коррекции соединены с выходами одноименных тетрад, первые группы выходов блоков коррекции сое-, динены с соответствующими входами 5 одноименных тетрад, вторая группа входов каждого блока коррекции соединена со второй группой выходов блока коррекции, соответствующего старшей тетраде, выход генератора серий импульсов соединен с управляющими входами блоков коррекции и первым входом накопителя результата, отл и ч а ю щ и й с я тем, что, с целью увеличения скорости преобразования и упрощения устройства,в нем каждый блок коррекции содержит параллельный сумматор и сумматор по модулю два, первая группа входов которого соединена с первой группой входов параллельного сумматора и Ю является первой группой входов блока коррекции, вторая группа входов сумматора по модулю два соединена с выходами трех старших разрядов и выходом переноса параллельного сум матора, управляющий вход сумматора . по модулю два является управляющим входом блока коррекции, вторая группа входов параллельного сумматора является второй группой входов блока коррекции, третья группа входов параллельного сумматора каждогб блока коррекции, кроме блока коррекции, соответствующего младшей тетраде, соединена с выходом младшего разряда старшей тетрады, первый и второй входы накопителя результата соединены соответственно с выходом младшего разряда младшей тетрады и выходом младшего разряда параллельного сумматора бло- ка коррекции, соответствующего млад- шей тетраде.2.Преобразователь двоично-десятичных чисел в двоичные по п.1, о т л ич а ю щ и й с я тем, что в нем накопитель результата содержит два регистра сдвига, входы которых являются первым и вторым входами накопителя результата.Источники информации, принятые во внимание при экспертизе1.Авторское свидетельство СССР В 494744, кл. С 06 Г 5/02, 1974.2.Авторское свидетельство СССР В 517890, кл. С 06 Г 5/02, 1975.

СмотретьЗаявка

2188726, 10.11.1975

РИЖСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА БИРЮЗОВА С. С

ИВАНОВ ВИКТОР АНАТОЛЬЕВИЧ, ПОНОМАРЕВ ЮРИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичных, двоичные, чисел

Опубликовано: 05.07.1980

Код ссылки

<a href="https://patents.su/3-746496-preobrazovatel-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в двоичные</a>

Предыдущий патент: Устройство для управления пишущей машинкой

Следующий патент: Преобразователь двоично-десятичного кода 12222 в унитарный код

Случайный патент: Пакер