Параллельный сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

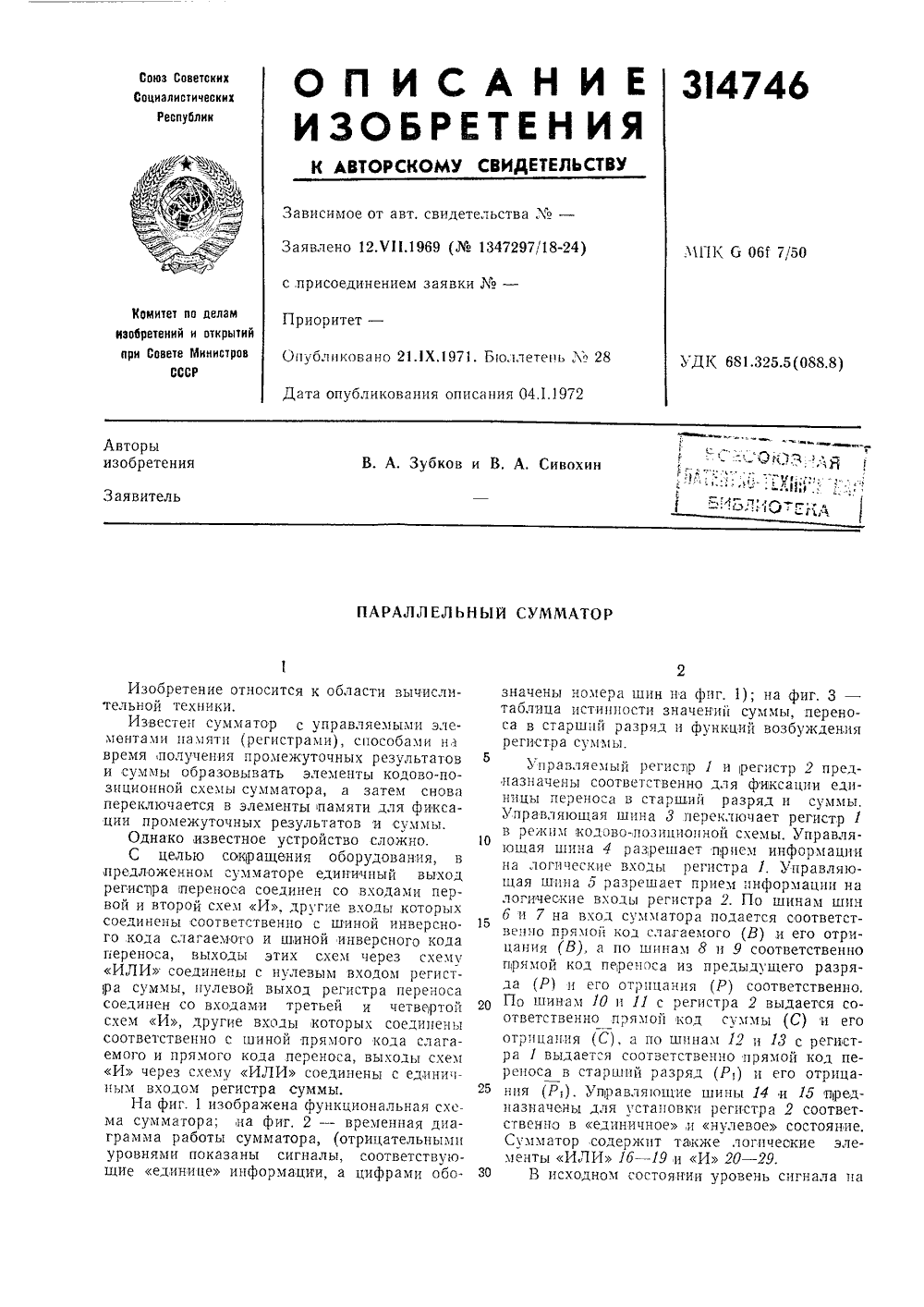

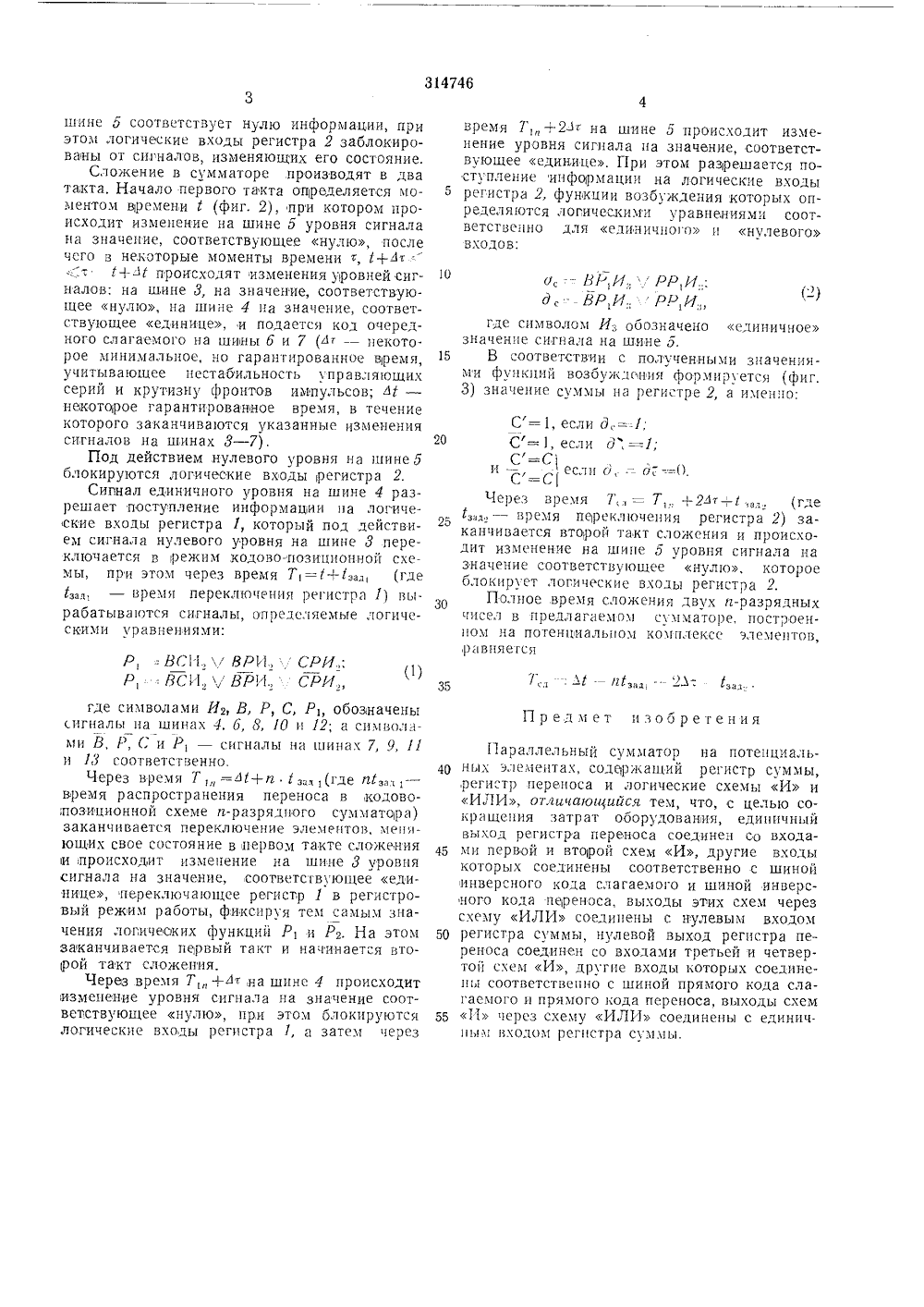

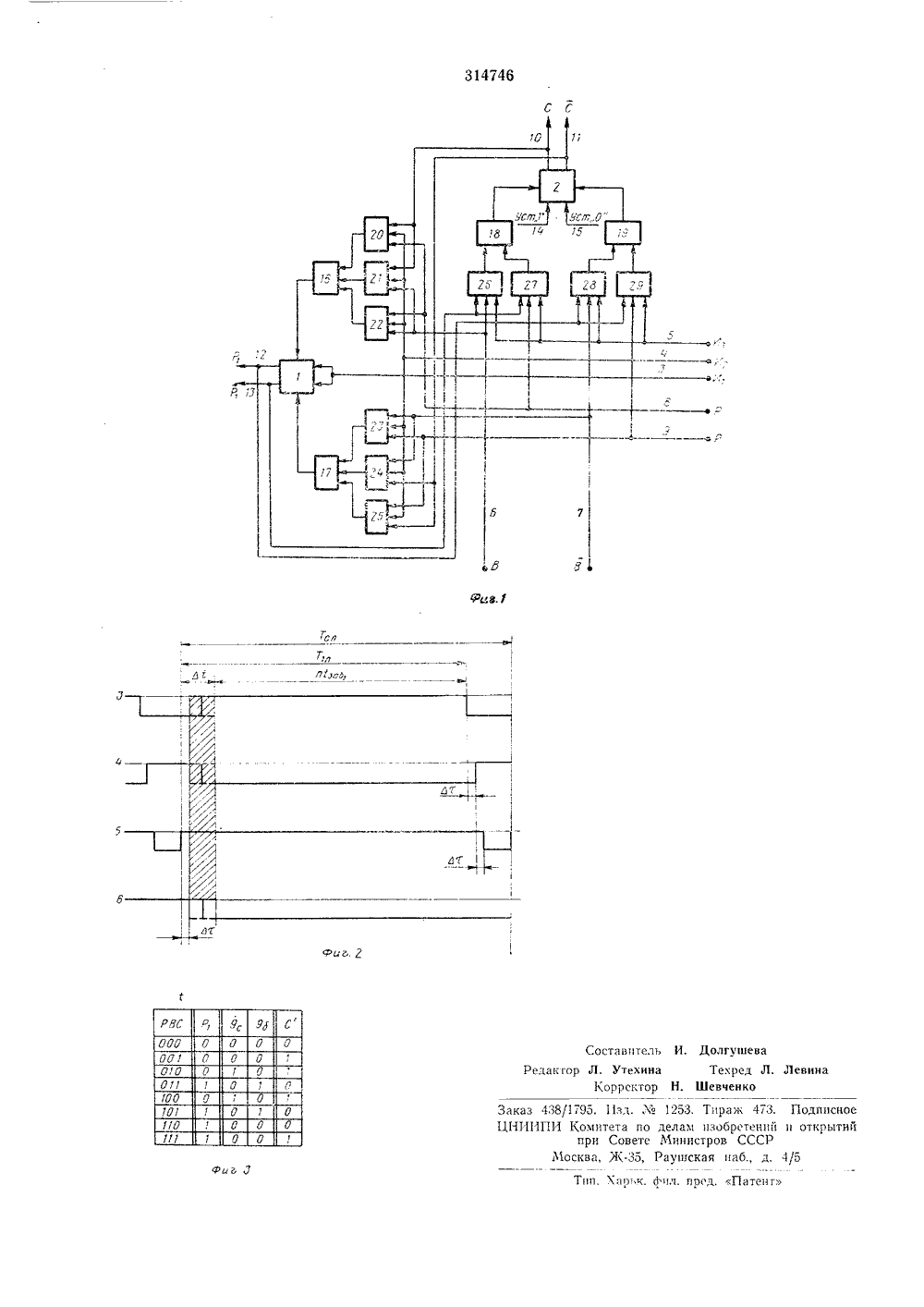

ОП ИСАНИЕ 34246ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических РеспубликКФЪ ависимое от авт. свидетельства-.1969 ( 1347297/18-2 1 ПК Ст 061 7/5 явлено вки о исоединением Комитет по деламзобретений и открытийпри Совете Министров итет Опубликовано 21.1 Х.1971. Бюллетень Хо 28Дата опубликования описания 04.1.1972 УДК 681,325.5 (088.8 Авторыизобретения:1 ф" Г,ла АРАЛЛ ЕЛ Ь Н Ы Й СУЛМАТ Изобретение относится к области вычислительной техники.Известен сумматор с управляемыми элементами памяти (регистрами), способами на время получения промежуточных результатов и суммы образовывать элементы кодово-позиционной схемы сумматора, а затем снова переключается в элементы памяти для фиксации промежуточных результатов и суммы.Однако известное устройство сложно.С целью сокращения оборудования, в предложенном сумматоре единичный выход регисцра переноса соединен со входами первой и второй схем И, другие входы которых соединены соответственно с шиной инверсного кода слагаемого и шиной инверсного кода гтереноса, выходы этих схем через схему ИЛИ соединены с нулевым входом регистра суммы, нулевой выход регистра переноса соединен со входами третьей и четвертой схем И, другие входы которых соединены соответственно с шиной прямого кода слагаемого и прямого кода переноса, выходы схем И через схему ИЛИ соединены с единичным входом регистра суммы.На фиг. 1 изображена функциональная схема сумматора; на фиг, 2 - временная диаграмма работы сумматора, (отрицательными уровнями показаны сигналы, соответствующие единице информации, а цифрами обозначены номера шин на фпг. 1); на фиг, 3 - таблица истинности значений суммы, переноса в старший разряд и функций возбуждения регистра суммы.5Управляемый регистр 1 и регистр 2 предназначены соответственно для фиксации единицы переноса в старший разряд и суммы.Управляющая шина 3 переключает регистр 1 10в режим кодово-позиционной схемы. Управляющая шина 4 разрешает прием информации на логические входы регистра 1, Управляющая шина 5 разрешает прием информации на логические входы регистра 2, По шинам шин 6 и 7 на вход сумматора подается соответственно прямой код слагаемого (В) и его отрицания (В), а по шинам 8 и 9 соответственно пряхтой код переноса из предыдущего разряда (Р) и его отрицания (Р) соответственно.По шинам 10 и 11 с регистра 2 выдается соответственно прямой код суммы (С) и его отрицания (С), а по шинам 12 и 1 т с регистра 1 выдается соответственно прямой код переноса в старший разряд (Р 1) и его отрица ния (Р,), Управляющие шины 14 и 15 предназначены для установки регистра 2 соответственно в единичное и нулевое состояние.Сумматор содержит также логические элементы ИЛИ 16 - 19 и И 20 - 29.30 В исходном состоянии уровень сигнала на314746 1 О 1 сз . 1и 1 ззд,1 зазз 35 шине б соответствует нулю информации, при этом логические входы регистра 2 заблокированы от сигналов, изменяющих его состояние.Сложение в сумматоре производят в два такта, Начало первого такта определяется моментом времени 1 (фиг. 2), при котором происходит изменение на шине б уровня сигнала на значение, соответствующее нулю, после чего в некоторые моменты времени , 1+:4 т .1+.з 1 происходят изменения уровней сигналов: на шине 3, на значение, соответствующее нулю, на шине 4 на значение, соответствующее единице, и подается код очередного слагаемого на шины б и 7 (т - некоторое минимальное, но гарантированное времи, учитываюгцее нестабильность управляющих серий и крутизну фронтов импульсов; Л 1 - некоторое гарантированное время, в течение которого заканчиваются указанные изменения сигналов на шинах 3 - 7),Под действием нулевого уровня на шине б блокируются логические входы регистра 2.Сипнал единичного уровня на шине 4 разрешает поступление информации на логические входы регистра 1, который под действием сигнала нулевого уровня на шине 3 переключается в режим кодово-позиционной схемы, при этом через время Т=1+1 зз(где- время переклочения регистра 1) вырабатываются сигналы, определяемые логическими уравнениями: Р, = ВС 11., х ВРИз , СРИ.,; Р, - ВСИзВРИ., СРИ где символами И, В, Р, С, Р обозначены сигналы на шинах 4, б, 8, 10 и 12; а символ- ми В, Р, С и Р, - сигналы на шинах 7, 9, (1 и 13 соответственно.Через время Т , =М+ и . 1 ззз, (где и 1 ззз, - время распространения переноса в,кодово;позиционной схеме и-разрядпого сумматора) заканчивается переключение элементов, меняющих свое состояние в первом такте сложения и происходит изменение на шине 3 уровня сигнала на значение, соогвстствующее единице, переключающее регистр 1 в регистровый режущим работы, фиксируя тем самым значения лопичеоких функций Р, и Р. На этом заканчивается первый такт и начинается второй такт сложения.Через время Т, +Л,на шине 4 происходит :изменение уровня сигнала па значение соответствующее нулю, при этом блокируются логические входы регистра 1, а затем через время Т,+2 на шине б происходит изменение уровня сигнала на значение, соответствуюгцее единице. При этом разрешается поступление иформации на логические входы 5 регистра 2, функции возбуждения которых определяются логическими уравнениями соответственно для единичного и нулевого входов: О,д,ВР,ИРР,И,где символом И обозначено единичноезначение сигнала на шине б.15 В соответствии с полученными значениями функций Возбуждения формируется (фиг.3) значение суммы на регистре 2, а именно: С=1, если д,=1;20 С=1, если д; =1;и - , если о, = д, - .О.с=сЧерез время Т == Т,+24 т+1(где1 зз.з - время переключения регистра 2) заканчивается второй такт сложения и происходит изменение на шине б уровня сигнала на значение соответствующее нуло, которое блокирует логические входы регистра 2,Полное время сложения двух и-разрядныхчисел в предлагаемом сумматоре, построенном на потенциальном комплексе элементов, ,равняется Предмет изооретения Параллельный сумматор на потепциаль 4 п ных элементах, содержащий регистр суммы,,регистр переноса и логические схемы И и ИЛИ, отличающийся тем, что, с целью сокращения затрат оборудования, единичный выход регистра переноса соединен со входа ми первой и второй схем И, другие входыкоторых соединены соответственно с шиной инверсного кода слагаемого и шиной инверсного кода переноса, выходы этих схем через схему ИЛИ соединены с нулевым входом 5 О регистра суммы, нулевой выход регистра переноса соединен со входами третьей и четвертой схем И, другие входы которых соединены соответственно с шиной прямого кода слагаемого и прямого кода переноса, выходы схем 55 И через схему ИЛИ соединены с единичным входом регистра суммы.

СмотретьЗаявка

1347297

В. А. Зубков, В. А. Сивохин

МПК / Метки

МПК: G06F 7/50

Метки: параллельный, сумматор

Опубликовано: 01.01.1971

Код ссылки

<a href="https://patents.su/3-314746-parallelnyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный сумматор</a>

Предыдущий патент: Устройство для смешения жидковязких составов

Следующий патент: Стабилизатор термоокисления изопропенилбензолов

Случайный патент: Холодная мастика