Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

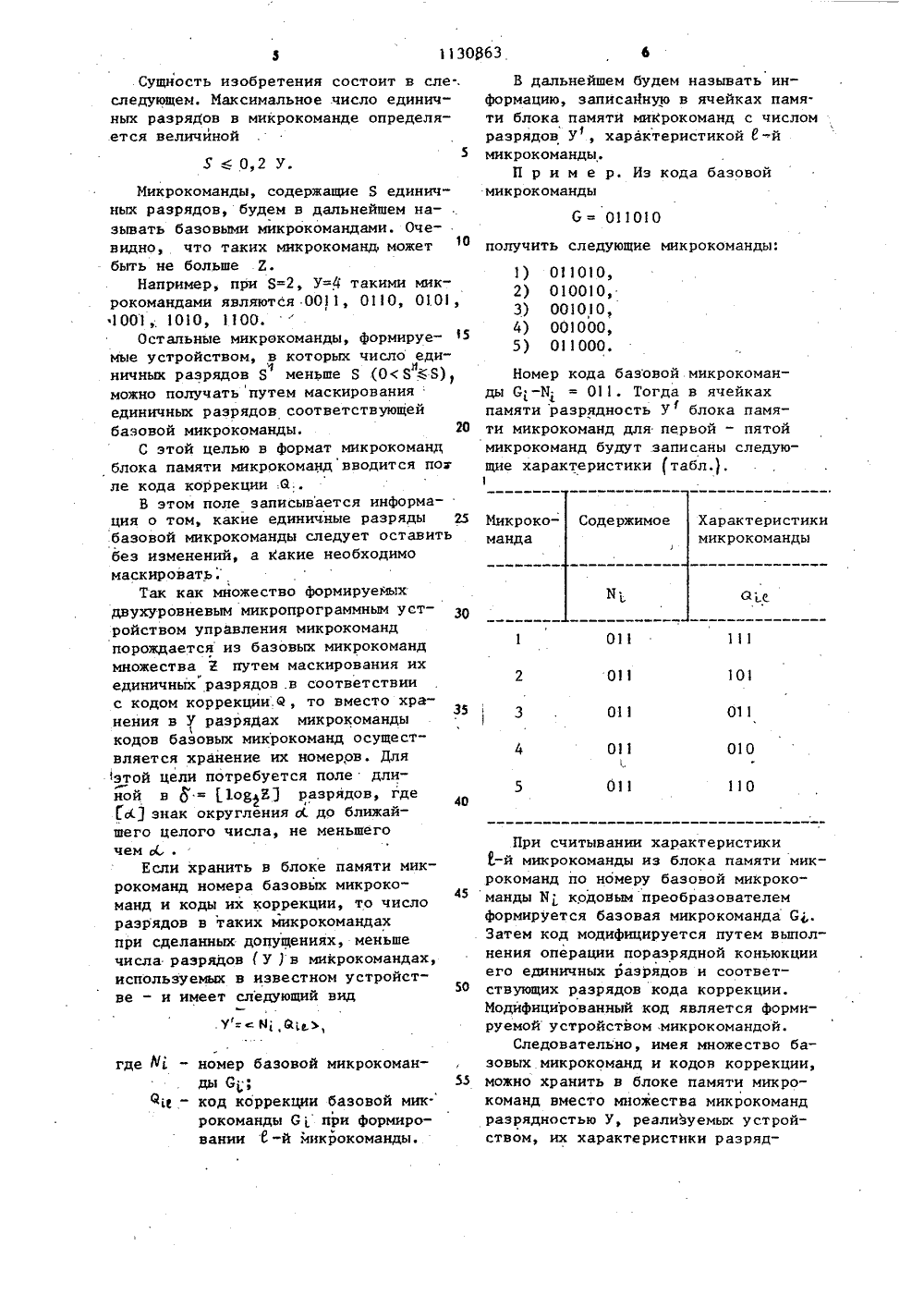

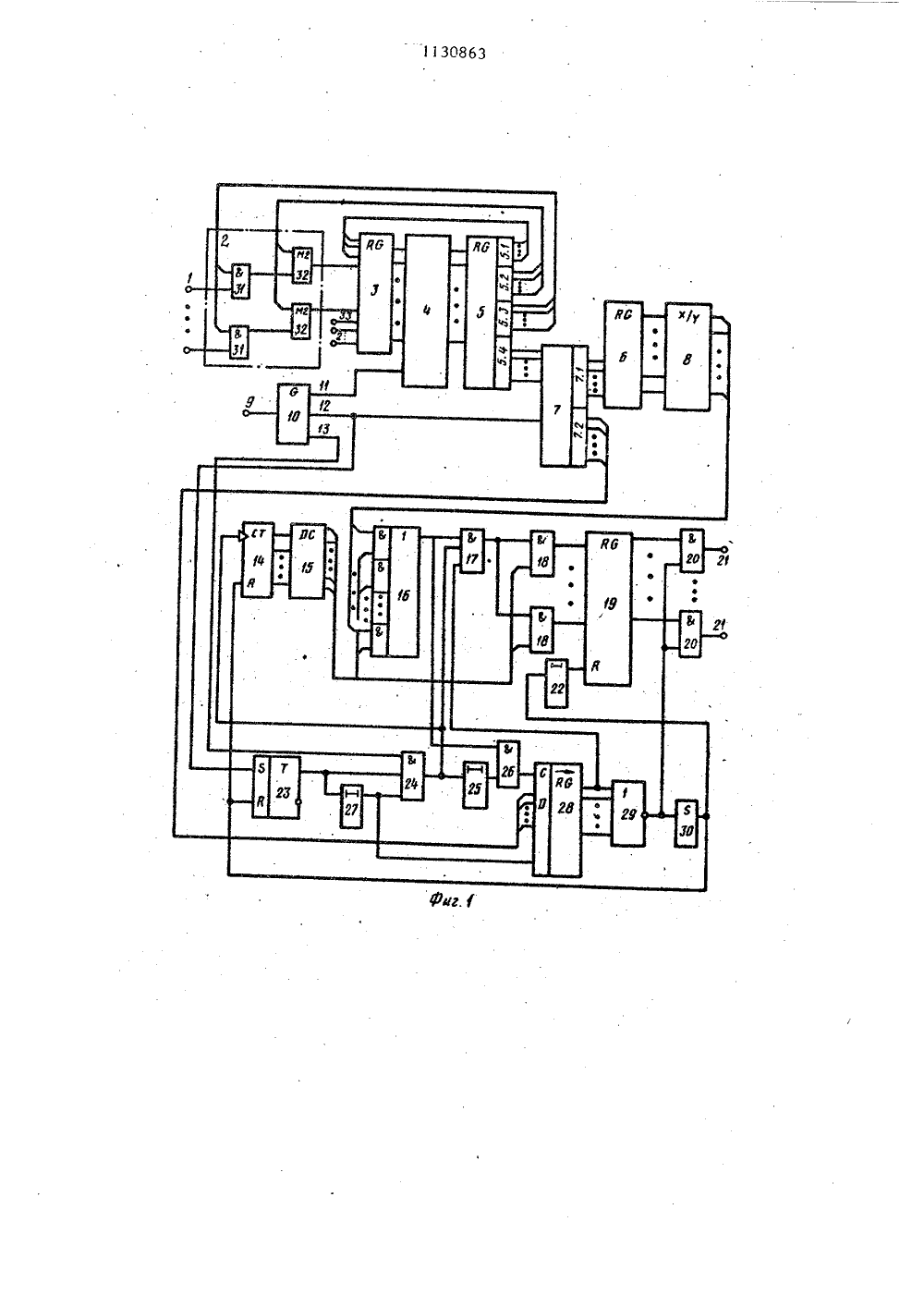

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН 63 А 091 (И) зШ С 06 Р 9/22 ИСАНИЕ ИЗОБРЕТЕНИ ЛЬСТ ев,Л.С.Соронко о ССС 75.и- 16,ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТКРЫТИЙ АВТОРСКОМУ СВИД(54) (57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее блок модификации адреса, регистр адреса, блокпамяти адресов микрокоманд, регистрадреса микрокоманды, блок памятимикрокоманд, регистр микрокоманды,коммутатор, генератор тактовых импульсов, триггер, первый элемент И,счетчик, дешифратор, регистр сдвига, причем входы сигналов логическихусловий устройства соединены с первой группой входов блока модификации адреса, выходы которого соединены с первой группой входов регистра адреса, выходы которого соединеныс адресными входами блока памятиадресов микрокоманд, выходы которогосоединены с входами регистра адресамикрокоманды, первая группа выходовкоторого соединена с второй группойвходов регистра адреса, вторая итретья группы выходов - соответственно с второй и третьей группами входовблока модификации адреса, четвертаягруппа выходов вс адресными входамиблока памяти микрокоманд, перваягруппа выходов которого соединена свходами регистра микрокоманды, вьг ходы счетчика соединены соответственно. с входами дешифратора, выходы которого, соединены с управляющими,входами коммутатора, входы кода операции устройства соединены с третьей группой входов регистра адреса, вход сигнала "Пуск" устройства соединен с входом генератора тактовых импульсов, первый выход которого соединен с управляющим входом блока памяти микрокоманд, второй выход - с первым входом первого элемента И, отличающее с я тем, что, с целью сокращения объема оборудования, оно содержит первый, второй и третий элементы задержки, второй итретий элементы И, одновибратор, элемент ИЛИ-НЕ, первый и второй блоки элементов И, регистр микроопераций, преобразователь кода микрокоманды, причем выходы регистра микрокомандысоединены с входами преобразователя, ф кода микрокоманды, выходы которого соединены с информационными входами коммутатора, выход которого соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с первыми входами первого блока элементов И, выходы которого соединены с входами регистра микроопераций, выходы которого соединены с первыми входами второго блока элементов И, выходы которого соединены с выходами микро- операций устройства, первый выход генератора тактовых импульСов соединен с единичным входом триггера, единичный выход которого соединеч с вторым входом первого элемента И и через первый элемент задержки - с третьим входом первого элемента И1130863 и управляющим входом регистра сдвига, выход первого элемента И сое.дннен со счетным входом счетчика,вторым входом второго элемента И ичерез второй элемент задержки - свторым входом третьего элемента И,выход которого соединен с входомсинхронизации регистра сдвига,вторая группа выходов блока памятимикрокоманд соединена синформационными входами регистра сдвига,первый выход которого соединен стретьим входом второго элемента И,выходы регистра сдвига соединены со 1 Изобретение относится к автоматике, вычислительной технике, передаче данных и может быть использовано при проектировании микропрограммных устройств управления цифровых 5 систем.Известно двухуровневое микропрограммное устройство управления которое содержит два блока памяти, дешифратор, счетчик, регистр адре са, генератор тактОвых импульсов, два блока элементов И, два элемента задержки, элемент ИЛИ-НЕ Г 11Недостатком указанного устройства является большая избыточность 15 блока памяти микрокоманд, обусловленная низкой информативностью заполнения ячеек памяти.Наиболее близким по технической сущности и достигаемому положитель ному эффекту к изобретению является двухуровневое микропрограммное устройство управления, содержащее блок модификации адреса, регистр адреса, блок памяти адресов микрокоманд, ре гистр адреса микрокоманды, блок памяти микрокоманд, регистр микрокоманды, коммутатор, генератор тактовых импульсов, триггер, первый элемент И, счетчик, дешифратор, регистр ЗО сдвига, причем входы сигналов логических условий устройства соединены с первой группой входов блока модификации адреса, выходы. блока модификации адреса соединены с адресными входами блока памяти адресов микро- команд, выходы которого соединены с ответственно с входами элементаИЛИ-НЕ, выход. которого соединен свторыми входами второго блока элементов И и с входом одновибратора,выход которого соединен с входамисброса счетчика и триггера, а через третий элемент задержки - свходом сброса регистра микроопераций, третий выход генератора тактовых импульсов соединен с управляющим входом блока памяти адресов микрокоманд, выходы дешифратора соединены с вторыми входами первогоблока элементов И соответственно. входами регистра адреса микрокоманды, первая группа выходов которогосоединена с второй группой входоврегистра адреса, вторая и третьягруппы выходов соединены соответственно с второй и третьей группой входов блока модификации адреса, четвертая группа выходов соеди,нена с адресными входами блока памяти микрокоманд, первая группа выходов которого - с входами регистрамикрокомандыф вьиоды счетчика соединены с входами дешифратора, выходы которого - с управляющими входами коммутатора, выходы кода операции устройства соединены с третьейгруппой входов регистра адреса,вход сигнала "Пуск" соединен с входом генератора тактовых импульсов,первый выход которого соединен с управляющим входом блока памяти микрокоманд, второй выход - с первым входом первого элемента И 123.Недостатками, ограничивающими область применения известного устройства, являются большая избыточность блока памяти микрокоманд и низкий коэффициент информативного заполнения блоков памяти.Большой объем оборудования обусловлен тем, что 1 ОХ разрядов микрокоманд, формируемых двухуровневым микропрограммным устройством управления; содержит полезную 1 значащую) информацию.В то же время 80-907 разрядов выполняемьи микрокоманд не содержит полезной информации, т.е.Цель изобретения - сокращениеобъема оборудования,В микропрограммное устройствоуправления, содержащее блок модификации адреса, регистр адреса,блок памяти адресов микрокоманд.,регистр адреса микрокоманды, блокпамяти микрокоманд, регистр микро.команды, коммутатор, генератор такЗОтовых импульсов, триггер, первыйэлемент И,. счетчик, дешифратор,регистр сдвига, причем входы сигналов логических условий устройства соединены с первой группой входов блока модификации адреса, вы- З 5ходы которого соединены с первойгруппой входов регистра адреса,выходы которого соединены с адресными входами блока памяти адресовмикрокоманд выходы которого соедииены с входами регистра адреса микрокоманды, первая группа выходовкоторого соединена с второй группойвходов регистра адреса, вторая итретья группы выходов в . соответственно с второй и третьей группамивходов блока модификации адреса,четвертая группа выходов - с адресными входами блока памяти микрокоманд, первая группа выходов которого соединена с входами регистра мик, рокоманцы, выходы счетчика соединены с входами дешифратора, выходы которого соединены с управляющими входами коммутатора, входы кода операции устройства соединены с третьейгруппой входов регистра адреса, входсигнала "Пуск" устройства соединен с 50 являются информационно избыточными.Поскольку в известном устройстве реализовано горизонтальное кодирование микрокоманд, когда каждой 5 микрооперации соответствует отдельный разряд кода, то это приводит к тому, что в рассмотренном случае коэффициент информативного заполнения блока памяти также составит 1 О О, 18,Таким образом, большой объем оборудования известного устройства обусловлен реализованным в нем горизонтальным кодированием микрокоманд и 15 отсутствием специальных технических средств, обеспечивающих декодирование микрокоманд при более эффективном методе кодирования, учитывающем малое содержание в них единиц. 20 входом генератора тактовых импульсов, первый выход которого соединен с управляющим входом блока памяти микрокоманд, второй выход - с первым входом первого элемента И, дополнительно введены первый,второй, и третий элементы задержки, второй и третий элементы И, одновибратор, элемент ИЛИ в , первый и второй блоки элементов И, регистр микроопераций, преобразователь кода микрокоманды, причем выходы регистра микрокоманды соединены с входами преобразователя кода микрокоманды, выходы которого соединены с информационными входами коммутатора, выход которого соединен с первыми входами второго и третЬего элементов И, выход второго элемента И соединен с первыми входами первого блока элементов И выходы которого соединены с входами регистра микроопераций, выходы которого соединены с первыми входами второго блока элементов И, выходы которого соединены с выходами микро- операций устройства, первый выход генератора тактовых импульсов соединен с единичным входом триггера, единичный выход которого соединен с вторым входом первого элемента, И и через первый элемент задержки - с третьим входом первого элемента И и управляющим входом регистра сдвига, выход первого элемента И соединен со счетным входом счетчика, вторым входом второго элемента И и через второй элемент задержки - с вторым входом треть-его элемента И, выход которого соединен с входом синхронизации регистра сдвига, вторая группа выходов блока памяти микрокоманд соединена с информационными входами регистра сдвига, первый выход которого соединен с третьим входом второго элемента И, выходы регистра сдвига соединены соответственно с входами элемента ИЛИ-НЕЪвыход которого соединен с вторыми входами второго блока элементов И и с входом одновибратора, выход которого соединен с входами сброса счетчика и триггера и через третий элемент задержки - с входом сброса регистра микроопераци, третий выход генератора тактовых импульсов соединен с управляющим входом блока памяти адресов микрокомайд,. выходы дешиф 1 атора соединены с вторыми входами первого блока элементов И соответственно.Сущность изобретения состоит в сле., следующем. Максимальное число единичных разрядов в микрокоманде определяется величиной5 с 0,2 У.Микрокоманды, содержащие Б единичных разрядов, будем в дальнейшем на-зывать базовыми микрокомандами. Очевидно, что таких микрокоманд можетбыть не больше 2.Например, при 8=2, У=4 такими микрокомандами являются 0011, 0110, 01.01,1001, 1010, 1100.Остальные микрокоманды, формируемые устройством, в которых число единичнык разрядов Я меньше 3 (0(3 Б),и.можно получать путем маскированияединичных разрядов соответствующейбазовой микрокоманды. 20С этой целью в формат микрокомандблока памяти микрокоманд вводится позле кода коррекции й,.В этом поле записывается информация о том, какие единичные разряды 25.базовой микрокоманды следует оставитьбез изменений, а какие необходимомаскировать."Так как множество формируемыхдвухуровневым микропрограммным устройством управления микрокомандпорождается из базовых микрокомандмножества 2 путем маскирования ихединичных разрядов .в соответствиис кодом коррекции.1, то вместо хранения в У разрядах микрокомандыкодов базовых микрокоманд осуществляется хранение их номеров. Дляэтой цели потребуется поле длийой в О = 1 одЕ разрядов, гдеГд.1 знак округления о. до ближайшего целого числа, не меньшегочем.Если хранить в блоке памяти микрокоманд номера базовых микрокоманд и коды их коррекции, то числоразрядов в таких микрокомандахпри сделанных допущениях, меньшечисла разрядовУ ) в микрокомандах,используемых в известном устройст 0ве - и имеет следующий видУ= й 1,йр.ъ,где Фь - номер базовой микрокоманды С,55П - код коррекции базовой мик.рокоманды Спри формировании Ю -й микрокоманды.В дальнейшем будем называть информацию, записанную в ячейках памя. ти блока памяти микрокоманд с числом разрядов У , характеристикой 0-й микрокоманды.П р и м е р. Из кода базовой микрокоманды 6 = 011010 получить следующие микрокоманды: 1) 011010,2) 010010,3) 0010 О,4) 001000,5) 011000. Номер кода базовой микрокоманды С;-Г 1 = 011. Тогда в ячейках памяти разрядность У блока памяти микрокоманд для первой - пятой микрокоманд будут .записаны следующие характеристики табл.1.Микрокоманда Характеристикимикрокоманды Содержимое 011 101 011 3011 011 011 011 010 110 При считывании характеристики -й микрокоманды из блока памяти микрокоманд по номеру базовой микрокоманды 0 кодовым преобразователем формируется базовая микрокоманда С. Затем код модифицируется путем выполнения операции поразрядной коньюкции его единичных разрядов и соответствующих разрядов кода коррекции. Модифицированный код является формируемой устройством микрокомандой.Следовательно, имея множество базовых микрокоманд и кодов коррекции, можно хранить в блоке памяти микро- команд вместо множества микрокоманд разрядностью У, реализуемых устройством, их характеристики разряд55 ностью Уф. Такая возможность реализуется в предлагаемом устройстве.На фиг.1 представлена функциональная схема предлагаемого микропрограмм. ного устройства управления; на фиг.2 -5 временной график его функциониро-. вания.Микропрограммное устройство управления содержит 1 фиг.1) входы 1 сигналов логических условий, блок 2 10 модификации адреса, регистр 3 адреса, блок 4 памяти адресов микроко манд, регистр 5 адреса микрокоманды, регистр 6 микрокоманды,блок 7 памяти микрокоманд, преобразователь 8 ко да микрокоманды, вход 9 сигнала "Пуск", генератор 10 тактовых импульсов с третьим 11, первым 12 и вторым 13 выходами, счетчик 14, дешифратор 15, коммутатор .16, второй 20 элемент И 17, первый блок элементов И 18, регистр 19 микроопераций второй блок элементов И 20, выходы 21 микроопераций устройства, третий элемент 22 задержки, триггер 23, первый 25 элемент И 24, второй элемент 25 задержки, третий элемент И 26, первый элемент 27 задержки, регистр 28 сдвига, элемент ИЛИ-НЕ 29, одновибратор 30, блок элементов И 31, группу ,сумматоров 32 по модулю два, входы 33 кода операции.Предлагаемое микропрограммное устройство управления функционирует следующим образом.Код очередной операции с группы входов 33 поступает на регистр 3.С приходом сигнала "Пуск" на вход 9 устройства происходит запуск генератора 10. Тактовый импульс после 40 довательности импульсов с выхода 11 генератора 10 поступает на управщпощий вход блока 4 памяти. При этом по адресу, записанному в регистре 3, с него считывается в регистр 5 адрес 4 ная информация о характеристике -й микрокоманды. Далее код немодифицируемой части адреса характеристики 1+1-й микрокоманды с группы вьг ходов 5.1 записывается в регистр 3,50 код модифицируемой части адреса с группы выходов 5,2 и код проверяемого логического условия с группы выходов 5.3 регистра 5 поступают на вторую и третью группы входов блока 2 модификации адреса.Адрес характеристики ь-й микро- команды с выходов регистра 5 поступает на адресные входы блока 7памяти.С приходом очередного тактового импульса с выхода 12 генератора 1 О на управляющий вход. блока 7 памяти с него считывается характеристика о -й микрокоманде.Номер базовой микрокоманды с первой группы выходов 7.1 поступает в регистр 6. Код коррекции базовой микрокоманды с выходов 7.2 блока 7 памяти поступает в регистр 28 сдвига. Этим же импульсом триггер 23 устанавливается в единичное состояние.Так как содержимое регистра 28 сдвига становится ненулевым, то сигнал на выходе элемента ИЛИ-НЕ 29 исчезает и элементы И 20 блока элементов по управляющим входам закрываются.Припоявлении на выходе элемента 27 задержки сигнала элемент И 24, становится открытым по второму и . третьему входам.При этом, тактовые импульсы с выхода 13 генератора 1 О через элемент И 24 поступают на счетный вход счетчика 14, на элемент И 17 и через элемент 25 задержки на элемент И 26.С поступлением первого импульса содержимое счетчика 14 увеличивается на единицу и становится равным единице.На .первом выходе дешифратора 15У появляется единичный сигнал, поступающий на первый управляк 4 ий вход конг мутатора 16 и на управляющий вход первого элемента И 18 первого блока.,Младший разряд ( первый) базовоймикрокомаиды с первого выхода преоб.разователя 8 черезкоммутатор 16поступаетна первый. вход элемента И 17,На третий вход элемента И 17 поступает сигнал с.младшего разрядакода коррекции, записанного в регистре 28. На выходе элемента И 17 формируется сигнал, соответствующий первому разряду формируемой микрокоманады. Этот сигнал поступает через первый элемент. И 20 блока элементов,открытый по управляющему входу сигналом с выхода дешифратора 5, напервый вход группы входов регистра 19. В последний записывается вна"чение сигнала, соответствующего первому разряду микрокоманды.Если значение сигнала на первомыходе преобразователя 8 ненулевое=1), то выходной сигнал элемен -та 25 задержки проходит через эле. -мент И 26 на вход синхронизации регистра 28. Содержимое последнегосдвигается на один разряд вправо,и в младший разряд записывается значение разряда кода коррекции.Если значение сигнала напервом Овыходе преобразователя 8 нулевое, то сигнал на выходе элементаИ 26 отсутствует. При этом содержимое регистра 28 не изменяется. С поступлением второго тактового импульса содержимое счетчика 14 увеличивается на единицу и становится равнымдвум.На втором выходе дешифратора 15появляется единичный сигнал. Далее 20осуществляется формирование второгоразряда микрокоманды аналогично описанному алгоритму формирования первого разряда.С поступлением третьего 1,-го импульсов на элемент И 24 аналогичноописанному алгоритму формированияразрядов осуществляется формированиеостальных разрядов микрокоманды изаписи их значений в регистр 19,После формирования разряда микрокоманды, для которого содержимоеК-го разряда базовой микрокомандыС ненулевое, а К+1 в 1 -й разряды -нулевые, содержимое регистра,2835становится нулевым.При этом на выходе элементаИЛИ-НЕ 29 появляется высокий потенциал.Элементы И 20 блока элементов от 40 крываются по управляющему входу, и сигналы микроопераций -й микро- команды с регистра 19 поступают на выходы 21. микроопераций устройства.Кроме того, сигнал с выхода элемента ИЛИ-НЕ 29 запускает одновибратор 30. Выходной импульс одновибратора 30 поступает на К -входы тригге 50 ра 23, счетчика 14 и через элемент 22 задержки на-вход регистра 19 и переводит их в нулевое состояние.В процессе выполнения 1:-й микро-команды в блоке 2 модификации адреса осуществляется формирование модифицированной части адреса кода адреса характеристики +1-й микрокоманды,Формирование модифицированной части адреса осуществляется следующим образом.На первые входы элементов И 31 группы элементов блока 2 модификации адреса поступает код с группы выходов 5.3 регистра 5.На вторые входы группы элементов И 31 поступают сигналы логических условий с входов 1 логических условий, Выходные сигналы группы элементов И 31 поступают на первые входы со - ответствующих сумматоров 32 по модулю два группы сумматоров, на вторые входы которых поступает код с выходов 5.2 регистра 5.Навыходах группы сумматоров 32 по модулю два формируется код модифицированной части адреса кода адреса характеристики Р +1-й микрокоманды и через выходы с блока 2 модификации адреса поступает в регистр :3 адреса. С приходом очередного .тактового импульса на управляющий вход блока 4 памяти в соответствии созначением адреса, записанного в регистре. 3, из блока 4 памяти считываетСя код адреса характеристики Е+1-й микрокоманды и базовый адрес кода адреса характеристики+2-й микрокоманды.Считанная информация записывается в регистр 5.Далее устройство функционирует аналогично алгоритму функционирования при формировании г,тй микрокоманды.Оценим технико-экономическую эффек. тивность изобретения.Так как 90-957 сложности микро - программных устройств управления составляет сложность блоков памяти микрокоманд и лишь 5-107 - сложность аппаратурного обрамления, то будем оценивать сложность микропрограммных устройств управления сложностью блоков памяти.С учетом этого допущения сложность известного микропрограммного устройства управления оценивается выражениемС = С + Со 1где С 1, - сложность блока 4 памяти 1 Со, - сложность блока 7 памяти,СоответственноСц= КйЛ,где 1 - множество реализуемых устройством мцкрокоманд;1130863 Составитель Л. Логачевактор Р.Цицика Техред И.Асталош рректо озмаи 8 одписно г.ужгород, ул.Проектная,4 Пате каз 9611/35 ВНИИПИ Г по дел 113035, Тираж ударствен изобрете сква Жого ко ий и оРауш тета СССРрытийая наб., д

СмотретьЗаявка

3497256, 06.10.1982

ПРЕДПРИЯТИЕ ПЯ Г-4190

КУЗНЕЦОВ СТАНИСЛАВ ВАЛЕНТИНОВИЧ, НИКОЛАЕВ ЮРИЙ ИВАНОВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, КЛЮЧКО ВЛАДИМИР ИГНАТЬЕВИЧ, СОРОКА ЛЕОНИД СТЕПАНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.12.1984

Код ссылки

<a href="https://patents.su/9-1130863-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Вычислительное устройство

Следующий патент: Микропрограммное устройство управления

Случайный патент: Арифметическое устройство для цифровой вычислительной машины