Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

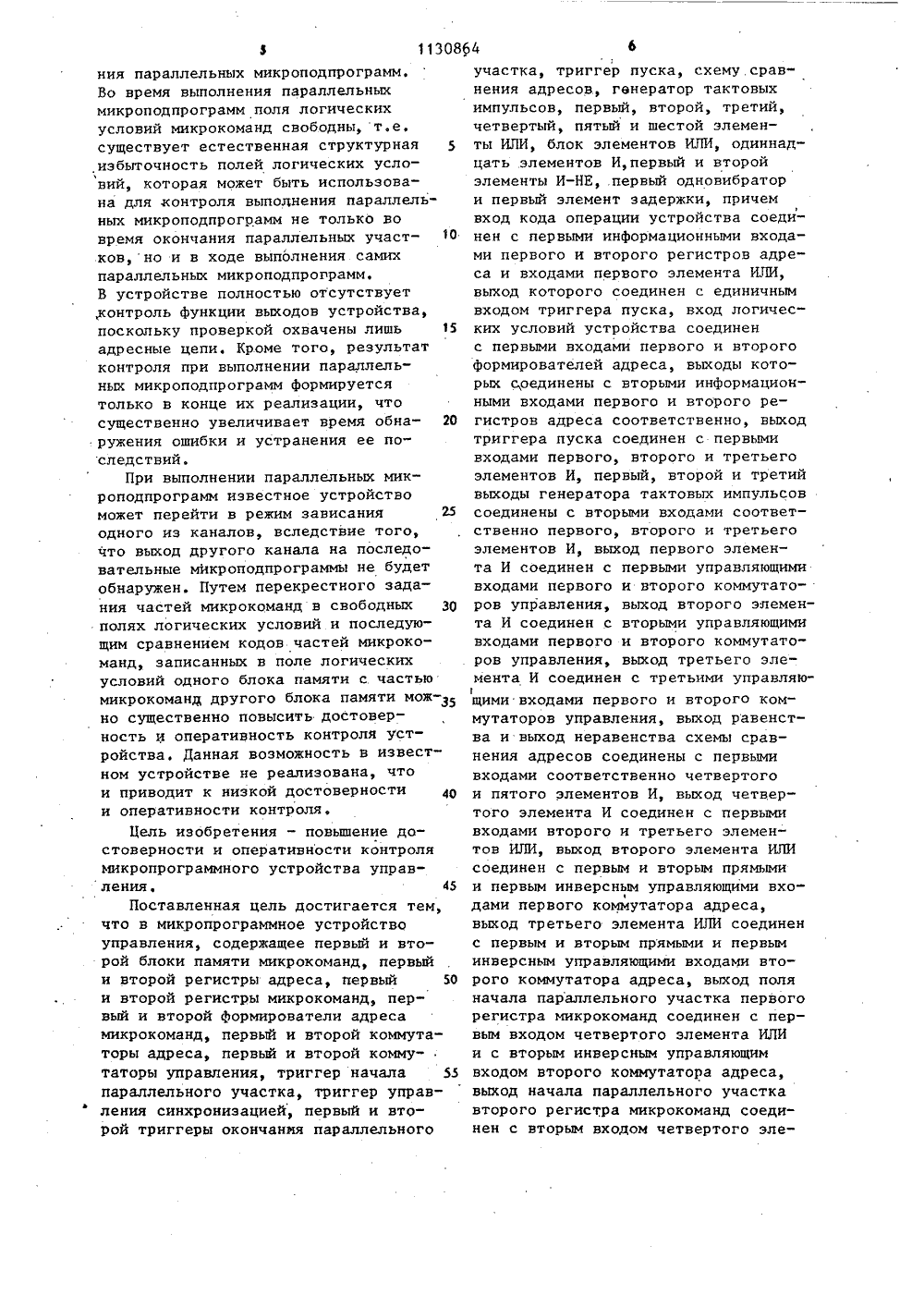

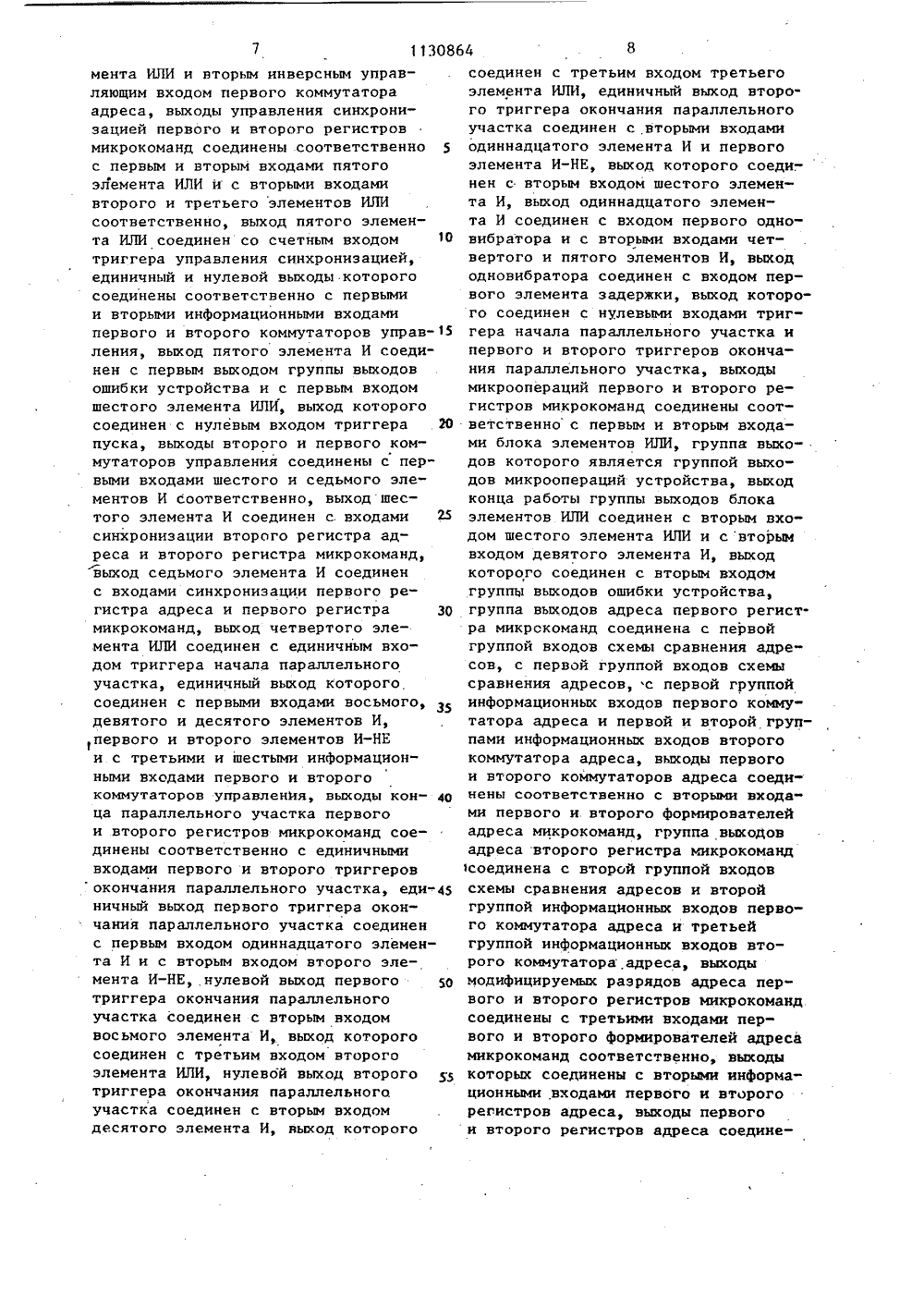

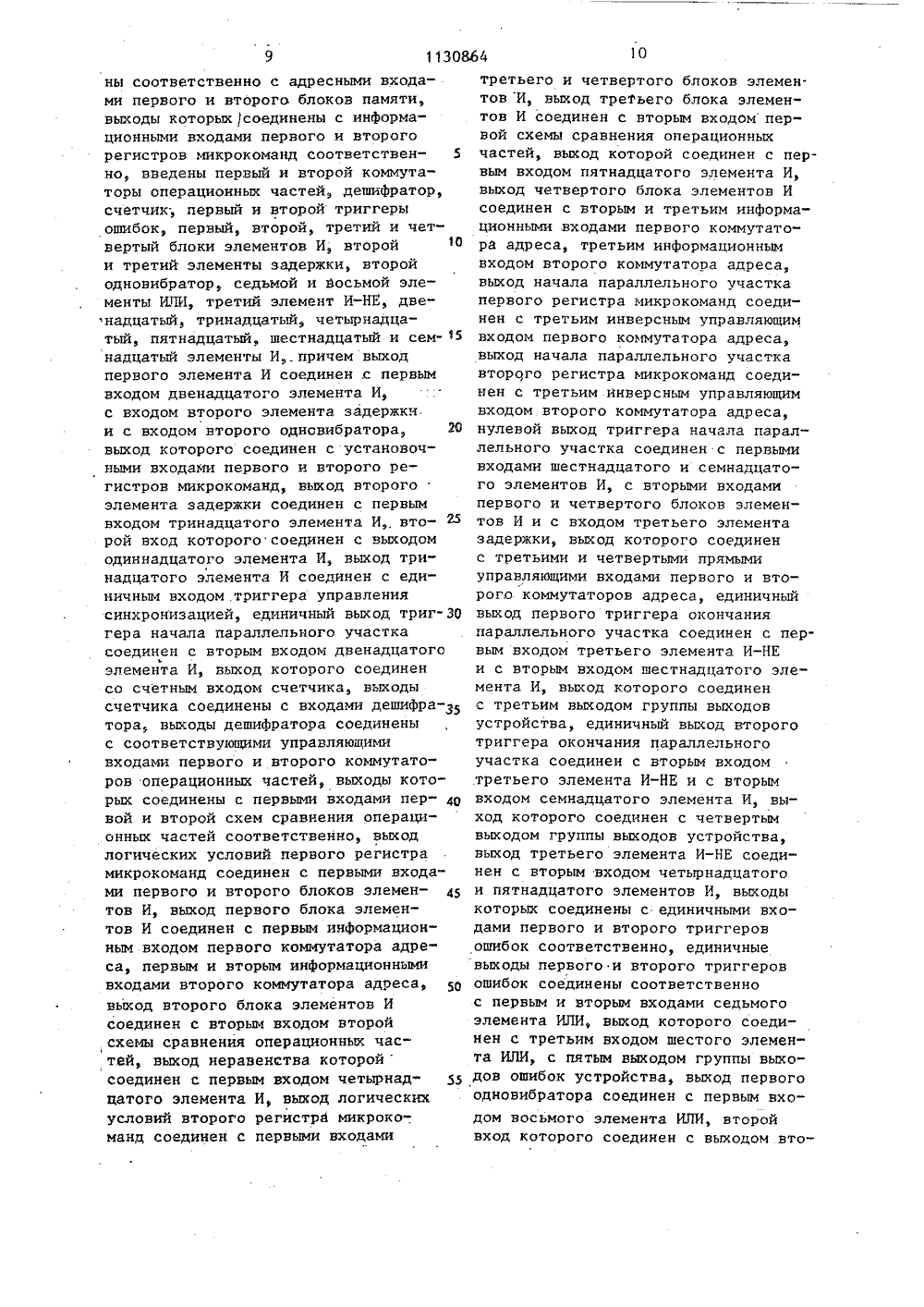

. РЕСПУБЛИК 4 А ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗОБРЕ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) 1. Авторское свидетельство СССРУ 437072, кл. С 06 Р 9/22, 1977.2. Авторское свидетельство СССРУ 451080, кл, С 06 Р 9/22, 1974,3. Авторское свидетельство СССРУ 830383, кл. С 06 Р 9/22, 1981.4. Авторское свидетельство СССРУ 1020825, кл. С 06 Р 9/22, 1982(прототип),(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО .УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд,.первыйи второй регистры адреса, первыйи второй регистры мнкрокоманд, первый и второй формирователи адресамикрокоманд, первый и второй коммутаторы адреса, первый и второй коммутаторы управления, триггер началапараллельного участка, триггер управления синхронизацией, первый и второй триггеры окончания параллельногоучастка, триггер пуска, схему сравнения адресов, генератор тактовыхимпульсов, первый, второй, третий,четвертый, пятый и шестой элементы ИЛИ, блок элементов ИЛИ, одиннадцать элементов И, первый и второйэлементы И-НЕ,.первый одновибратори первый элемент задержки, причемвход кода операции устройства соединен с первыми информационными входами первого и второго регистров адре 06. Р 9/22; С 06 Р 11/О са и входами первого элемента ИЛИ,выход которого соединен с единичнымвходом триггера пуска, вход логических условий устройства соединенс первыми входами первого и второгоформирователей адреса, выходы которых соединены с вторыми информационными входами первого и второго регистров адреса соответственно, выходтриггера пуска соединен с первымивходами первого, второго и третьегоэлементов И, первый, второй и третийвыходы генератора тактовых импульсов соединены с вторыми входами соответственно первого, второго и третьего элементов И, выход первогоэлемента И соединен с первыми управ-,ляющими входами первого и второгокоммутаторов управления, выход второго элемента И соединен с вторымиуправляющими входами первого и второго коммутаторов управления, выходтретьего элемента И соединен с третьими управляющими входами первогои второго коммутаторов управления,выход равенства и выход неравенствасхемы сравнения адресов соединеныс первыми входами соответственно четвертого и пятого элементов И, выходчетвертого элемента И соединен с первыми входами второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первым и вторымпрямыми и первыми инверсным управляющими входами первого коммутатора адреса, выход третьего элемента ИЛИсоединен с первым и вторым прямымии первым инверсным управляющими входами второго коммутатора адреса,выход поля начала параллельногоного участка, триггер 27 пуска,второй одновибратор 28, первый элемент 29 задержки, первый одновибратор 30, второй элемент 31 задержки,первый блок элементов И 32, второй 5блок элементов И 33, третий блокэлементов И 34, четвертый блок элементов И 35, первый элемент И 36,1второй элемент И 37, третий элемент И 38, двенадцатый элемент И 39,четырнадцатый элемент Й 40, пятнадцатый элемент И 41, четвертый эле-,мент И 42, пятый элемент И 43, тринадцатый элемент И 44, семнадцатыйэлемент И 45, десятый элемент И 46,шестой элемент И 47, седьмой элемент И 48, одиннадцатый элемент И 49,восьмой элемент И 50, девятый эле.мент И 51,.шестнадцатый элемент И 52,первый элемент И-НЕ 53, второй элемент И-НЕ 54, блок элементов ИЛИ 55,первый элемент ИЛИ 56, второй элемент ИЛИ 57, третий элемент ИЛИ 58,четвертый элемент ИЛИ 59, пятый элемент ИЛИ 60, седьмой элемент ИЛИ 61,восьмой элемент ИЛИ 62, шестой элемент ИЛИ 63, третий элемент 64 задержки, третий элемент И-НЕ 65. Кроме того, на фиг. 1 показаны; вход 66кода операции устройства, выход 67 30микроопераций устройства, выход 671микрооперации конца работы, группавыходов 68 ошибки устройства, вы-ход 69 первого элемента И 36, выход 70 (71) второго (третьего) эле- Змента И 37 (38), единичный (нулевой)выход 72 (73) триггера 21 управлениясинхронизацией, выход 74 (75) полей 5.6 (6.1) управления синхронизацией регистра 5 (6) микрокоманд 40соответственно, выход 76 (77) восьмого (десятого) элемента И 50,(46),единичный выход 79 (78) первого(фиг. 2) содержит элемент ИЛИ 90 .я мультиплексор 91.На фиг, 3 показан формат микро- команд, хранящихся в ПЗУ 1 и ПЗУ 2, которые содержат: поле адреса А, поле микроопераций МО, поле логических условий ЛУ, модифицируемый разряд адреса МР метки М 1 М 2 и МЗ причем; 1, если микрокоманда является последней в параллельноймикроподпрограмме;О, в противном случае;1, если микрокоманда предшествует началу параллельноймикроподпрограммы,О, в противном случае;1, если после нечетной (четной) должна следовать нечетная (четная) микрокоманда;О, в противном случае. М =На временной диаграмме (фиг. 5) показаны изменения сигналов на входах-выходах элементов функциональйой схемы устройства, Числа на оси ординат указывают номера входов-выходов элементов функциональной схемы устройства, Последовательности синхроимпульсов 7, Г и Т соответствуют последовательностям синхроимпульсов на выходах 70, 71 и 69 функциональной схемы устройства соответственно. Кроме того, на фиг. 5 приняты следующие сокращения: РАМК 3 - регистр адреса микрокоманд 3, РМК 5 - регистр микрокоманд 5.Микропрограммное устройство управления содержит следующие группы технических средств: средства хранения и формирования микрокоманд; средст- ва управления и синхронизации; средства.управления адресацией и распараллеливанием; средства контроля.К средствам хранения и формирования микрокоманд относятся ПЗУ 1 и ПЗУ 2, регистры 3 и 4 адреса, регистры 5 и 6 микрокоманд, формирователи 10 и 11 адреса микрокоманд, коммутаторы. 12 и 13 адреса, Данные средства обеспечивают хранение последовательных и параллельных микроподпрограмм, формирование адресов очередных микрокоманд, а также формирование начальных адресов микроподпрограмм в соответствии с кодом операции.ПЗУ 1 и ПЗУ 2 предназначены для хранения последовательных и параллельньм микроподпрограмм. Параллель" ными микроподпрограммами назовемтакие микроподпрограммы, которые выполняются параллельно (одновременно) и независимо одна от другой. Адрес входа и выхода иэ параллельных микроподпрограмм одинаков для ПЗУ 1 5 и ПЗУ 2.Первый 3 и второй 4 регистры адреса предназначены для записи кодов операций, поступающих на вход 66 кода операции устройства, и адресов 10 очередных микрокоманд, формируемых в формирователях 10 и 11 адреса.Первый 10 и второй 11 формирователи адреса предназначены для формирования исполнительных адресов оче редных микрокоманд.Элемент ИЛИ 90 (фиг. 2) предназначен для модификации разряда адреса очередной микрокоманды, поступающего на вход 5,7 (6.7) формирователя 10 20 (11) адреса, в соответствии со значением проверяемого логического условия,Мультиплексор 91 (фиг. 2) предназначен для коммутации значений логических условий, поступающих на вход 89 устройства, в зависимости от кода логических условий, поступающего на вход 84 (85) формирователя 10 (11) адреса, Мультиплексор 91 реализует следующую логическую функ цию ъ1" = Ч х., где х - значение д-го логического условия на входе 89 устройства; 35 = ЛК3:1 где Г = К, если в соответствующем разряде поля 5.2 (6.5)регистра 5(6) записана "1", К, если в соответствующем разряде поля 5.2 (6.5) регистра 5(6) записан "0" 451 ш - разрядность поля логических условий регистра 5(6), микрокоманд; г - разрядность значений логических условий, поступающих на вход 89 устройства, первый 5 и второй 6 регистры микро- команд предназначены для записи микрокоманд, считываемых из ПЗУ 1 и ПЗУ 2 соответственно.Первъй 12 и второй 13 коммутаторы адреса предназначены для коммута 1 ции адресов очередных микрокоманд в различных режимах функционирования устройства,К средствам управления и синхронизации относятся генератор 20 такто вых импульсов, триггер 27 пуска, первый 36, второй 37, третий 38элементы И, первый 14 и второй 15коммутаторы управления, второйодновибратор 28, триггер 21 управления синхронизацией, блок элементов ИЛИ 55, пятый элемент ИЛИ 60, шестой элемент ИЛИ 63, восьмой элемент ИЛИ 62, первый 53 и второй 54элементы И-НЕ, четвертый 42, пятый 43, шестой 47 и седьмой 48 элементы И.Данная группа средств предназначена для синхронизации и управления работой элементов и узлов устройства. Генератор 20 тактовых импульсов предназначен для формирования трех последовательностей Т 1 - 75 тактовых импульсов.Триггер 27 пуска предназначен для управления работой первого 36, второго 37 и третьего 38 элементов И, которые на выходах 69, 70 и 71 формируют соответственно последовательности тактовых импульсовТ 5, 7 и Т. Первый 14 и второй 15 коммутаторы управления предназначены для коммутации тактовых импульсов- Т в зависимости от режима работы устройства.Триггер 21 управления синхронизацией предназначен для управления перетактовкой устройства. В точках перетактовки, когда после четной (нечетной) микрокоманды должна идти четная (нечетная) микрокоманда, по сигналу М 5 производится, изменение привязки номера тактового импульса к номеру блока памяти. При этом из одного блока памяти. ПЗУ 1 (ПЗУ 2) подряд считываются две микрокоманды. Второй одновибратор 28 предназначен для формирования еДиничного сигнала сброса операционных полей регистров 5 и 6 микрокоманд.Блок элементов ИЛИ 56 предназначен для формирования сигналов управ ления объектом в различных режи- мах функционирования. Пятый элемент ИЛИ 60 предназначен для формирования сигнала перетактовки, поступающего с регистра 5 или 6 микро- команд. Шестой элемент ИЛИ 63 предназначен для формирования сигнала; участка, элемент 29 задержки, одновибратор 30, элементы И 46, 49 и 50,ЗО элемент ИЛИ 59, второй элемент 31 задержки, элемент И 44, которые выполняют Функции: управления адресными цепями в зависимости от режима работы и тачки микропрограммы; реализации операций распараллеливания при переходе к выполнению параллельных микроподпрограмм; реализации операции объединения в точках схождения параллельных микроподпрограмм.Элемент 29 задержки предназначен для формирования сигнала сброса триггеров 24 - 26 после выхода из парал лельного выполнения микроподпрограмм. Адрес выхода записывается в регистр 3 адреса по тактовому импульсу, проходящему через элемент И 48, Разрешающим сигналом для прохождения такта- Ьо ваго импульса через элемент И 48 является единичный сигнал, Формируемый первым адновибратором 30 и проходящий через элемент ИЛИ 62. Затем про-,изводится перевод триггеров 24 - 26в нулевое исходное) состояние.Триггер 25 началапараллельногоучастка предназначен для управления останова устройства, восьмой элемент ИЛИ 62 предназначен для формирования единичного сигнала, управляющего прохождением тактовых импульсов через элемент И 48 на входы синхро низации регистра 3 адреса и регистра 5 микрокоманд. Первый 53 и второй 54 элемента И-НЕ предназначены для управления прохождением тактовых импульсов через элементы И ч 7 и 48,/ 10 Четвертый элемент И 42 предназначен для формирования управляющего. сигнала вмомент окончания параллельных микроподпрограмм. Пятый элемент И 43 предназначен для Формирования сигнала ошибки в момент окончания параллельных микроподпрограмм при.несовпадении адресов выхода из параллельного режима выполнения микроподпрограмм. Шестой 47 и седьмой 48 элементы И предназначены для управления прохождением тактовых импульсов на входы синхронизации регистров 3 и 4 адреса и регистров 5 и 6 микрокоманд.К средствам управления адресацией и распараллеливанием относятся коммутаторы, первый триггер 24 окончаработой устройства при одновременномвыполнении параллельных микроподпрограмм,Первый 24 и второй 26 триггерыокончания параллельных участков предназначены для блокировки прохождения тактовых импульсов на входысинхронизации регистров 3,5 и 4,6после выполнения параллельных участков.К средствам контроля устройстваотносятся схемы 7 и 8 сравненияоперационных частей, схема 9 сравнения адресов, коммутаторы 16 и 17операционных частей, счетчик 18, дешифратор 19, первый и второй триггеры 22 и 23 ошибок, первый-четвертыйблоки 32-35 элементов И, элементы И 39, 40, 41, 42, 43, 45, 51 и 52,элемент ИЛИ 61 и элемент И-НЕ 65.Указанные элементы осущестВляют оперативный контроль функционированияустройства при выполнении параллельных микроподпрограмм.Схема 9 сравнения адресов микрокоманд производит сравнение адресных частей микрокоманд, которые являются последними в параллельныхмикроподпрограммах, и формирует сигнал ошибки при их несовпадении./Схемы 7 и 8 сравнения операционныхчастей микрокоманд производят в па,раллельном режиме работы устройствасравнение групп разрядов операционных частей микрокоманд из одногоканала с кодами, записанными в сво бодных разрядах логических условийдругого канала. При несовпаденииконтролируемых разрядов происходитформирование сигнала ошибки и останов устройства, Элемент И 51 формирует сигнал ошибкй при выдаче операций конца работы при выполнениипараллельных микроподпрограмм. Элемент И 52 формирует сигнал ошибкипри считывании метки М из ПЗУ 1в параллельном режиме, элемент И 53формирует сигнал ошибки при считывании метки Мз из ПЗУ 2 в параллельном режиме. Счетчик 18 и дешифратор 19 предназначены для Формирования номеров групп разрядов операционных частей и управления коммутаторов 16 и 17 операционных частей.Устройство функционирует в следующих режимах: выполнения последовательных микроподпрограмм и выполнения параллельных микроподпрограмм,О Режим выполнения последовательных микроподпрограмм.В исходном состоянии все триггеры и регистры устройства находятся в нулевом состоянии. После прихода 5 кода операции начального адреса микроподпрограммы на вход 66 устройст- ва сигнал с выхода элемента ИЛИ 56 устанавливает триггер 27 в единичное состояние, который разрешает прохождение последовательностей тактовых импульсов 7, 7 и 7 через элементы И 36 - 38 соответственно. При этом, перед считыванием очередной микрокоманды тактовый импульс с выхода 69 подается на одновибратор 28, на выходе которого формируется единичный сигнал, производящий обнуление операционных полей регистров 5 и, 6 микрокоманд. Тактовый импульс с выхода 70 (71) элемента И 37 (38) через коммутатор 14. (15) и элемент И 48 (47) подается на входы синхронизации регистров 3 и 5 (4 и 6), причем запись инфбрмации в регистр 3 (4) происходит по переднему фронту тактового импульса, а в регистр 5 (6) - по заднему фронту тактового импульса, По переднему фронту тактового им пульса Т(7) происходит обращение к блоку памяти ПЗУ 1 (ПЗУ 2) микро- команд в соответствии с адресом микрокоманды, записанным в регистре 3 (4) адреса микрокоманд (РАМК). По заднему фронту ь () тактового импульса происходит запись микрокоманды из блока памяти ПЗУ 1 (ПЗУ 2) микрокоманд в регистр 5 (6) микро- команд. Адресная часть микрокоманды 4 О поля 5. 1 (6.6) регистра 5 (6) подается через коммутатор 13 (12) на вход формирователя 11 (10) адреса микрокоманд, Аналогично, код.логических условий с выхода 5.2(6.5) регистра 5 (6) через блок элементов И 32 (35) через коммутатор 13 (12) подается на вход формирователя 11 (10) адреса микрокоманд, В формирователе адреса (фиг. 3) микрокоманд код ло- ьо гических условий и логические условия с выхода 89 подаются на мультиплексор 91. На вход 6,7 (57) формирователя 11 (10) адреса микрокоманд поступает модифицируемый разряд ад- у реса, который формируется на выходе элемента ИЛИ 90 и поступает на выход формирователя 11 (10) адреса микрокоманд вместе с немодифицируемыми разрядами адреса.Адрес очередной микрокоманды с выхода формирователя .11 (10) адреса подается на информационный вход Р 2 регистра 4 (3).По очередному тактовому импульсу происходит обращение и считывание информации с ЛЗУ 2 (ПЗУ 1). В последующем работа устройства происходит аналогично рассмотренным тактам.Если после нечетной (четной) микрокоманды из блока памяти 1 (2) вновь должна быть считана нечетная (четная) микрокоманда, то в поле 5.6. (6.1) этой микрокоманды записывается единица, по которой затем триггер 21 устанавливается в единичное состояние, В результате этого на входе 72 коммутатора 14 (15) появляется разрешающий сигнал, который разрешает прохождение тактового импульса Т (7) с выхода 71 (70) элемента И 38 (37) через коммутатор 14 (15) и элемент И 48 (47) на регистры 3 и 5 (4 и 6). Таким образом, из ПЗУ 1 (ПЗУ 2) происходит считывание подряд двух микрокоманд и перетактовка, т.е. привозка синхроимпульсов к соответствующим регистрам без потери одного микротакта. При этом адрес и код логических условий следующей нечетной (четной) микрокоманды с полей 5.1 и 5,2 (6,6 и 6.5) регистра 5 (6) поступает через открытый сигналом с выхода элемента ИЛИ 57 (58) коммутатор 12 (13) в формирователь адреса 10 (11).При появлении очередной метки в поле 5.6 (61) вновь осуществляется перетактовка, и из одного блока памяти подряд считываются две микро- команды. Затем работы продолжается аналогично описанным тактам работы: считывание микрокоманд производится по очереди иэ одного и из другого блока памяти. При появлении метки в поле 5.5(6.2) регистра 5 (6) устройство переходит во второй режим работы,Режим выполнения иараллельных микроподпрограмм.При появлении метки М на выходе 5.5 регистра 5 формируется единичный сигнал, который проходит через элемент ИЛИ 59 и устанавливает триггер 25 в единичное состояние, открывая элементы И 50 и И 46, а также1 О коммутаторы 14 и 15 для прохождениятактовых импульсов й с выхода 69элемента И 36.Адрес с поля 5.1 и код логическихусловий с поля 5.2 регистра 5 микрокоманд через коммутаторы 12 и 13поступают на входы формирователей. 10и 11 соответственно.Разрешающими управляющими сигналами для прохождения кода адресаи кода логических условий с регистра 5 микрокоманд через коммутатор 12являются: единичный сигнал с выхода 76, проходящий через элемент ИЛИ 57 и поступающий на прямойуправляющий вход коммутатора 12адреса; нулевой сигнал с выхода поля метки М начала параллельногоучастка регистра 6 микрокоманд,поступающий на нулевой управляющийвход коммутатора 12 адреса,Разрешающими управляющими сигналами для прохождения кода адреса икода логических условий с регистра 525микрокоманд через коммутатор 13 являются: единичный сигнал с выхода 77,проходящий через элемент ИЛИ 58 ипоступающий на прямой управляющийвход коммутатора 13 адреса; нулевойсигнал с выхода поля метки М регист-ЗОра 6 микрокоманд, поступающий нанулевой управляющий вход коммутатора 13 адреса; единичный сигнал с выхода элемента 64 задержки, поступающий на прямой управляющий вход коммутатора 13 адреса (блокировка прохождения кода адреса и логическихусловий с регистра 5 через коммутатор 13 производится по нулевому сигналу, поступающего с нулевого выхода 81 триггера 25 начала параллельного участка через элемент 64 задержки).Таким образом, производится занесение начального адреса параллельных микроподпрограмм в регистры 3и 4 адреса по переднему фронту тактового импульса 15 . По заднему фронту тактового импульса 1 З производится запись первых микрокоманд в ре гистры 5 и 6, считанных из ПЗУ 1и ПЗУ 2 соответственно,Операционные части микрокомандчерез блок элементов ИЛИ 55 поступают на выход 67 устройства и через 55коммутаторы 16 и 17 на схемы 7 и 8сравнения соответственно. Адресныечасти с полей 5.1 (6;6) поступают через коммутатор 12 (13) в регистры 3 (4), код логических условийс поля 5.2 (6.5) через блок элементов И 33 (34) поступает на второйвход схемы 8 (7) сравнения, Очередным тактовым импульсом 7 с выхода 69происходит параллельное считываниемикрокоманд из ПЗУ 1 и ПЗУ 2, В дальнейшем эти два канала продолжают своюработу параллельно и независимо.После окончания одной из микроподпрограмм (например, первой, котораяхранится в блоке памяти ПЗУ 1) в поле 5.4 регистра 5 появляется меткаМ=1, и триггер 24 устанавливаетсяв единичное состояние. Элемент И 48блокируется нулевым сигналом, формируемым элементом И-НЕ 54 и проходящим через элемент ИЛИ 62. В результате тактовые импульсы на входы синхронизации регистров 3 и 5 не подаются. Данный канал переходит в режиможидания и находится в нем до окончания выполнения второй микроподпрограммы. После появления метки М 1=1в поле 6,3 регистра 6 устанавливается в единичное состояние триггер 26.После этого сигналом с выхода элемента И 49 производится сравнение содержимого полей адреса 5.1 и 6.6 регистров 5 и 6. Если адресные части последних микрокоманд совпадут, то сигналом с выхода элемента И 42, проходящим через элементы ИЛИ 57 и 58,разрешается передача адреса в реп . фгистр 3. Затем с задержкой 1.5 ) и(Г - длительность тактового импульса) одновибратор 30 производит обнуление триггеров 24 - 26,До того момента, как переключатсятриггеры 24-26,импульс с выхода 69,задерживаясь элементом. 3 1 задержкина время С ( , производит принудительную установку триггера 21 в единичное состояние. Одновременно, сигнал с выхода одновибратора 30, проходя через элемент ИЛИ 62, разрешаетпрохождение тактового импульсас выхода коммутатора 14 через элемент И 48 на входы синхронизациирегистров 3 и 5, В результате чегопринудительно производится считывание первой мнкрокоманды в последовательном режиме работы их первогоблока памяти ПЗУ 1. После того, какобнулятся триггеры 24-26, открываются элементы И 48 и 47, и по очередному тактовому импульсу с выхода23 64 11308 коммутатора 15 будет считана микро- команда из блока памяти ПЗУ 1. В дальнейшем устройство переходит в последовательный режим функционирования. При появлении на выхо де 67.1 блока элементов ИЛИ 55 мик. - рооперации.конца работы единичный сигнал через элемент ИЛИ 63 подается на нулевой вход триггера 27. Последний устанавливается в нулевое 10 состояние и запрещает прохождение тактовых импульсов с выходов генератора 20. Устройство прекращает свое функционирование.Рассмотрим особенности функциони рования средств контроля устройства при выполнении параллельных микро- подпрограмм, Сущность работы средств контроля заключается в следующем .(фиг. 4), При реализации параллель ных микроподпрограмм освобождаются ноля логических условий, В целях повышения достоверности и оперативности функционирования устройства свободные поля логических условий 25 регистров микрокоманд используются для контроля блоков памяти. Все,поле 5,3 (6.4) регистра 5 (6) разбивается на группы разрядов, например, на тетрады. Пусть имеется И тетрад. 30 В каждой тетраде записана команда. В разряды кода логических условий с поля 6,5 (5.2) для каждой микро- команды записывается команда из числа тех, которые записаны в тетрадах д 5 в поле 5,3 (6,4). На фиг, 4 и 5 А(В) команда, записываемая в поле 5.3 (6.4). При параллельном режиме работы производится сравнение поля логических условий и части поля 40 микроопераций, регистров 5 и 6 микро- команд. Рассмотрим реализацию данного алгоритма работы средств контроля.После того, как триггер 25 начала 45 параллельного участка сигналом с выхода элемента ИЛИ 59 устанавливается в единичное состояние, сигналом с выхода 80 разрешается прохождение кода логических условий на схемы 7 и 8зО сравнения; разрешается прохождение тактовых импульсов через элемент И 39 на вход счетчика 18, который формирует код номера одной из и-тетрад и обнуляется по сигналу переполне 55 ния; дешифратор 19 в соответствии с кодом, полученным от счетчика 18, производит поочередно опрос всех и-тетрад и передачу их содержимогона схемы 7 и 8 сравнения. Схемы 7и 8 сравнения сравнивают информацию,записанную в разрядах кода логических условий и разрядах поля микроопераций. При их несовпадении схемы 7 или 8 сравнения вырабатываютсигнал ошибки. Этот сигнал производит установку в единичное состояниетриггера 22 или 23,В случае, если устанавливается в единичное состояние триггер 24 и 26, то цепь прохождения сигнала ошибки от схем сравнения блокируется элементами И 40 и И 41. При установлении триггеров 22 или 23 в единичное состояние формируется сигнал ошибки устройства, и производится ,останов устройства. Кроме данного вида контроля, в устройстве производится сравнивание адресных частей микрокоманд регистров 5 и 6. Сравнение происходит после установки в единичное состояние триггеров 24 и 26окончания параллельных участков. В случае неравенства адресных. частей формируется сигнал ошибки устройства, и производится останов устройства. Кроме того, сигнал ошибки форми,руется при:появлении микрооперации конца работы на выходе 67,1 при вы полнении параллельного участка микропрограммы, при этом сигнал ошибкипроходит через открытый эле-.мент И .51, на выход группы выходовошибки устройства; появлении меткиконца параллельного участка микро- подпрограммы первого канала (ПЗУ 1) в последовательном режиме работы, при этом сигнал ошибки .проходит через элементы И 52 на выход группы выходов ошибки устройства; появлении метки конца параллельного участка микроподпрограммы второго канала(ПЗУ 2). в последовательном рерме,при этом сигнал .ошибки формируетсяэлементом И 45 и пбступает на выход группы выходов ошибки устройства. Таким образом, предлагаемое параллельное микропрограЯ 4 ное устройство управления с контролем отличается от известных технических решений повышением достоверности и оперативности контроля за счет использования естественной структурной избыточности полей логических условий .микро 3130864 26команд при выполнении параллельных микроподпрограмм путем органиэации задания в свободных полях логических условий частей микрокоманд параллель ных микроподпрограмм и последующего сравнения частей поля микроопераций и поля логических условий микрокоманд независимых параллельных микроподпрограмм,Применение изобретения поэволит 5 строить более надежные устройствауправления параллельными процессами..Проектная, 4 едактор Р.Цицик Государственного к о делам изобретени ква, Ж, Раушска Подписное митета СССР и открытий наб, д. 4/11участка первого регистра микрокомандсоединен с первым входом четвертогоэлемента ИЛИ и с вторым инверснымуправляющим входом второго коммутатора адреса, выход начала параллельного участка второго регистра микрокоманд соединен с вторым входом четвертого элемента ИЛИ и вторым инверс.ным управляющим входом первого коммутатора адреса, выходы управлениясинхронизацией первого и второгорегистров микрокоманд соединены соответственно с первым и вторым входами пятого элемента ИЛИ и с вторымивходами второго и третьего элементта ИЛИ соответственно, .выход пятогоэлемента ИЛИ соединен со счетнымвходом триггера управления синхрони-,зацией, единичный и нулевой выходыкоторого соединены соответственнос первыми и вторыми информационнымивходами первого и второго коммутаторов управления, выход пятого элемента И соединен с первым выходом группы выходов ошибки устройства и спервым входом шестого элемента ИЛИ,выход которого соединен с нулевымвходом триггера пуска, выходы второго и первого коммутаторов управления соединены с первыми входами шестого и седьмого элементов И соответ ственно, выход шестого элемента Исоединен с входами синхронизациивторого регистра адреса и второгорегистра микрокоманд, выход седьмого элемента И соединен с входамисинхронизации первого регистра адреса и первого регистра микрокоманд,выход четвертого элемента ИЛИ соединен с единичным входом триггера начала параллельного участка, единичный выход которого соединен с первыми входами восьмого, девятого и десятого элементов И, первого и второго элементов И-НЕ и с третьими ишестыми информационными входамипервого и второго коммутаторов управления, выходы конца параллельногоучастка первого и второго регистровмикрокоманд соединены соответственно с единичными входами первого ивторого триггеров окончания параллельного участка, единичный выходпервого триггера окончания параллельного участка соединен с первымвходом одиннадцатого элемента И ис вторым входом второго элемента ИНЕ, нулевой выход первого триггера 30864окончания параллельного участка соединен с вторым входом восьмого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, нулевой выход второго триггера окончания параллельного участка соединен с вторым входом десятого элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ, единичный выход второго триггера окончания параллельного участка соединен с вторыми входами одиннадцатого элемента И и первого элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, выход одиннадцатого элемента И соединен с входом первого одновибратора и с вторыми входами четвертого и пятого элементов И, выход одновибратора соединен с входом первого элемента задержки, выход которого соединен с нулевЫми входами триггера начала параллельного участка и первого и второго триггеров окончания параллельного участка, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, группа выходов которого является группой выходов микроопераций устройства, выход конца работы группы выходов блока элементов ИЛИ соединен с вторым входом шестого элемента ИЛИ и с вторым входом девятого элемента И, выход которого соединен с вторым входом группы выходов ошибки устройства, группа выходов адреса первого регистра микрокоманд соединена с первой группой входов схемы сравнения адресов, с первой группой входов схемы сравнения адресов, с первой группой информационных входов первого коммутатора адреса и первой и второй группами информационных входов второго коммутатора адреса, выходы первого и второгокоммутаторов адреса соединены соответственно с вторыми входами первого и второго формирователей адреса микрокоманд, группа выходов адреса второго регистра микрокоманд соедине" на с второй группой входов, схемы сравнения адресов и второй .группой информационных входов первого коммутатора адреса и третьей группой информационных входов второго коммутатора адреса, выходы модифицируемыкразрядов адреса первого н второго регистров микрокоманд соединены с третьими входами первого и второго формирователей адреса микрокоманд соответственно, выходы которых сое-динены с вторыми информационными входами первого и второго регистров адреса, выходы первого и второго регистров адреса соединены соответственно с адресными входами первого и второго блоков памяти, выходы которых соединены с информационными входами первого и второго регистров микрокоманд соответственно, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности и оперативности контроля устройства, в него введены первый и второй коммутаторы операционных частей, дешифратор, счетчик, первый и второй триггеры ошибок, первый, второй, третий и .четвертый блоки элементов И, второй и третий элементы"задержки, второй одновибратор, седьмой и восьмой элементы ИЛИ, третий элемент И-НЕ, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый и семнадцатый элементы И, причем выход первого элемента И соединен с первым входом двенадцатого элемента И, с входом второго элемента задержки и с входом второго одновибратора, выход которого соединен с установочными входами первого и второго регистров микрокоманд, выход второго элемента задержки соединен с первым входом тринадцатого элемента И, второй вход которого соединен с выходом одиннадцатого элемента И, выходтринадцатого элемента И соединен с единичным входом триггера управления синхронизацией, единичный выход триггера начала параллельного участка соединен с вторым входом двенадцатого элемента И, выход которого соединен со счетным входом счетчика, выходы счетчика соединены с входами дешифратора, выходы дешифратора соединены с соответствующими управляю,щими входами первого и второго коммутаторов операционных частей, выходы которых соединены с первыми входами первой и второй схем сравнения операционных частей соответственно, выход логических условий первого регистра микрокоманд соединен с первымн входами первого и второго блоков элементов И, выход первого блока элементов И соединен с первым инфор- мационным входом первого коммутатора адреса, первым и вторым информационными входами второго коммутатора адреса, выход второго. блока элементов И соединен с вторым входом второй схемы сравнения операционных частей, выход неравенства которой соединен с первым входом четырнадцатого элемента И, выход логических условий второго регистра микрокоманд соединен с первыми входами третьего и четвертого блоков элементов И, выход третьего блока элементов И соединен с вторым входом первой схемы сравнения операционных частей, выход которой соединен с первым входом пятнадцатого элемента И, выход четвертого блока элементов И соединен со вторым и третьим информационными входами первого коммутатора. адреса, третьим информационным входом второго коммутатора адреса, выход начала параллельного участка первого регистра микрокоманд соединен с третьим инверсным управляющим входом первого коммутатора адреса, выход начала параллельного участка второго регистра микрокоманд соединен с третьим инверсным управляющим входом второго коммутатора адреса, нулевой выход триггера начала параллельного участка соединен с первыми входамн шестнадцатого и семнадцатого элементов И, с вторыми входами первого и четвертого блоков элементов И ис входом третьего элемента задержки,выход которого соединен с третьими и четвертыми прямыми управляющими входами первого и второго коммутаторов адреса, единичный выход первого триггера окончания параллельного участка соединен с первым входом третьего элемекта И-НЕ и с вторым входом шестнадцатого элемента И, выход которого соединен с третьим выходом группы выходов устройства, единичный выход второго триггера окончания параллельного участка соединен с вторым входом третьего элемента И-НЕ и с вторым входом семнадцатого элемента И, выход которого соединен с четвертйм выходом груп.пы выходов устройства, выход третьего элемента И-НЕ соединен с вторье входом четырнадцатого и пятнадцатого элементов И, выходы которых соединены с единичными входами первого113086 ч и второго триггеров ошибок соответственно, единичные выходы первого и второго триггеров ошибок соедине-. ны соответственно с первым и вторым входами седьмого элемента ИЛИ, выэлемента ИЛИ, второй вход которогосоединен с выходом второго элемента И-НЕ, выход восьмого элемента ИЛИсоединен с вторым входом седьмогоэлемента И, выход двенадцатого элемента И соединен с установочным вхоход которого соединен с третьим входом счетчика, единичный выход тригдом шестого элемента ИЛИ, с пятым выходом группы выходов ошибок устрой- гера начала параллельного участкаства, выход первого одновибратора соединен с вторыми входами второго и третьего блоков элементов И. соединен с первым входом восьмого Изобретение относится к цифровойвычислительной технике и может бытьиспользовано при разработке устройствуправления параллельными процессамивычислительных и управляющих систем. 5Известны микропрограммные устройства управления, содержащие первыйи второй блоки памяти микрокоманд,регистры микрокоманд и адреса, Формирователи адреса, триггеры, элементы И 1 и 2.Недостатками указанных устройствявляются низкая производительностьи узкая область применения, обусловленные их невозможностью управленияпараллельными процессами, а такженизкая достоверность Функционирования, обусловленная отсутствиемсредств контроля адресов при выходеиз параллельного режима.20Известно микропрограммное устройство управления, содержащее первыйи второй блоки памяти микрокоманд,первый и второй регистры адреса,первый и второй коммутаторы, блоксинхронизации, первый и второй триггеры управления, элементы Ии ИЛИ 3.Недостатками данного устройстваявляется низкая производительность, ЗОобусловленная отсутствием технических средств для управления параллельными процессами и перетактовкойустройства при последовательном выполнении двух четных (нечетньгх) мик,рокоманд, а также низкая достоверность функционирования,Наиболее близким к изобретениюпо технической сущности и достигаемому положительному эффекту являет ся микропрограммное устройствоуправления, содержащее первый ивторой блоки памяти микрокоманд, пер.вый и второй регистры адреса, первыйи второй регистры микрокоманд, схему сравнения, первый - четвертыйкоммутаторы, Формирователь тактовыхимпульсов, первый и второй Формирователи адреса, первый-пятый триггерыуправления, первый-восьмой элементы И, перый-седьмой элементы ИЛИ,первый и второй элементы И-НЕ, одновибратор, блок элементов ИЛИ, причемвход логических условий устройствасоединен с первыми информационнымивходами первого и второго Формирователей адреса, выходы которых соединены с первыми входами соответственнопервого и второго регистров адреса,вход кода операции устройства соединен со вторыми информационными входами первого и второго регистров адреса, выходы которых соединены с информационными входами соответственнопервого и второго блоков памяти микрокоманд, выходы первого и второгоэлементов И соединены с управляющимивходами соответственно первого ивторого блоков памяти микрокоманд,выходы которых соединены с входамисоответственно первого и второгорегистров микрокоманд, первый управляющие выходы первого и второгорегистров микрокоманд соединенныхс единичными входами соответственнопервого и второго триггеров управления, выходы микроопераций первогои второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ,311 Овыход которого является выходом микроопераций устройства, выход адреса.первого регистра микрокоманд соединен с первыми информационными,входами первого,и второго коммутаторов,выход адреса второго регистра микрокоманд соединен с вторыми информационными входами первого и второго коммутаторов, выходы которых соединеныс вторыми информационными входами10соответственно первого и второгоформирователей адреса, вход кода операции устройства через первый элемент ИЛИ соединен с единичным входом.третьего триггера управления, единичный выход которого соединен с входомформирователя тактовых импульсов,первый выход формирователя тактовыхимпульсов соединен с нулевыми входами триггеров полей микроопераций пер- р 0вого и второго регистров микрокоманд и с первыми информационнымивходами третьего и четвертого коммутаторов, выходы которых соединеныс первыми входами соответственно 25первого и второго элементов И,второй и третий выходы формирователятактовых импульсов соединены соответственно с вторыми и третьими информационными входами третьегоичетвертого коммутаторов, единичныйвыход четвертого триггера управления соединен с первыми управляющимивходами третьего, четвертого коммутаторов, первыми входами третьего,35четвертого, пятого элементов И и первого и второго элементов И-НЕ, выходы которых соединены с вторыми входами соответственно первого и второгоэлементов И, второй управляющий выход первого регистра микрокомандсоединен с первыми входами второгои третьего элементов ИЛИ, выход которого соединен с первым управляющимвходом первого коммутатора, второйуправляющий выход второго регистрамикрокоманд соединен с первым входом четвертого и вторым входом второго элементов ИЛИ, выход которогосоединен с Т-входом пятого триггерауправления, единичный выход пятоготриггера управления соединен с вторыми управляющими входами. третьегои четвертого коммутаторов, а нулевойвыход - с третьими управляющими вхо 55дами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров микрокоманд 864 4 через пятый элемент ИЛИ соединеныс единичным входом четвертого триггера управления, нулевой выход которого соединен с вторым управляющим входом первого коммутатора и первым управляющим входом второго коммутатора, нулевые выходы первого и второготриггеров управления соединены свторыми входами соответственно третьего и пятого элементов И, выходыкоторых соединены с вторыми входамисоответственно третьего и четвертого элементов ИЛИ, выход которогосоединен с вторым управляющим входом второго коммутатора, третьиуправляющие выходы первого и второго регистров микрокоманд соединеныс третьими управляющими входами соответственно первого и второго коммутаторов, единичный выход первоготриггера управления соединен с вторым входом первого элемента И-НЕи первым входом шестого элемента И,единичный выход второго триггерауправления соединен с вторым входом второго элемента И-НЕ и вторым входом шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И, а через одновибратор - с нулевыми входами первого, второго и четвертого триггеров обнуления, выходы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверсный выход которой соединены с вторыми входами соответственно седьмого и восьмого элементов И, выход седьмого элемента И соединен с третьими входами третьего и четвертого элементов ИЛИ, выход восьмого элемента И соединен с первыми входами шестого и седьмого элементов ИЛИ, выходы которых соединены соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выход конца операции блока элементов ИЛИ соединен с вторыми входами шестого элемента ИЛИ и четвертого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ 4,Недостатками известного устройства являются низкая достоверность и оперативность контроля, обусловленные тем, что контроль адресов выхода из параллельного режима осу,ществляется только в конце выполне 113084ния параллельных микроподпрограмм.Во время выполнения параллельныхмикроподпрограмм поля логическихусловий микрокоманд свободны, т.е.существует естественная структурная 5избыточность полей логических условий, которая может быть использована для контроля выполнения параллельных микроподпрограмм не только вовремя окончания параллельных участков, но и в ходе выполнения самихпараллельных микроподпрограмм,В устройстве полностью отсутствует,контроль функции выходов устройства,поскольку проверкой охвачены лишь 15адресные цепи. Кроме того, результатконтроля при выполнении параллельных микроподпрограмм формируетсятолько в конце их реализации, чтосущественно увеличивает время обнаружения ошибки и устранения ее последствий.При выполнении параллельных микроподпрограмм известное устройствоможет перейти в режим зависания 25одного из каналов, вследствие того,что выход другого канала на последовательные мйкроподпрограммы не будетобнаружен. Путем перекрестного задания частей микрокоманд в свободных 30полях логических условий и последующим сравнением кодов частей микрокоманд, записанных в поле логическихусловий одного блока памяти с частьюмикрокоманд другого блока памяти мож-Зно существенно повысить достоверность и оперативность контроля устройства. Данная возможность в известном устройстве не реализована, чтои приводит к низкой достоверностии оперативности контроля.Цель изобретения - повышение достоверности и оперативности контролямикропрограммного устройства управления. 45Поставленная цель достигается тем,что в микропрограммное устройствоуправления, содержащее первый и второй блоки памяти микрокоманд, первыйи второй регистры адреса, первый 50и второй регистры микрокоманд, первый и второй формирователи адресамикрокоманд, первый и второй коммутаторы адреса, первый и второй коммутаторы управления, триггер начала 55параллельного участка, триггер управления синхронизацией, первый и второй триггеры окончания параллельного участка, триггер пуска, схему,сравнения адресов, гвнератор тактовых импульсов, первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, блок элементов ИЛИ, одиннадцать элементов И,первый и второй элементы И-НЕ, первый одновибратор и первый элемент задержки, причем вход кода операции устройства соединен с первыми информационными входами первого и второго регистров адреса и входами первого элемента ИЛИ, выход которого соединен с единичным входом триггера пуска, вход логических условий устройства соединен с первыми входами первого и второго формирователей адреса, выходы которых с,оединены с вторыми информационными входами первого и второго регистров адреса соответственно, выход триггера пуска соединен с первыми входами первого, второго и третьего элементов И, первый, второй и третий выходы генератора тактовых импульсов соединены с вторыми входами соответственно первого, второго и третьего элементов И, выход первого элемента И соединен с первыми управляющими входами первого и второго коммутаторов управления, выход второго элемента И соединен с вторыми управляющими входами первого и второго коммутаторов управления, выход третьего элемента И соединен с третьими управляющими входами первого и второго коммутаторов управления, выход равенства и выход неравенства схемы сравнения адресов соединены с первыми входами соответственно четвертого и пятого элементов И, выход четвертого элемента И соединен с первыми входами второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первым и вторым прямыми и первым инверсным управляющими входами первого коммутатора адреса, выход третьего элемента ИЛИ соединен с первым и вторым прямыми и первым инверсным управляющими входами второго коммутатора адреса, выход поля начала параллельного участка первого регистра микрокоманд соединен с первым входом четвертого элемента ИЛИ и с вторым инверсным управляющим входом второго коммутатора адреса, выход начала параллельного участка второго регистра микрокоманд соединен с вторым входом четвертого элемента ИЛИ и вторым инверсным управляющим входом первого коммутатораадреса, выходы управления синхронизацией первого и второго регистровмикрокоманд соединены соответственно 5с первым и вторым входами пятогоэлемента ИЛИ й с вторыми входамивторого и третьего элементов ИЛИсоответственно, выход пятого элемента ИЛИ соединен со счетным входом 10триггера управления синхронизацией,единичный и нулевой выходы которогосоединены соответственно с первымии вторыми информационными входамипервого и второго коммутаторов управления, выход пятого элемента И соединен с первым выходом группы выходовошибки устройства и с первым входомшестого элемента ИЛИ, выход которогосоединен с нулевым входом триггера .20пуска, выходы второго и первого коммутаторов управления соединены с первыми входами шестого и седьмого элементов И соответственно, выходшестого элемента И соединен с. входами 25синхронизации второго регистра адреса и второго регистра микрокоманд,выход седьмого элемента И соединенс входами синхронизации первого регистра адреса и первого регистра З 0микрокоманд, выход четвертого элемента ИЛИ соединен с единичным входом триггера начала параллельногоучастка, единичный выход которогосоединен с первыми входами восьмого,девятого и десятого элементов И,первого и второго элементов И-НЕи с третьими и шестыми информационными входами первого и второгокоммутаторов управления, выходы конца параллельного участка первогои второго регистров микрокоманд соединены соответственно с единичнымивходами первого и второго триггеровокончания параллельного участка, еди ничный выход первого триггера окончания параллельного участка соединенс первым входом одиннадцатого элемента И и с вторым входом второго элемента И-НЕ, нулевой выход первого 50триггера окончания параллельногоучастка соединен с вторым входомвосьмого элемента И, выход которогосоединен с третьим входом второгоэлемента ИЛИ, нулевой выход второго 55триггера окончания параллельногоучастка соединен с вторым входомдесятого элемента И, выход которого соединен с третьим входом третьегоэлемента ИЛИ, единичный выход второго триггера окончания параллельногоучастка соединен с вторыми входамиодиннадцатого элемента И и первогоэлемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, выход одиннадцатого элемента И соединен с входом первого одновибратора и с вторыми входами четвертого и пятого элементов И, выхододновибратора соединен с входом первого элемента задержки, выход которого соединен с нулевыми входами триггера начала параллельного участка ипервого и второго триггеров окончания параллельного участка, выходымикроопераций первого и второго регистров иикрокоманд соединены соответственнос первым и вторым входами блока элементов ИЛИ, группа выходов которого является группой выходов микроопераций устройства, выходконца работы группы выходов блокаэлементов ИЛИ соединен с вторым входом шестого элемента ИЛИ и с вторымвходом девятого элемента И, выходкоторого соединен с вторым входомгруппы выходов ошибки устройства,группа выходов адреса первого регист.ра микрскоманд соединена с первойгруппой входов схемы сравнения адресов, с первой группой входов схемысравнения адресов, с первой группойинформационных входов первого коммутатора адреса и первой и второй группами информационных входов второгокоммутатора адреса, выходы первогои второго коммутаторов адреса соединены соответственно с вторыми входами первого и второго формирователейадреса микрокоманд, группа выходовадреса второго регистра микрокоманд1 соединена с второй группой входовсхемы сравнения адресов и второйгруппой информационных входов первого коммутатора адреса и третьейгруппой информационных входов второго коммутатора адреса, выходымодифицируемых разрядов адреса первого и второго регистров микрокомандсоединены с третьими входами первого и второго формирователей адресамикрокоманд соответственно, выходыкоторых соединены с вторьяи информационными входами первого и второгорегистров адреса, выходы первогои второго регистров адреса соедине 1130864 10ны соответственно с адресными входами первого и второго блоков памяти,выходы которых соединены с информационными входами первого и второгорегистров микрокоманд соответственно, введены первый и второй коммутаторы операционных частей, дешифратор,счетчик; первый и второй триггерыошибок, первый, второй, третий и четвертый блоки элементов И, второйи третий элементы задержки, второйодновибратор, седьмой и восьмой элементы ИЛИ, третий элемент И-НЕ, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый и сем" 5надцатый элементы И причем выходпервого элемента И соединен .с первымвходом двенадцатого элемента И,с входом второго элемента задержки.и с входом второго одновибратора, 2 Овыход которого соединен с установочными входами первого и второго регистров микрокоманд, выход второгоэлемента задержки соединен с первымвходом тринадцатого элемента И, второй вход которого соединен с выходомодиннадцатого элемента И, выход тринадцатого элемента И соединен с единичным входом триггера управлениясинхронизацией, единичный выход триг- ЗОгера начала параллельного участкасоединен с вторым входом двенадцатогоЪэлемента И, выход которого соединенсо счетным входом счетчика, выходысчетчика соединены с входами дешифра-З 5тора, выходы дешифратора соединеныс соответствующими управляющимивходами первого и второго коммутаторов операционных частей, выходы которых соединены с первыми входами пер Овой и второй схем сравнения операционных частей соответственно, выходлогических условий первого регистрамикрокоманд соединен с первыми входами первого и второго блоков элементов И, выход первого блока элементов И соединен с первым информационным входом первого коммутатора адреса, первым и вторым информационнымивходами второго коммутатора адреса, 5 Овыход второго блока элементов Исоединен с вторым входом второйсхемы сравнения операционных частей, выход неравенства которойсоединен с первым входом четырнадцатого элемента И, выход логическихусловий второго регистра микрокоманд соединен с первыми входами тРетьего и четвертого блоков злемен.тов И, выход третьего блока элементов И соединен с вторым входом первой схемы сравнения операционныхчастей, выход которой соединен с первым входом пятнадцатого элемента И,выход четвертого блока элементов Исоединен с вторым и третьим информационными входами первого коммутатора адреса, третьим информационнымвходом второго коммутатора адреса,выход начала параллельного участкапервого регистра микрокоманд соединен с третьим инверсным управляющимвходом первого коммутатора адреса,выход начала параллельного участкавторого регистра микрокоманд соединен с третьим инверсным управляющимвходом второго коммутатора адреса,нулевой выход триггера начала параллельного участка соединен с первымивходами шестнадцатого и семнадцатого элементов И, с вторыми входамипервого и четвертого блоков элементов И и с входом третьего элементазадержки, выход которого соединенс третьими и четвертыми прямымиуправляющими входами первого и второго коммутаторов адреса, единичныйвыход первого триггера окончанияпараллельного участка соединен с первым входом третьего элемента И-НЕи с вторым входом шестнадцатого элемента И, выход которого соединенс третьим выходом группы выходовустройства, единичный выход второготриггера окончания параллельногоучастка соединен с вторым входом.третьего элемента И-НЕ и с вторымвходом семнадцатого элемента И, выход которого соединен с четвертымвыходом группы выходов устройства,выход третьего элемента И-НЕ соединен с вторым входом четырнадцатогои пятнадцатого элементов И, выходыкоторых соединены с единичными входами первого и второго триггеровошибок соответственно, единичныевыходы первого и второго триггеровошибок соединены соответственнос первым и вторым входами седьмогоэлемента ИЛИ, выход которого соединен с третьим входом шестого элемента ИЛИ, с пятым выходом группы выходов ошибок устройства, выход первогоодновибратора соединен с первым входом восьмого элемента ИЛИ, второйвход которого соединен с выходом вто12 864 1130 1рого элемента И-НЕ, выход восьмого элемента ИЛИ соединен с вторым входом седьмого элемента И, выход двенадцатого элемента И соединен с установочным входом счетчика, единичный 5 выход триггера начала параллельноГо участка соединен с вторыми входами второго и третьего блоков элементов И.1Сущность изобретения состоит в по 10 .вышении достоверности и оперативности контроля на основе использования естественной структурной избыточности полей логических условий при выполнении параллельных участков путем перекрестного задания в свободных полях15 частей микрокоманд параллельных микроподпрограмм.Введение первого-четвертого блоков элементов И, первого и второго коммутаторов операционных частей, первой и второй схем сравнения, второго одновибратора, третьего элемента И-НЕ, четырнадцатого и пятнадцатого элементов И, первого и второго триггеров ошибок, седьмого элемен 25 та ИЛИ и рбусловленных ими связей позволяет осуществить контроль микро- команд, записанных в первом и втором блоках памяти, и выдачу сигнала ошибки при искажении информациии, считы- ЗО ваемой из первого или второго блоков памяти.Введение двенадцатого элемента И, счетчика и дешифратора и обусловленных ими связей позволяет осуществлять 35 выбор частей микрокоманд, записанных в первом и втором блоках памяти.Введение восьмого элемента ИЛИ, тринадцатого элемента И, второго элемента задержки и обусловленных ими 40 связей позволяет осуществить прохождение тактового импульса с выхода первого коммутатора управления на входы синхронизации первого регистра адреса и первого регистра микрокоманд 45 при выходе из параллельного режима, а также осуществлять установку триггера управления синхронизацией в единичное состояние с временем задержки ЗЪ 1, после окончания параллель ных участков.Введение шестнадцатого и семнапцатого элементов И и обусловленных ими связей позволяет формировать сигналы ошибок в параллельном режи ме.Введение третьего элемента задержки и обусловленных им связей позволяет производить блокировкупервого и второго коммутаторов адреса нулевым сигналом при входе в параллельный режим.На фиг. 1 приведена функциональная схема устройства; на фиг, 2функциональная схема первого и второго формирователей адреса; нафиг. 3 - формат микрокоманд, считываемых из блоков памяти; на фиг, 4структурная схема контроля устройства; на фиг, 5 - временная диаграммаработы устройства,Параллельное микропрограммноеустройство управления с контролем(фиг. 1) содержит первый блок 1 памя- .ти микрокоманд (ПЗУ 1), второй блок 2памяти микрокоманд (ПЗУ 2), первыйрегистр 3 адреса, второй регистр 4адреса, первый регистр 5 микрокоманд, содержащий поле 5;1 адреса,поле 5,2 логических условий, поле 5.3 микроопераций, поле 5.4 метки М конца параллельного участкамикропрограммы, поле 5,5 метки Мначала параллельного участка, поле 5.6 метки М 3 управления синхронизацией, поле 5.7 модифицируемогоразряда адреса, второй регистр 6микрокоманд, содержащий поле 6.1 метки М 3 управления синхронизацией,поле 6.2 метки М начала параллельного участка микропрограммы, поле 6,3 метки М 4 конца параллельногоучастка микропрограммы, поле 6.4микроопераций, поле 6.5 логическихусловий, поле 6.6 адреса, поле 6,7модифицируемого разряда адреса, первую схему 7 сравнения операционныхчастей, вторую схему 8 сравненияоперационных частей, схему 9 сравне фния адреса, первый. формирователь 10адреса микрокоманд, второй формирователь 11 адреса мнкрокоманд, первый коммутатор 12 адреса, второйкоммутатор 13 адреса, первый коммутатор 14 управления, второй коммутатор 15 управления, первый коммутатор 16 операционных частей, второйкоммутатор 17 операционных частей,счетчик 18, дешифратор 19, генератор 20 тактовых импульсов, триггер 21управления синхронизацией, первыйтриггер 22 ошибки, второй триггер 23ошибки, первый триггер 24 окончанчяпараллельного участка, триггер 25начала параллельного участка, второй триггер 26 окончания параллель

СмотретьЗаявка

3647727, 30.09.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, НИКОЛЬСКИЙ СЕРГЕЙ БОРИСОВИЧ, КАЛЬЧЕНКО СЕРГЕЙ БОРИСОВИЧ, ЧИГРИН ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/25, G06F 9/22

Метки: микропрограммное

Опубликовано: 23.12.1984

Код ссылки

<a href="https://patents.su/19-1130864-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для сварки неповоротных стыков труб