Процессор цифровой обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

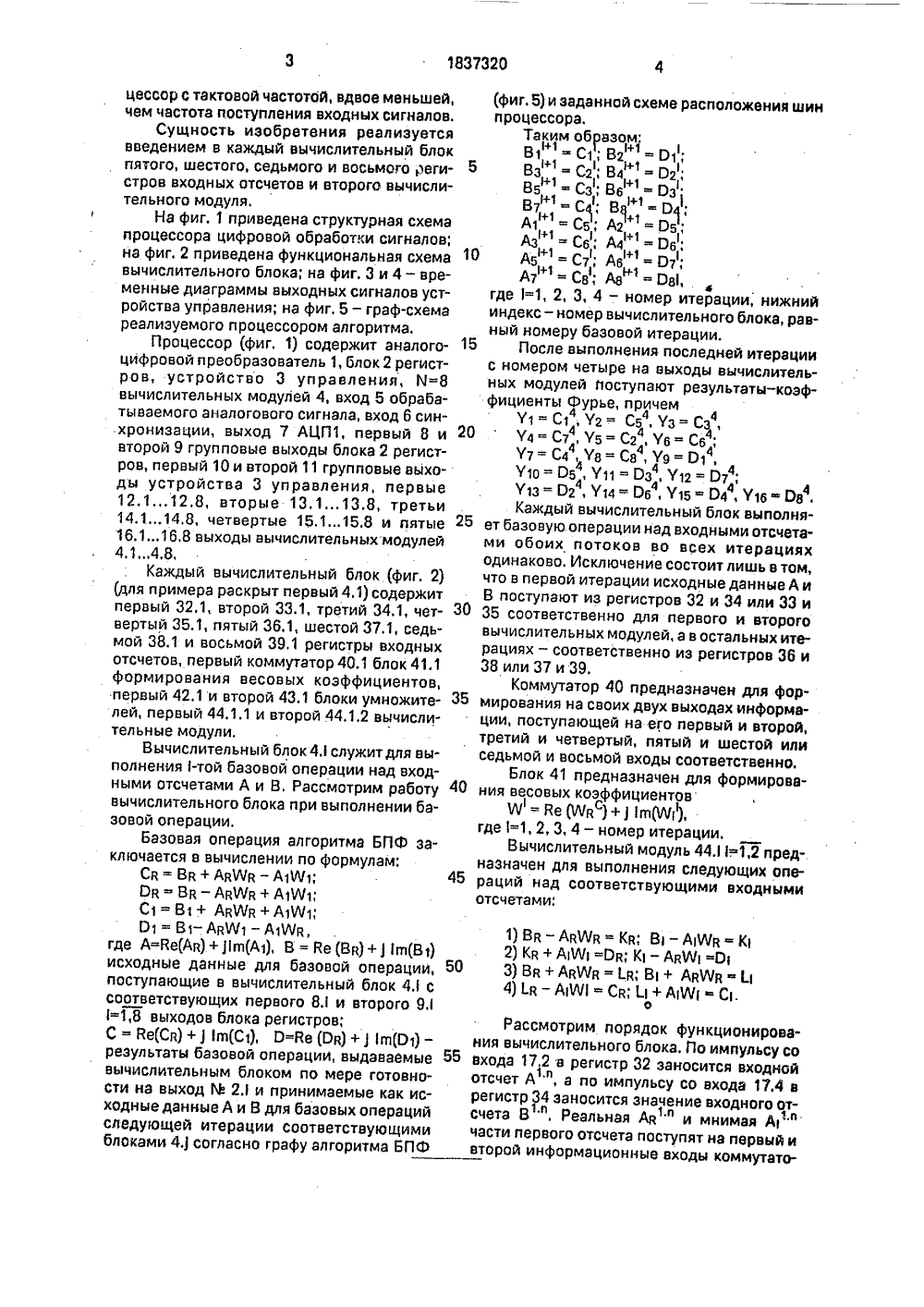

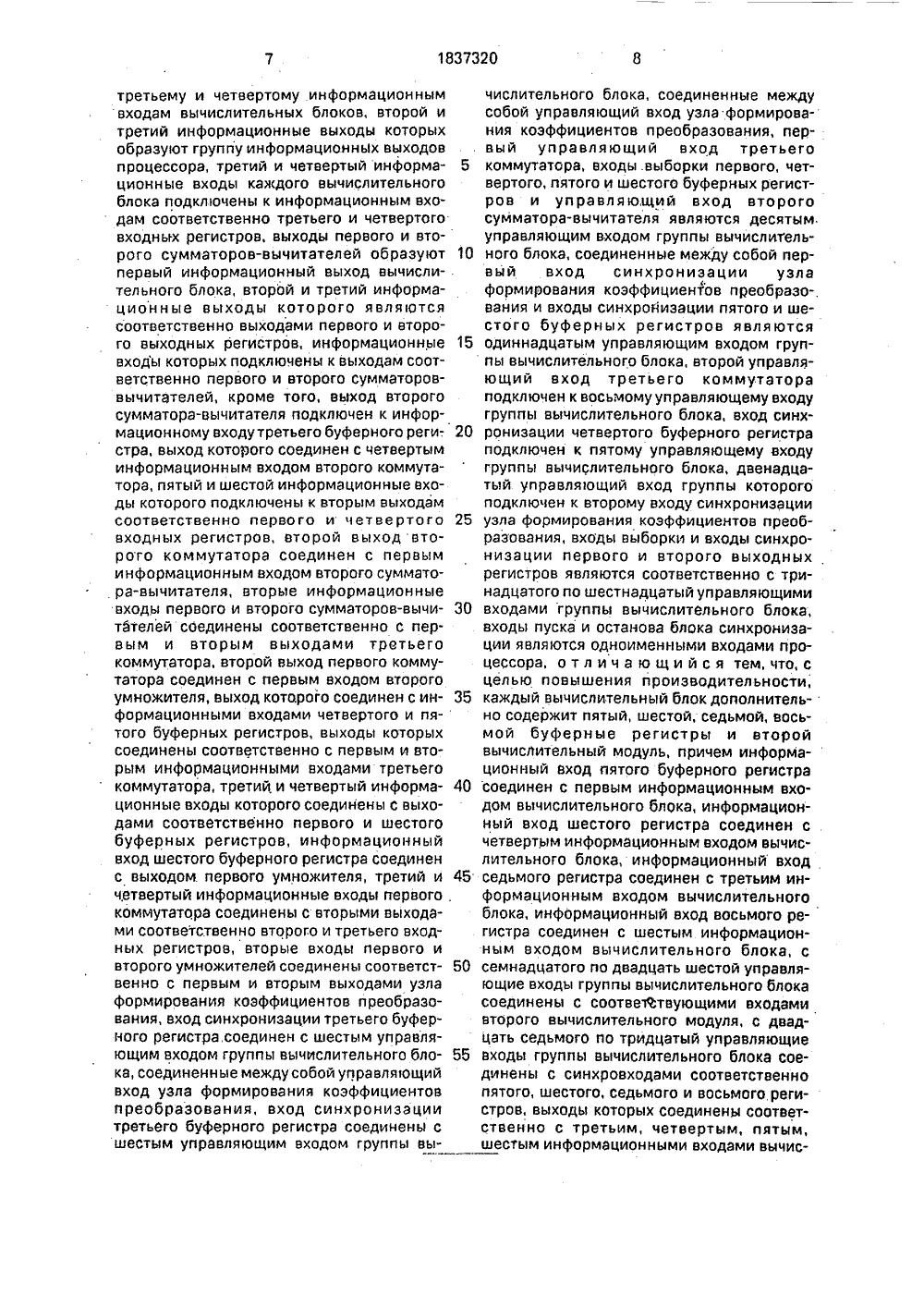

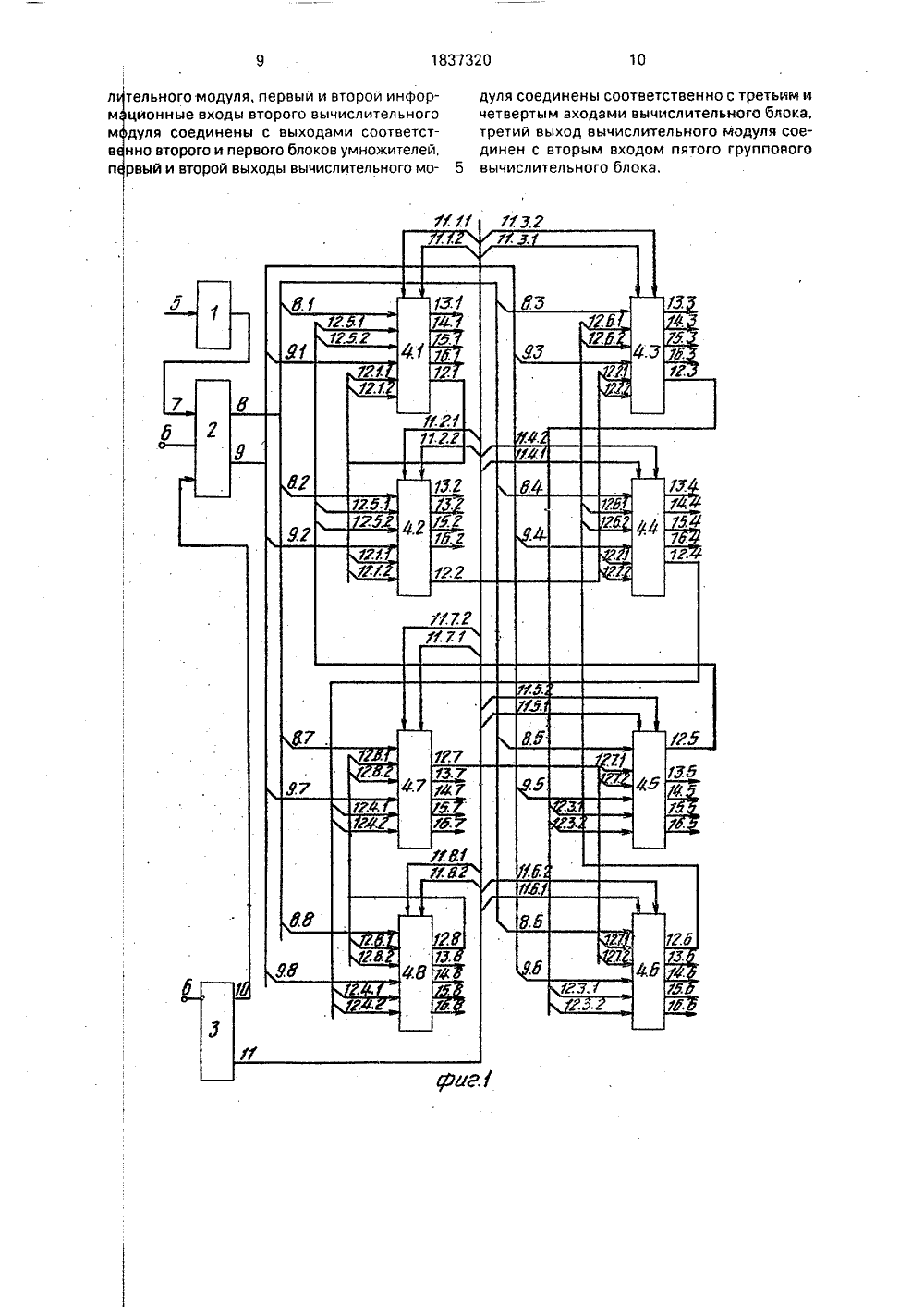

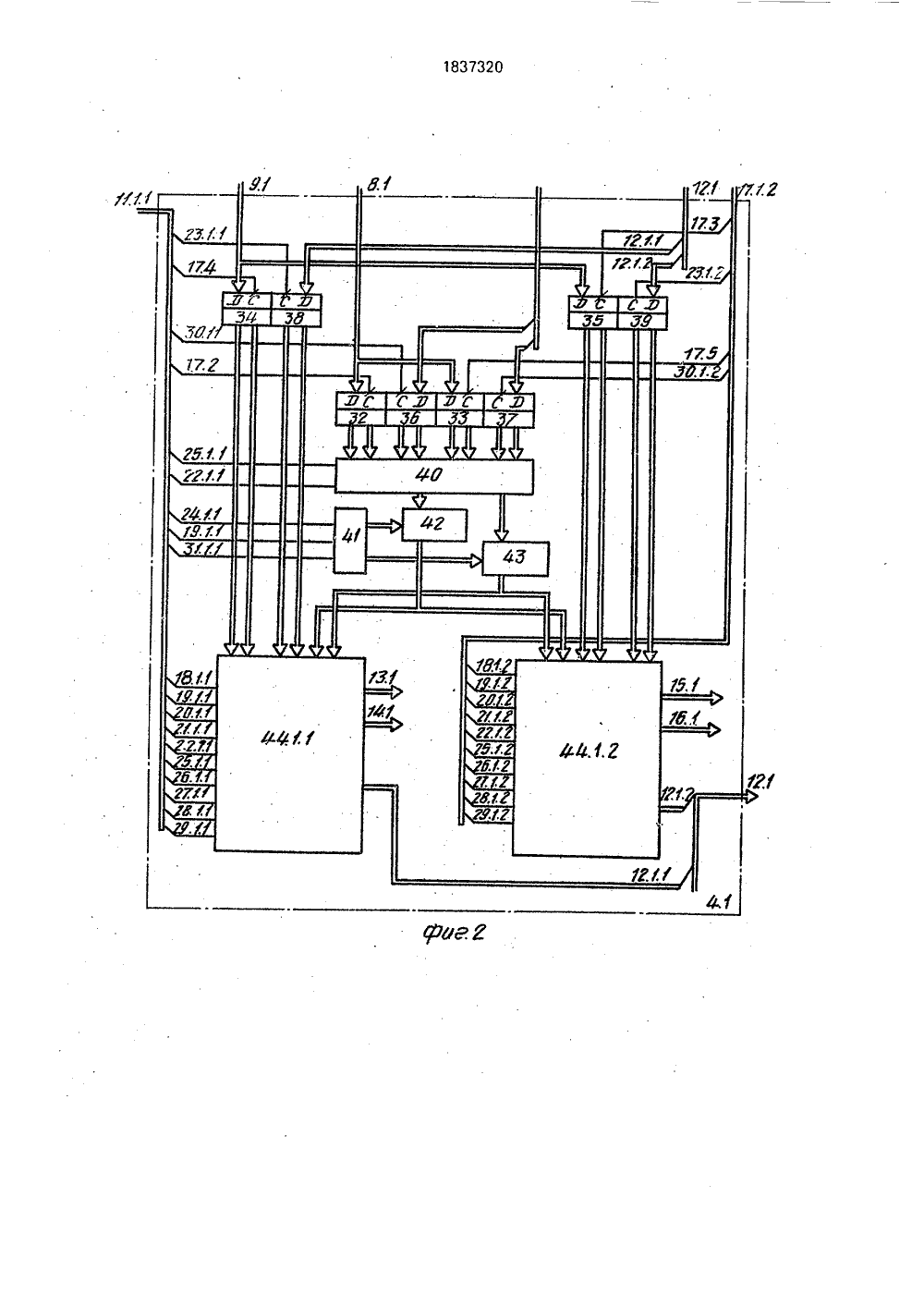

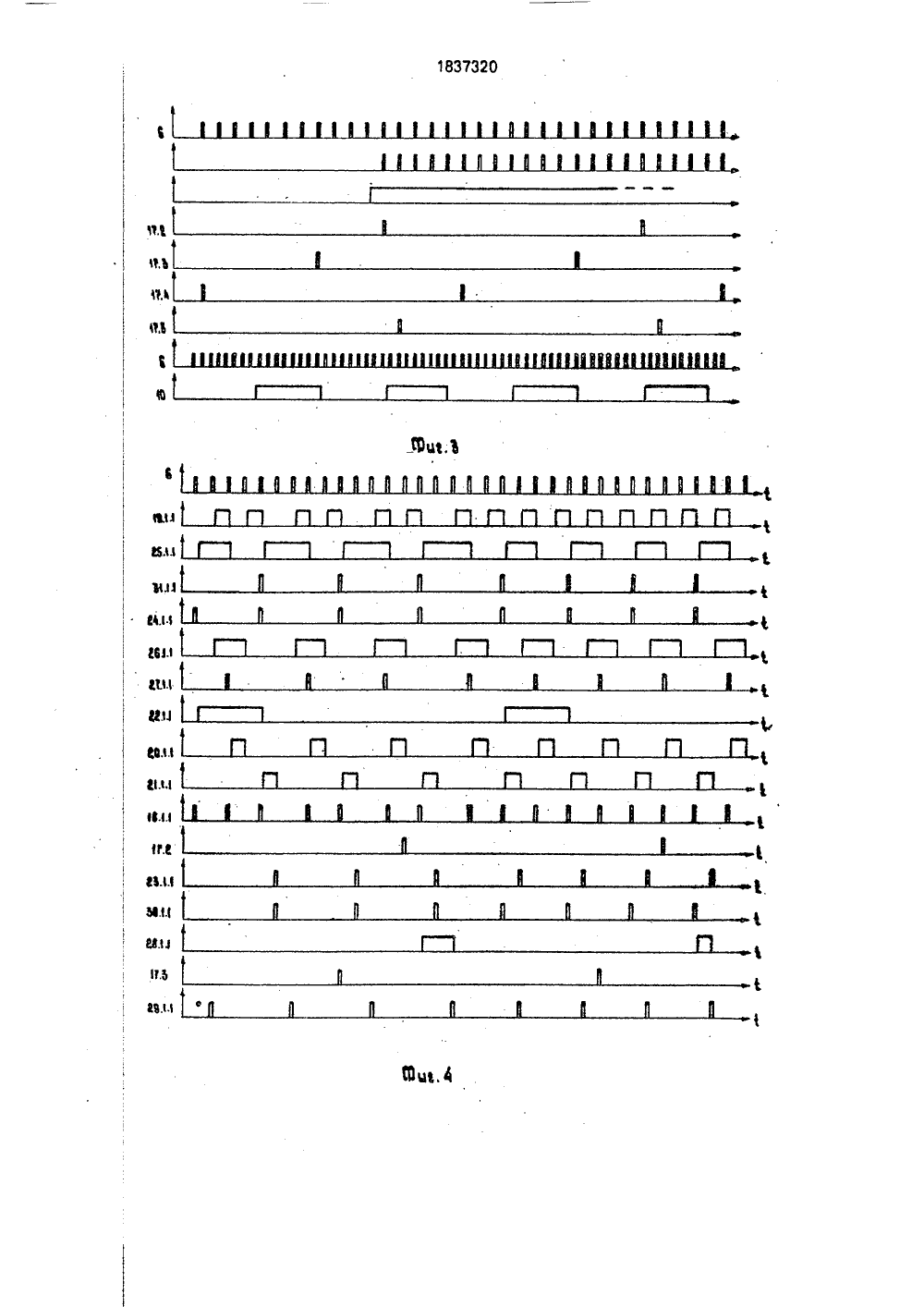

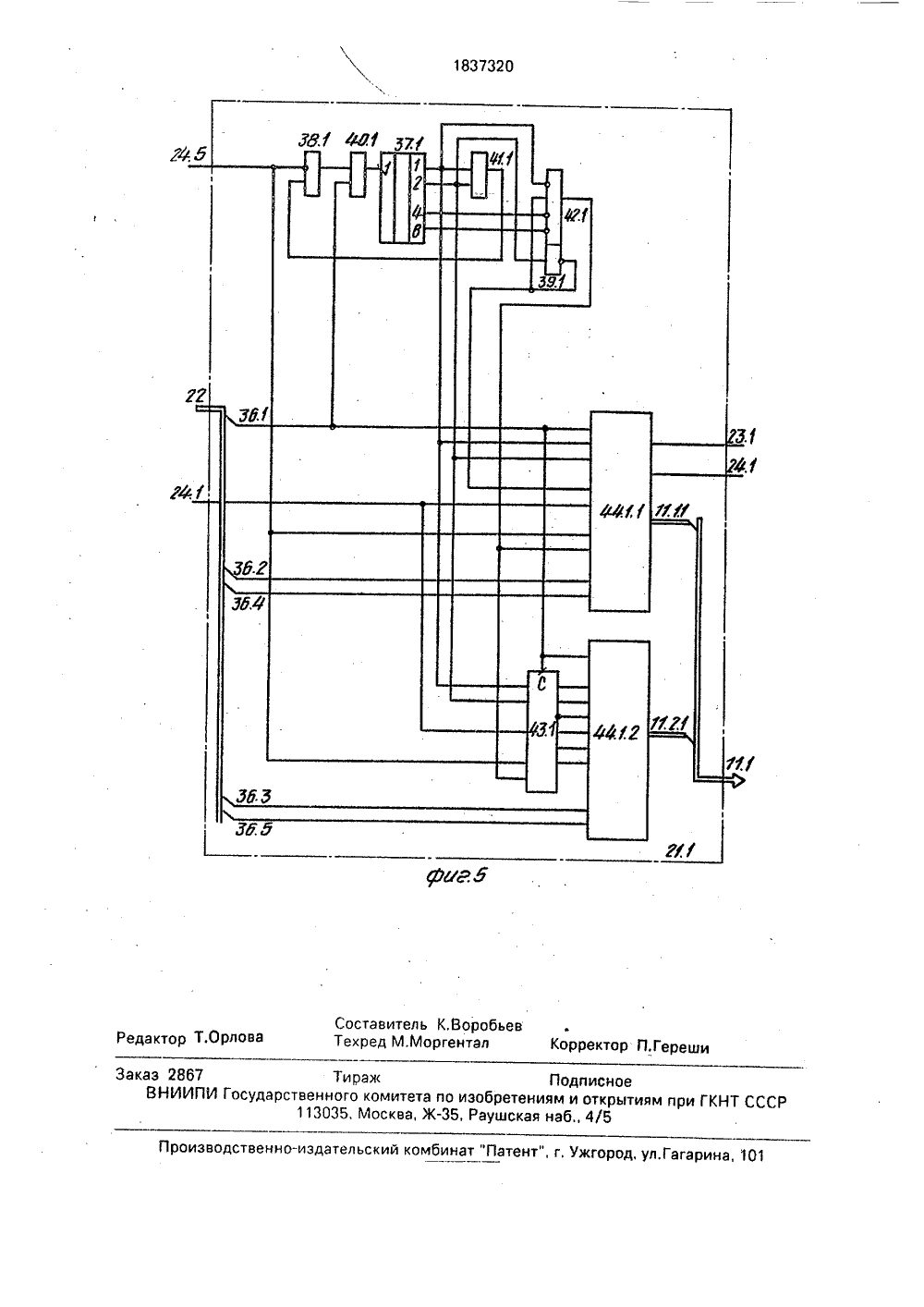

Недостатком 41815953/24 яв твльность, яется повышеоцессора цифсостоит в повыти процессора лов за счет разчетов на два по- параллельной пользовать про) 12.06.90) Конструкторское бюро электроприборороения) ПРОЦЕССОР ЦИФРОВОЙ ОБРАБОТКИГНАЛОВ) Изобретение относится к вычислительй технике и предназначено для решениядач цифровой обработки сигналов, вклюющих выполнение алгоритма быстрогоеобразования Фурье (БПФ). Целью изоетения является повышение производильности процессора цифровой обработкигналов за счет разбиения входного потокасчетов на два потока и органиэации ихраллельной обработки, что позволяет исльзовать процессор с тактовой частотой,вое меньшей, чем частота поступленияодных сигналов, При этом время обработгруппы входных отсчетов каждого из поотносится к вычислительедназначено для решения обработки сигналов, вклюение алгоритма быстрого (БПФ),процессора по заявке М яется низкая производи рования, что позволяет предлагаемому процессору цифровой обработки сигналов работать в реальном масштабе времени, Процессор содержит аналого-цифровой преобразователь, блок регистров, устройство управления, Й вычислительных модулей, вход обрабатываемого аналогового сигнала, вход синхронизации, выход аналогоцифрового преобразователя, первый и второй групповые выходы блока регистров, первый и второй групповые выходы устройства управления, первые, вторые, третьи, четвертые и пятые выходы вычислительных модулей и соответствующие связи. Каждый вычислительный блок содержит первый - восьмой регистры входных отсчетов, коммутатор, блок формирования весовых коэффициентов, первый и второй блоки умножителей, первый и второй вычислительные модули и соответствующие связи. Новым в процессоре цифровой обработки сигналов является введение в каждый вычислительный блок пятого, шестого, седьмого и восьмого регистров входных отсчетов, второго вычислительного модуля и обусловленных ими связей. 5 ил,Целью изобретения явлние производительности ировой обработки сигналов.Сущность изобретенияшении производительносцифровой обработки сигнабиения входного потока отстока и организации ихобработки, что позволяет исцессор с тактовой частотой, вдвое меньшей, чем частота поступления входных сигналов.Сущность изобретения реализуется введением в каждый вычислительный блок пятого, шестого, седьмого и восьмого регистров входных отсчетов и второго вычислительногоо модуля.На фиг. 1 приведена структурная схема процессора цифровой обработки сигналов, на фиг. 2 приведена функциональная схема вычислительного блока; на фиг. 3 и 4 - временные диаграммы выходных сигналов устройства управления; на фиг. 5 - граф-схема реализуемого процессором алгоритма.Процессор (фиг, 1) содержит аналогоцифровой преобразователь 1, блок 2 регистров, устройство 3 управления, И=8 вычислительных модулей 4, вход 5 обрабатываемого аналогового сигнала, вход 6 синхронизации, выход 7 АЦП 1, первый 8 и второй 9 групповые выходы блока 2 регистров, первый 10 и второй 11 групповые выходы устройства 3 управления, первые 12.112,8, вторые 13.113.8, третьи 14.1.14.8, четвертые 15.115.8 и пятые 16.116.8 выходы вычислительных модулей 4.14.8,Каждый вычислительный блок (фиг, 2) (для примера раскрыт первый 4.1) содержит первый 32.1, второй 33.1, третий 34,1, четвертый 35.1, пятый 36.1, шестой 37,1, седьмой 38.1 и восьмой 39.1 регистры входных отсчетов, первый коммутатор 40,1 блок 41 1 формирования весовых коэффициентов, первый 42.1 и второй 43.1 блоки умножителей, первый 44.1,1 и второй 44.1.2 вычислительные модули.Вычислительный блок 4. служитдля выполнения -той базовой операции над входными отсчетами А и В, Рассмотрим работу вычислительного блока при выполнении базовой операции.Базовая операция алгоритма БПФ заключается в вычислении по формулам:Сй = Вй + ДВЮВ - А 1 О/1;Ов- Вв-двщ+ АЮ:С 1= В 1+ АВЮВ+ А 1 В/1;О 1 = В 1- АВИ 1 - А 1 ЮВ,где А=Ве(дв)+)в(А 1), В = Ве(ВВ)+Ъ(В 1) исходные данные для базовой операции, поступающие в вычислительный блок 4. с соответствующих первого 8и второго 9. =1,8 выходов блока регистров;С - Ве(СВ)+) а(С 1), О=Ве(ОВ)+) п 1(01) - результаты базовой операций, выдаваемые вычислительным блоком по мере готовности на выход Ь 2. и принимаемые как исходные данные А и В для базовых операций следующей итерации соответствующими блоками 4,) согласно графу алгоритма БПФ(фиг. 5) и заданной схеме расположения шинпроцессора.Таким обоазом:В 1 С 1; В 2 =015 Вз С 2; В 4 = 02,А 1 =С 5; А 2 =05;Аз С 6 А 4 06,10 А 5 = С 7; А 6 07д 7" = С 6; да+1 = оагде =1, 2, 3, 4 - номер итерации, нижнийиндекс - номер вычислительного блока, равный номеру базовой итерации.15 После выполнения последней итерациис номером четыре на выходы вычислительных модулей поступают результаты-коэффициенты Фурье, причемУ 1 = С 1, У 2 = С 5, Уз = Сз,У 4= С 7, У 5= С 2, У 6= С 6;У 7 = С 4, У 6 = С 8, У 9 = 01,У 10 = 05, У 11 = 03, У 12 = 07;У 1 з = 02, У 14 = 06, У 15 04, У 16 06Каждый вычислительный блок выполня 25 ет базовую операции над входными отсчетами обоих потоков во всех итерацияходинаково. Исключение состоит лишь в том,что в первой итерации исходные данные А иВ поступают из регистров 32 и 34 или 33 и30 35 соответственно для первого и второговычислительных модулей, а в остальных итерациях - соответственно из регистров 36 и38 или 37 и 39.Коммутатор 40 предназначен для фор 35 мирования на своих двух выходах информации, поступающей на его первый и второй,третий и четвертый, пятый и шестой илиседьмой и восьмой входы соответственно.Блок 41 предназначен для формирова 40 ния весовых коэффициентовЧЧ = Ве 0 Ов)+) выгде =1, 2, 3, 4 - номер итерации.Вычислительный модуль 44. -.1,2 предназначен для выполнения следующих опе 45 раций над соответствующими входнымиотсчетами: 1) Вр - АВЩ = Кв; В - АИ/в - К г) Кй+ АВ =Ов; К - Авщ -О50 3) Вв+АВМ/в .в; В+ АВАЕВ-Ь4) .в - АИ/ Св; .+ АЮ С.оРассмотрим порядок функционирования вычислительного блока. По импульсу со 55 входа 17,2 в регистр 32 заносится входнойотсчет А , а по импульсу со входа 17.4 в1.прегистр 34 заносится значение входного отсчета В. Реальная АВ 1" и мнимая А 1"1.пчасти первого отсчета поступят на первый и второй информационные входц коммутато 18373205 10 15 20 30 35 40 50 55 Р в Р м 3 в В с в а г в П н и Р н и к В т и 2 Р о в с г е в м ч п К Р м В л и д е и а ю ч и в о ф н я б ч т и в 40, реальная Вв " и мнимая В " части орого отсчета поступят на первый и втой входы первого 44.1 вычислительного дуля. По импульсу со входа 17.5 в регистр заносится отсчет А ", а по импульсу со оа 36.3 в регистр 35 заносится отсчет. Реальная Ая и и мнимая Ачаи отсчета поступят на пятый и шестой оды коммутатора 84 соответственно, ре 1.п+1 1.п+1 ьная Вя " и мнимая части В " второ- отсчета поступят на первый и второй оды второго 44.2 вычислительного блока, импульсу на вхоце 30.1 в регистр 36 заСИтСя ЭНаЧЕНИЕ А+1 и (ГдЕ 1=1, 2, 3 - НОМЕР ерации), а по импульс со входа 23,1 в гистре 38 заносится В п(1=1,2,3). Реальн1+1,п 1+1.пя Ави мнимая Ачасти отсчета ступают на третий и четвертый входы ммутатора 40, а реальная Вв " и мнимая" части второго отсчета поступают на етий и четвертый информационные входы рвого вычислительного 44.1 модуля. По ПУЛЬСУ СО ВХОда 30.2 ОТСЧЕТ А 1+1 и 1 эаНО- тся в регистр 37, а по импульсу со входа ,2 отсчет В+ " заносится в регистр 39.+1 и+1 +1.п+1 альная Аяи мнимая А 1части счета поступают на седьмой и восьмой оды коммтато 1 оа 40, а реальная Вя нимая В " части второго отсчета поупают на третий и четвертый входы второ.2 вычислительного модуля, По иничному сигналу на входе 25.1 на перм и втором выходах коммутатора 40 фо 1 оруется реальная Ав " и мнимая А сти входного отсчета, поступающие на рвые входы первого 42 и второго 43 блов умножителей соответственно, На втох их входах формируются реальная Юв и имая Я 1 части весового коэффициента, результате на выходе первого умножитеформируется проиэвед 1 ение Ав "Юр 1, а выходе второго А "ЧЧр; Во втором такте рвый умножитель 42 формирует произвение Ак "И 1, а второй- А "Ю 1 . В третьтакте на первые вхо 1 ды умножителей ступают Ав " и А " соответственно, а вторые Юн; по которым они сфо 1 оми 1 оупроизведение Ав " О/в и А 1 " Ив, в твертом такте умножители формируют оизведения Ая " И и А " Ив для орого вычислительного модуля 44,2 инаково, Вычислительные модули нкционируют со сдвижкой во времена 2 такта. В последующих итераципорядок работы вычислительного ока не изменяется, только в этом слуе входные отсчеты на входы умножилей поступают из регистров 36, 37, 38 39, куда заносятся по импульсам со одов 30.1, 30,2, 23.1, 23.2,Формула изобретения Процессор цифровой обработки сигналов, содержащий й вычислительных блоков (где й - размерность преобразования), блок регистров и блок синхронизации, й групп выходов которого соединены с группами управляющих входов соответствующих Й вычислительных блоков, первый информационный вход К-го (К=1, 1 ч/1) вычислительного блока соединен с первыми информационными входами 2 К-го и (2 К)- го вычислительных блоков, первый информационный выход М-го (М=М/2+1,й) вычислительного блока соединен с вторыми информационными входами (2 М - И/2)-го и (2 М - 1 ч/2+1)-го вычислительных блоков, причем каждый вычислительный блок содержит узел формирования коэффициентов, четыре входных регистра, три коммутатора, два умножителя, два сумматора-вычитателя, два выходных регистра и шесть буферных регистров, причем информационные входы пе рвого и второго входных регистров являются соответственно первым и вторым информационными входами вычислительного блока,первые выходы второго и третьего входных регистров соединены соответственно с первым и вторым информационными входами первого коммутатора, первый выход которого соединен с первым входом первогоумнажителя, выход которого соединен с информационным входом первого буфер 1 ого регистра, первые выходы первого и четвертого входных регистров соединены соответственно с первым и вторым информационными входами второго коммутатора, первый выход которого соединен с первым информационным входом первого сумматора-вычитателя, выход которого соединен с информационным входом второго буферного регистра, выход которого соединен с третьим информационным входом второго коммутатора, входы синхронизации с первого по четвертый входных регистров, первого и второго буферных регистров,соединенные между собой управляющий вход первого коммутатора и первый управляющий вход второго коммутатора, второй управляющий вход второго коммутатора и управляющий вход первого сумматора-вычитателя являются соответственно с первого по девятый управляющими входами группы вычислительного блока, информационный вход блока регистров подключен к информационному входу процессора, первый и второй входы синхронизации блока регистров подключены соответственно к первому и второму выходам блока синхронизации, первый и второй выходы блока регистров подключены соответственно квходных регистров, выходы первого и второго сумматоров-вычитателей образуют 10 15 сумматора-вычитателя подключен к информационному входу третьего буферного реги-. 20стра, выход которого соединен с четвертым 30 умножителя, выход котарого соединен с информационными входами четвертого и пя 40 45 третьему и четвертому информационным входам вычислительных блоков, второй и третий информационные выходы которых образуют группу информационных выходов процессора, третий и четвертый информационные входы каждого вычислительного блока подключены к информационным входам соответственно третьего и четвертого первый информационный выход вычислительного блока, второй и третий информационные выходы которого являются соответственно выходами первого и второго выходных регистров, информационные входы которых подключены к выходам соответственно первого и второго сумматороввычитателей, кроме того, выход второго информационным входом второго коммутатора, пятый и шестой информационные входы которого подключены к вторым выходам соответственно первого и четвертого входных регистров, второй выход второго коммутатора соединен с первым информационным входом второго сумматора-вычитателя, вторые информационные входы первого и второго сумматоров-вычитателей сОединены соответственно с первым и вторым выходами третьего коммутатора, второй выход первого коммутатора соединен с первым входом второго того буферных регистров, выходы которых соединены соответственно с первым и вторым информационными входами третьего коммутатора, третий и четвертый информационные входы которого соединены с выходами соответственно первого и шестого буферных регистров, информационный вход шестого буферного регистра соединен с выходом. первого умножителя, третий и четвертый информационные входы первого коммутатора соединены с вторыми выходами соответственно второго и третьего входных регистров, вторые входы первого и второго умножителей соединены соответственно с первым и вторым выходами узла формирования коэффициентов преобразования, вход синхронизации третьего буферного регистра. соединен с шестым управляющим входом группы вычислительного блока, соединенные между собой управляющий вход узла формирования коэффициентов преобразования, вход синхронизации третьего буферного регистра соединены с шестым управляющим входом группы вы 50 55 числительного блока, соединенные между собой управляющий вход узла формирования коэффициентов преобразования, первый управляющий вход третьего коммутатора, входы. выборки первого, четвертого, пятого и шестого буферных регистров и управляющий вход второго сумматора-вычитателя являются десятым управляющим входом группы вычислительного блока, соединенные между собой первый вход синхронизации узла формирования коэффициентов преобразо-. вания и входы синхронизации пятого и шестого буферных регистров являются одиннадцатым управляющим входом группы вычислительного блока, второй управляющий вход третьего коммутатора подключен к восьмому управляющему входу группы вычислительного блока, вход синхронизации четвертого буферного регистра подключен к пятому управляющему входу группы вычислительного блока, двенадцатый управляющий вход группы которого подключен к второму входу синхронизации узла формирования коэффициентов преобразования, входы выборки и входы синхронизации первого и второго выходных регистров являются соответственно с тринадцатого по шестнадцатый управляющими входами группы вычислительного блока, входы пуска и останова блока синхронизации являются одноименными входами процессора, о т л и ч а ю щ и й с я тем, что, с целью повышения производительности, каждый вычислительный блок дополнительно содержит пятый, шестой, седьмой, восьмой буферные регистры и второй вычислительный модуль, причем информационный вход пятого буферного регистра соединен с первым информационным входом вычислительного блока, информационный вход шестого регистра соединен с четвертым информационным входом вычислительного блока, информационный вход седьмого регистра соединен с третьим информационным входом вычислительного блока, информационный вход восьмого регистра соединен с шестым информационным входом вь 1 числительного блока, с семнадцатого по двадцать шестой управляющие входы группы вычислительного блока соединены с соответствующими входами второго вычислительного модуля, с двадцать седьмого по тридцатый управляющие входы группы вычислительного блока соединены с синхровходами соответственно пятого, шестого, седьмого и восьмого регистров, выходы которых соединены соответственно с третьим, четвертым, пятым, шестым информационными входами вычис 1837320 10м м в и тельногомодуля, первый и второй инфорционные входы второго вычислительного дуля соединены с выходами соответстнно второго и первого блоков умножителей, рвый и второй выходы вычислительного модуля соединены соответственно с третьим и четвертым входами вычислительного блока, третий выход вычислительного модуля соединен с вторым входом пятого группового 5 вычислительного блока.1837320 Составитель К,Воробьевдактор Т,Орлова Техред М.Моргентал Корректор П,Гереш ательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 Производстве Заказ 2867 Тираж ВНИИПИ Государственного комитета по изобрете 113035, Москва, Ж, РаушскаПодписноеям и открытиям при ГКНТ ССнаб., 4/5

СмотретьЗаявка

4838597, 12.06.1990

КОНСТРУКТОРСКОЕ БЮРО ЭЛЕКТРОПРИБОРОСТРОЕНИЯ

БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, НЕСТЕРЕНКО ЮРИЙ ГРИГОРЬЕВИЧ, ВОРОБЬЕВ КОНСТАНТИН ЮРЬЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/332

Метки: процессор, сигналов, цифровой

Опубликовано: 30.08.1993

Код ссылки

<a href="https://patents.su/8-1837320-processor-cifrovojj-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Процессор цифровой обработки сигналов</a>

Предыдущий патент: Устройство обратного дискретного преобразования

Следующий патент: Устройство для перемножения матриц

Случайный патент: Способ обработки пермутита