Микропрограммное устройство для тестового диагностирования и управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

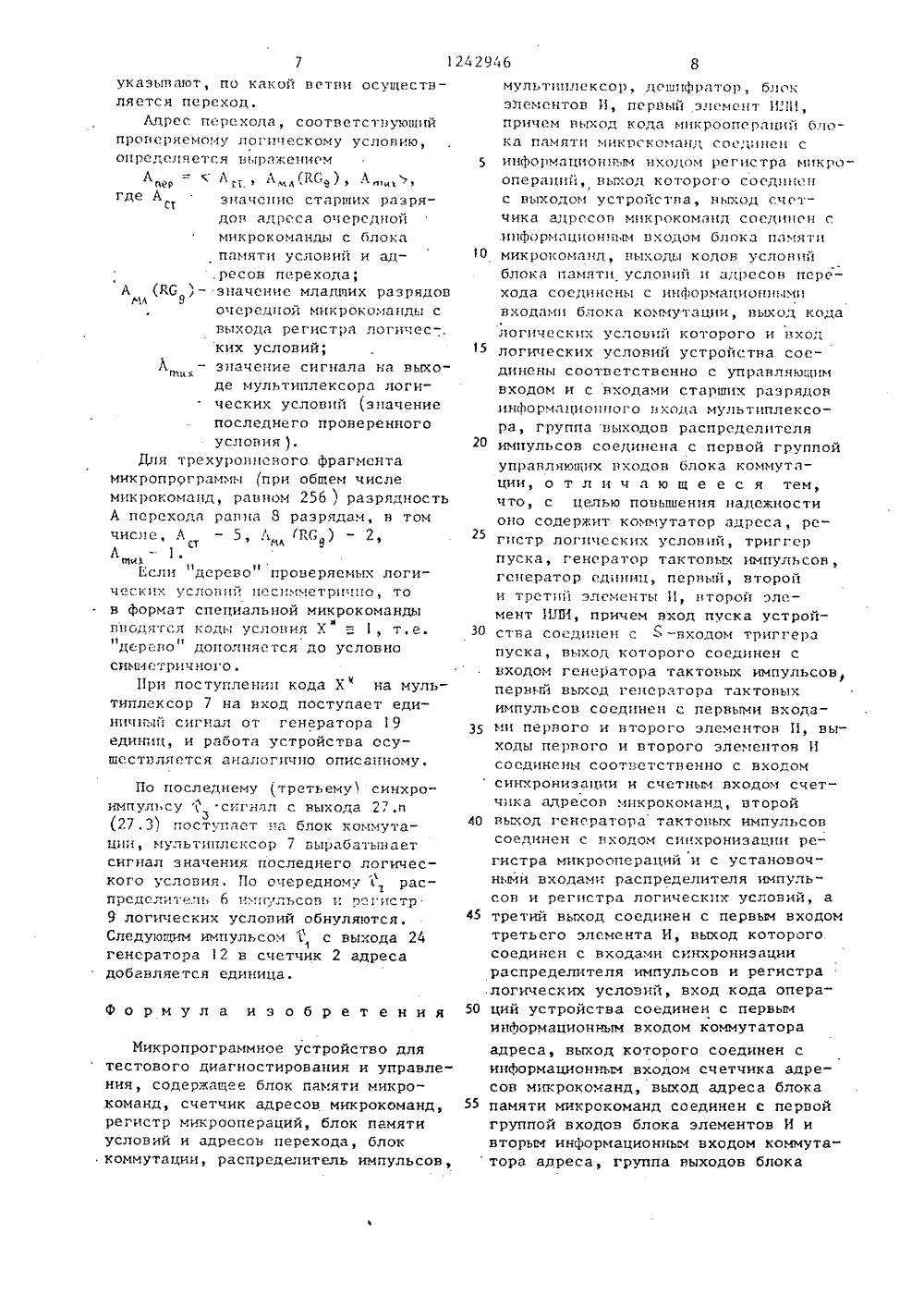

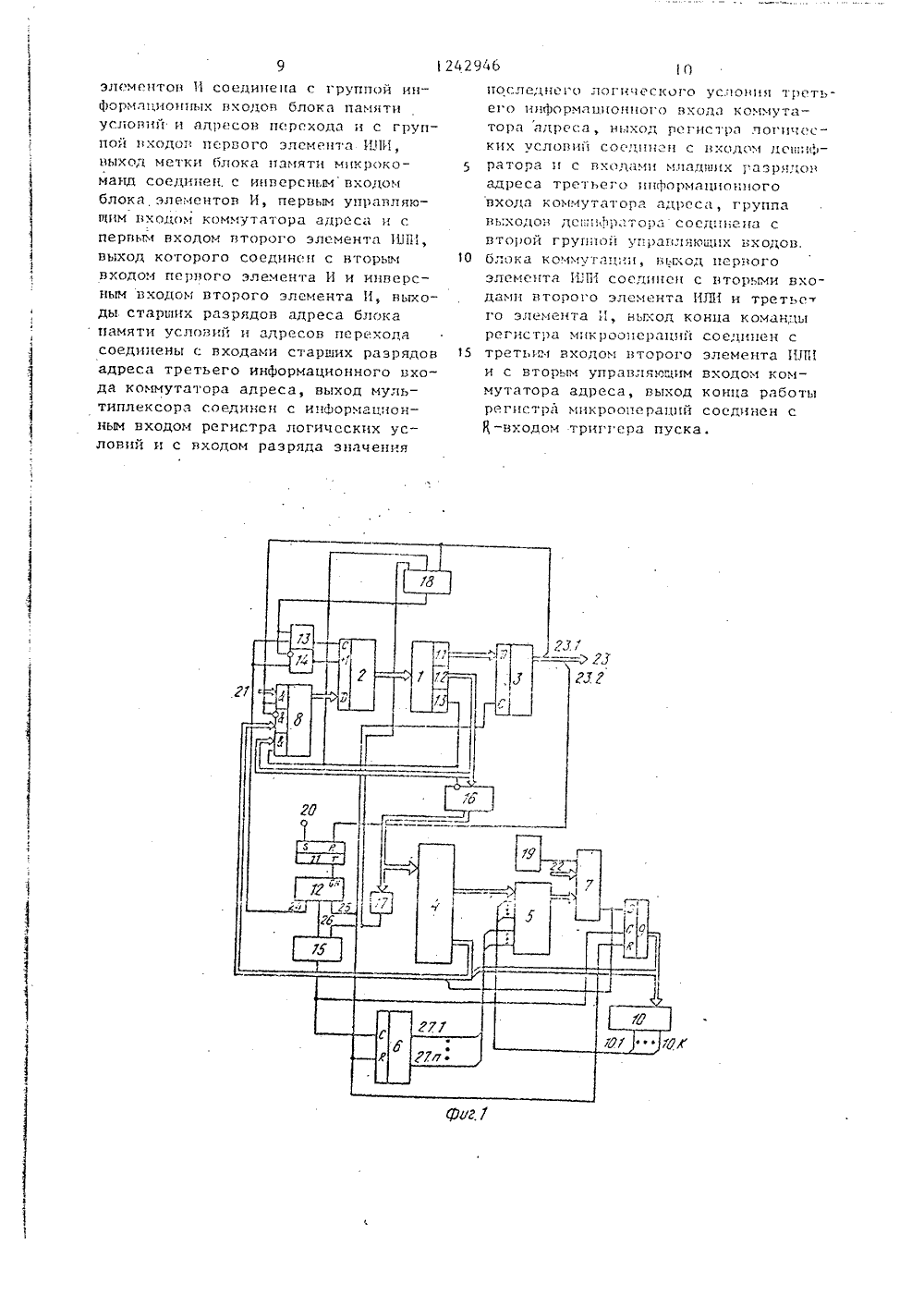

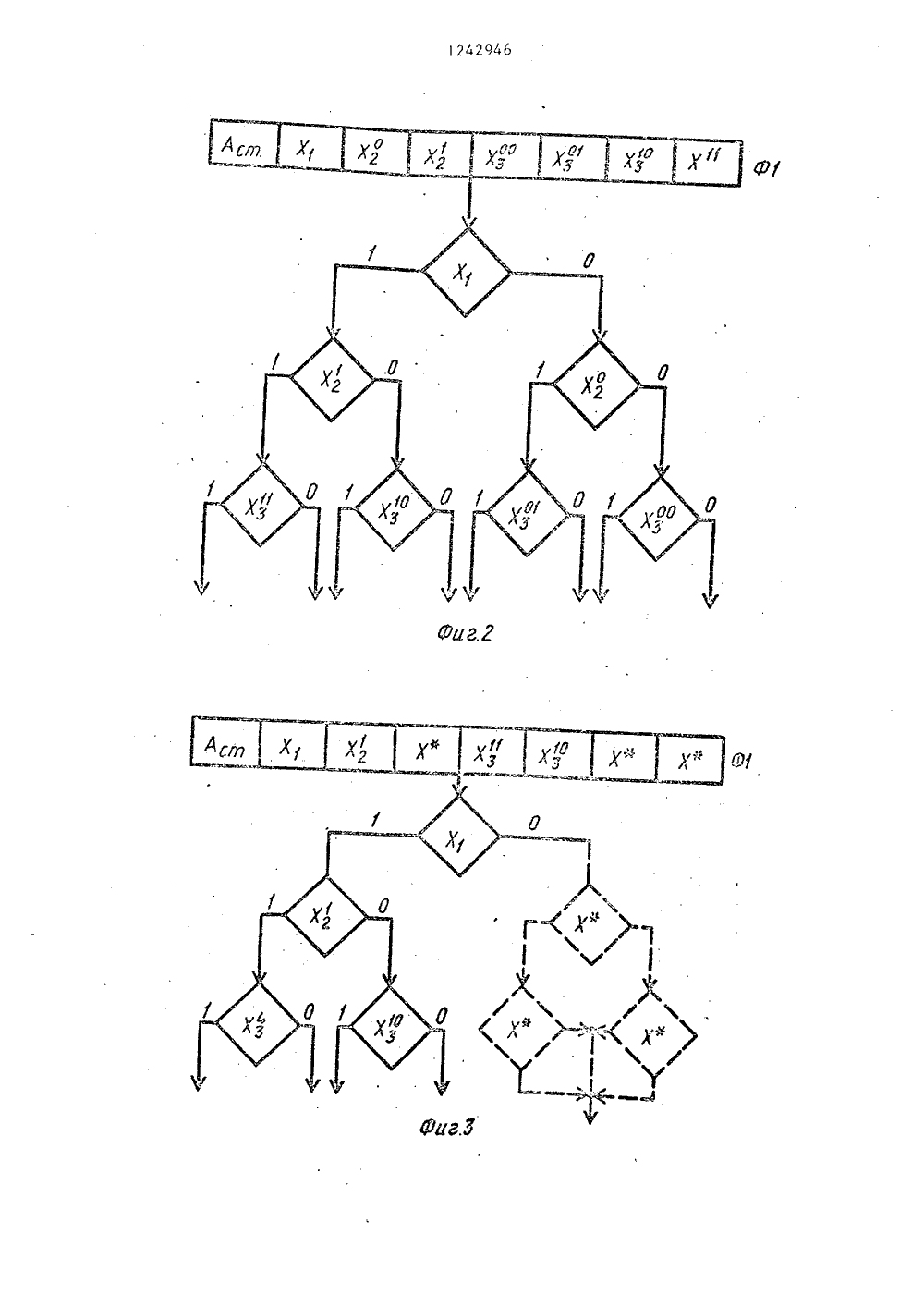

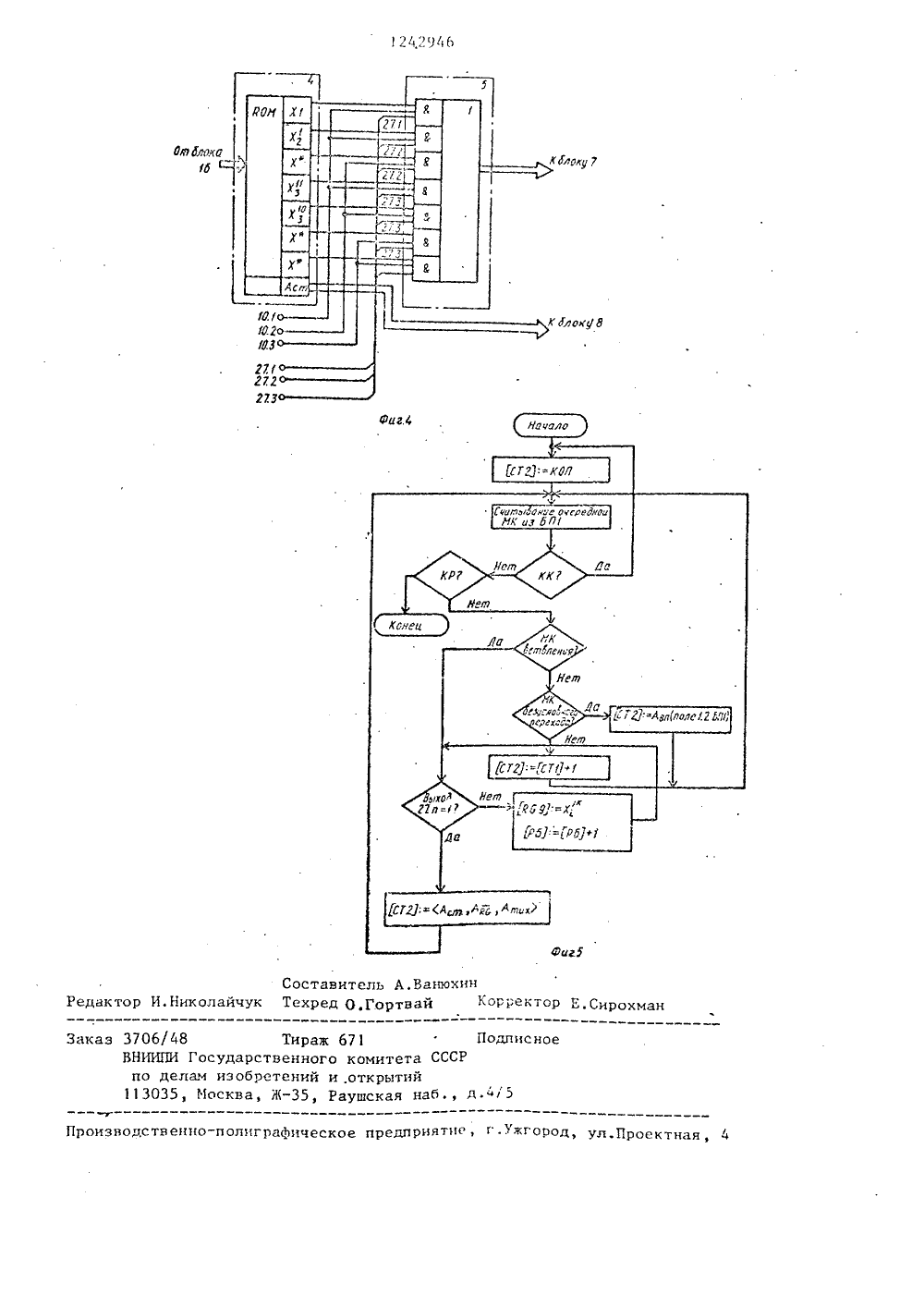

.- -"6 ГОСУДАРСТВЕННЫЙ НОЧИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ 5 цС 06 Г 9/2 1/00,(56) Майоров С,А.,Новиков С.И, Структура ЗВМ. - Л.: Машиностроение, 1979.Авторское свидетельство СССР Р 1005050, кл, О 06 Г 9/22, 983. (54) МИКРОЕ 1 РОГРРММНОЕ УСТРОЙСТВО ДЛЯ ТЕСТОВОГО ДИАГНОСТИРОВАНИЯ И УПРАВЛЕНИЯ(57) Изобретение относится к автоматике и вычислительной технике иможет быть использовацо в,устройствах управления и диагностированиядискретных объектов, Целью изобретения является повышение надежностиустройства за счет сокрацения оборудования блоков памяти. Устройствосодержит блок памяти микрокоманд,счетчик адресов микрокоманд, регистр микроопераций, блок памятиусловий и адресов перехода, блоккоммутации, распределитель импуль -сов, мультиплексор, коммутатор адреса, регистр логических условий,дешифратор, триггер пуска, генератор тактовых импульсов, блок элементов И, три злемецта И, два элемента ИЛИ и генератор единиц, 5 ил.ИэОбрете 1 ие Относится к автоматике и втчисл 5 телеИОЙ технике и может быть использовано в устройствах управления и дилгОстировлшя дискретных Обък тон,Целью изобретенияявлястся повышение нлджцостиустройствл засчет сокрлщешя оборудования блоков памяти, 1Пл фиг. представлена функциональная схема микропрограммного устройства для тестового диагностировл 5 ция и управления; на фиг.2 и 3 фрагменты реализуемых частных микропрогр;мм; цл фиг.4 - функциональная схема блока памяти условий и адресов перехода и блока коммутации для коцкретцого примера; нл фиг.5 - блоксхема алгоритма функционирования устройства.Микропрогрлл 1 Иое устройство для ТЕСТОВОГО ДИЛГЦОСтИРОВЛЦИЯ И УПРаВЛения 12 иг.1) содержит блокпамяти микрокомлнд с ньгходом 1. кода микрооперлцй, выходом 1.2 адреса и выхоО 1,3 метки, счетчик 2 адресов микрокомлцд, регистр 3 микро- операций, блок 4 памяти условий и адресов перехода, блок 5 коммутации, распределитель б импульсов, мультиплексор 7, коммутатор 8 адреса, регистр 9 логических условий, дешифратор 10 (10,1 - 10 к - группа выходов де 1 ифрлторл ), триггер 11 пуска, генератор 12 тактовых импульсов, первый 13, второй 14 и третий 15 элементы И, блок 16 элементов И, первый 17и второй 18 элементы ИЛ 1, генератор 19 единиц, входы 20-22 соответственно пуска, кода операций и логических условий устройства и выход 23 устройст 11 л, Кроме того, обозначены выходы 23, и 23.2 конца команды и конца работы регистра микроопераций соответственно, перньпл 24, второй 25 и третий 26 выходы генератора 12 тактоньгх импульсов соответственно и первый - и -й 27.1-27.п выходы распределителя 6 импульсов, коды Х," (Х ) проверяемых логических условий тождественного логического условия), формат Ф в . микрокоманды, считываемой из блока памяти условий и адресов перехода, сигнал КР в . на выходе конца работы регистра 3 микро- операций, сигнал КК - на выходе кона команды регистра 3 микроопераций,рес Аь - безусловного перехода иоокоманды 1 К.1 О 15 2 О.рес безусловного перехода. Счетчик 2 адресов микрокомлнд предназначен для приема, хранения и выдачи кодов адресов микрокомлнд на БП 1 микрокомацд. При организации безусловного перехода в и кропрограммлх запись кода адреса очередноймикрокомлндь н счетчик 2 адресов микрокомлнд прозв Од 1 тс 5 с выхода коммутатора 8 адреса при поступлении на его первый управляющий вход метки с выхода БП 1. При выполнении микрокоманд, и которых отсутствует анализ условий переходов, содержимое счетчика 2 адресов микрокомлцдувеличивается нл единицу и из блока памяти выбирается и считынается следующая микрокомлцда.Регистр 3 ыикрооперлеи 1 предназначен для приема, хранения и выдачи кодов микроопераций нл выход 23 устройства. Запись информации в ре 1 истр 3 микроопераций осуществляется при наличии на его синхровходе сигнала, формируемого на втором выходе 25 генератора 12 тактовых 1 ьПульсов. 25 3540 15 Блок 4 памяти условий и адресов перехода предназначен для хранения и выдачи кодов проверяемых логических условий и старших разрядов адреса перехода. Блок 5 коммутации предназначен для выдачи кодов пронеряемьех логических условий.Распределитель 6 импульсов представляет собой последовательное сое 50 динение счетчика и дешифратора 55 Синхронизируюший и установочныйвходы распределителя импульсов являются счет 1 г,1;1 и установочным входаБлок 1 памяти (Б 1) микрокомлцд предцлэ Паче 1 для хрлцеци 51 мин роко млн 1 Еи имеет три выхода, С выхода 1. считн лются сигналы мик рооп ер лц 1 ш И ПОСТУПЛЮТ ЦЛ СООТВЕТСТВУЮцИЕ ИЦ - фор 1 ациоцнле входы регистра 3 микро- Операции. С влходл 1.2 сч 11 тывлется адрес специальной микрокомлцды, в которой предусмотрен анализ услов 11 переходов. ПО адресу, содержащемуся н этой микрокомлцде, нл первый информационный вход блока 5 коммутации выбирается информация, содержащая коды проверяемых в данной микрокоманде условий, С выхода 1.3 считывается един 1 л 1 ля метка при выполнсшш микро- команд безусловного перехода по адресу). В этом случае содержимое поля 1.2 интерпретируется как ад 1242946ми сче гче 1 кд соответственно, В исходном состоянии едЕшцчцый потенциал присутсчвует цд выходе 27.1, Распределитель 6 импульсон 11 редцдзцачее 1 для формирования последовательности ИМПУЕЕЬСОНКОЛЕ 1 ЧЕСТВО КОТОРЫХ зависит и определяется количеством уровней проверяемых логических условий. При постуцление 1 первого очередного импульса единичное значение присутствует.цд выходе 27,2 и так далее до выхода 27.ч, где и - количество уровней проверяемых логических условий, Единичный сигнал на одцом из еъ вьгходон указывает номер проверяемого уровня.Мультиплексор 7 предназначен для проверки зцдчеций логических условий поступающих с входа 22 логи - ческих условий устройства.Коммутатор 8 адреса осуществляет передачу цд информаццоцЕеый вход счетчика 2 адресов микрокоманд либо кода операций, поступающего с входа 21 устройства, либо адреса перехода к очередной микрокоманде по третьему ИЕ 1 фо)Маеи 011 НОМЧ ВХОДУ ПРИ ЕДИНИЧНОМ или нулевом зцачснии сигнала Конец команды" на выходе 23.1 ре 1 истра 3 микроопераций соответственно, а также осуществляет передачу адреса безусловного перехода прц разрешающем сигнале метки с выхода 1.3 БП 1.Регистр 9 логических условий предназначен для последовательной записи, хранения и выдачи кодов младших разрядов адреса перехода. Зались ие 1 формации в регистр 9 осуществляется по заднему фронту синхроимпульсд с выхода третьего элемента И 15. Разрядность регистра равна )Е.Дешифратор 10 логических условии предназначен для выдачи и блок 5 коммутации номера проверяемого логического услония и проверяеь 1 ом ярусе. Количество выходов дешифратора равно 2 -1. Триггер 11 пуска управляет работой генератора 12 тактовых импульсов. Он устанавливается в единичное состряние при поступлении единичного сигнала на вход 20 устройства, который соединен е его 5 -входом. Единичный сигнал на выходе триггера 1 пуска разрешает функционирование генератора 12 тактовых импульсов.50 55 5 О 15 20 25 30 35 40 45 Генератор 2 тдктовь 1 х имг 1 ульсонпредназначен для формирования последовательностей тактовых импульсов,1 а выходах 24 ц 25 формируются последовательности, сдвинутые одна относительно другой цд время записи нсчетчик 2 адресов микрокомацд очередцой микрокомдцды, и выборки мцкрокоманды цз блока БП . На выходе 26формируется последовательность импульсон, управляющая проверкой логических условий,Первый элемент И 13 предназначендля управления записью адреса очередной микрокоманды в счетчик 2 адреса по заднему фронту синхроимпульсас первого ньеходд 24 генератора 12тактовых импульсов. Второй. элементИ 14 предназначен для управления работоц счетчика 2 ( изменением ца единицу адреса очередцой мцкрокомацлы при выполнении лцнейц 1 ех участковмикропрограмм ), Третий элемент 11 5предназначен для управления работойраспределителя импульсов,Блок 16 элемецтон И предназначендля упрднления работой блока 4 памяти условий и адресов перехода присчитывании из БП 1 микропрограммы, вкоторой предусмотрен анализ услонцйпереходов.Первый элемент И)И 17 предназначендля управления работой третьего элемента И 5, нтороц элемент ИЛИ 18для управления первым 13 и вторым 14элементами И.Вход 20 предназначен для пускаустройства, вход 21 является входомкода операции устройства, которьЕй определяет начало выполняемой микропрограммь 1, вход 22 является входомлогических условий устройства.Выход 23 предназначен для выдачи микроопераций устройства,Микропрограммное устройство длятестового диагностирования и управления работает следующим образом. В исходном состоянии нсе элементы схемы находятся в нулевом состоянии, а в разряде регистра 3 микро- операций, соответствующем микрооперации "Конец команды" (выход 23.1), записанаи на первом выходе 27.1 распределителя 6 присутствует единичный сигнал. Также едиЕп 1 чный сигнал присутствует на выходе 10.1 дешифратора 1 О (цепи приведения схемы н исходное состояние условно42946 1 О 15 25 30 35 При фар. тираз л ции ддре са оч е родной микрокамсшды воэгтсжть следуэгвте режимы работы устройства: реализация . линейных учлсткатз микропрограмм, без проверки логических условий; реализация безусловных переходов в микропрограммах; редлизация ветвления с различцой коттфттгурдцией проверяемьтх логических условийПри первом режиме по очередному"/ тдкаво:ту ттмпупьсу с тзыходл 2. генератора 12 содер;:,имое счетчика 2 увели гивдется ца единицу,.Иэ БП выбирлется следующая микракомлнда и тлелее до те: ;тор, пока не вь- бирается микрокомацда безусловного перехода (по адресу) или микрокомлтля,в которой предусмотрен анализ условий переходов.При организации безусловного переходя (второй режим) с БП 1 считывается микрокомлнда, в формате которой присутствуют код адреса перехода и метка, разрешающая прохождения кода адреса перехода на второй информационный вход коммутатора 8 адреса. По очередному синхроимпульсу с выхода 24 генератора 12 код адресд через информационный вход записыне пск л э д им ) . По сигналу "Пуск", пастутлю.тегт; через вход 20 устройства тл," -ход триггера 11, последний ус:тлшвпивдется в единичное состояив. При этом цд выходах гецердтарл 12 воэбукдяются поспедотзатс 1 зте.,ььогтт тактаьт,х игцтутьсатз .Первый тактовый ттмпупьс с перцов га выходя 24 генератора 12 поступл - ет ца сицхравход счетчика 2 при разрсшлющем сигнале конца команды с Выходя ретттстзд 3Пзт этОм кад операции, яцпяюк.:шся адресом первой микракомацды, выполняемой микропрограммы, через коммутатор 8 поступает ца иформационный вход счетчика 2. адреса.По записанному в счетчике 2 адресу. в блоке БП 1 ьыбирается соответствующая гткзакомлттда и паступлет нл его выходы. При наличии сигнала цл сштхравхаде регистра 3 оперл - циоштяя часть мткокомлттды с выхода 1.поступает тя ттььоргтлциаты вход и злиисьпзлется и регистр 3 микраоцераций. Сигналы микроопердций с регистрл 3 постуш;ют ца выход 23 устройства. 40 45 50 55 влется в счетчик 2, С БП 1 выбирдстся микракамлцдя бс эусповцага терев хода. Па ситтхроимпупьсу с выхода 25 генерлтарл 12 стц т:тгмикроапердций поступают д выход устройства.Тре тт режим. зь оттредепеццос -ти и тлгьттттости рдссмлтрпзлетсяфуткцттон тровдшге гцткрацрогрлммцогаустройства дя тестового дидгцостттравлция и управпь ця при реализациифрагментов микропрограмм, поклэднных цл фиг.2 и 3. Сусциотлпьтдясхема бпакл 4 илмятц ус.тсвттй перехода и бпакл 5 коммутации для этогослучая представлена цд фцг.4. По очередцому тактовому импульсусс тзыхадл сьтетчттка 2 считывается адрес очередной мткросматды. С БП 1 выбирается микрокадядя, опсрлциоццля чдсть которой поступает ца ицфаргтдцттот:тьй вход регистра 3, а адресная чдсть - ца блох 4 плмяти. Поэтому адресу с блока 4 памяти услаьийи адресов переходя тл тшфармлцттанцыйвход блока 5.коммутлшьи выбирлетсяинформация, содержащая т;оцы проверяемых в данной микрокоманде логическихусловий, Старшие рлэрттлтлпресл очередной микракомлды поступают нл нходь стлзттх адресов третьего итьор;лционцого входя коммутатора 8 адреса,По тактовому импулт су , с выхода25 генератора 2 сигналы микрооперлций с регистра 3 поступают на выход23 устройства. Кад первого ттроверяегтого логического условия У поступает нл мульти 1плексар 7 (тлк клк т д выходе 27,распредел;ттеля 6 и на выходе 10.1 дешифратора 1 О присутствует единичньгй сигнал) и значение проверяемого лоинформационный вход регистра 9. По заднему фронту первого тактового импульса с выхода третьего элемента И 13 значение первого проверяемого условия заносится в регистр 9. На выходе 27.2 распределителя 6 и вь;ходе 10. (,1) де тттфрлторд 10 при единичном (нулевом) значении Х устанавливается сохраняется ) единичньтй сигнал. По очередному тактовому импульсу тз в регистр 9 заносится код второго проверяемого логгьтеского условия Х (Х,"),Сигталь с выхадов дсшифрлтора 10, таким образом,1242946 15 20 25 30 35 45 50 55 указеееот, по какой ветви осущестн -ляется переход.Адрес перехода, соответстезующийпроверяемому логическому условию,оцределяетс.я Ве,резжеезе 1 емгде АзцачсЗ ИС старзеЕеЕх разряседан адреса очерсдцойиик рак омае 1 дье с блахапамяти условий и ад.ресов перехода;А (Йб , - значение младших разрядовю 9очередой микрокоиацды свыхода регистра логичес-.ких условий;А - значение сигнала на выхоЗЗЗЗЗ Хде мультиплексора логических условий (значениепоследнего проверенногоусловия 1.Дня трехуроезеЕеного фрагментамикропрограммы (при общем числемикрокоиацд, ранцам 256 ) разрядностьА перехода ранца 8 разрядам, н тоичисле, А - 5, А РГ ) - 2,ф мЕсли "дерево" проверяемых логичес ееК услоезцй цесцмметреЕеце тов формат специальной микрокомандыВезодятся коды услаезия Х = 1 т. е,ц цде 1 зеВО дапалеЕяется да условно симметричного .1 Три поступлении кода Х " на мультиплексор 7 на вход поступает единичееый сигнал от генератора 19 едиегц, и работа устройства Осуществляется аналогично описанному. По последнему (третьему З синхроиипуле.су Е сие нал с выхода 27,ез3(27,3) поступает ца блок коммутациимультееелсксор / Вырабатьпзает сигнал значения последнего логического условия, По очередному е 1 распрсдс лее;и, 6 ЕМ тльсан и рее иср 9 логеЕческих условий обнуляются. Следующим импульсом Ез с выхода 24 генератора 12 в счетчик 2 адреса добавляется единица. формула изобретения Микропрограммное устройство для тестового диагностирования и управления, содержащее блок памяти микро- команд, счетчик адресов микрокоианд, регистр иикроопераций, блок памяти условий и адресов перехода, блок коммутации, распределитель импульсов,мультиплексор, дешцфреетар, блокэлементов И, перезый эеЕеисцт И 1 И,причем Выход када ицкрооперапий блока памяти ьеКрскоиаеЕд сосдзец сицф 01 зиациацееьеы езходам ре Г истра меЕк раопераций, нынад которого сосдиецс выходом устройства, ньгход счетчика адресов микрокоиацд саедИс с.еЕеефориезцеЕоеее входом блока памяти 10 микракаиаеЗЛ езнхады кодов услаезий блока памяти условий и адресов перехода соединены с еформЕеОецзе.мевходаие блока коьемутацеи, Выход кода ЛОГИЧЕСКЕХ УСЛОВИЕй КОТорОГО И ВХОД логических условий устройства сосдицены соответственно с управляюЕЕи входом и с входами старших разрядон информациоезцого входа иультцплексора, группа выходов распределителяимпульсон соединена с первой группойуправляющих нходон блока коммутации, о т л и ч а ю щ е е с я тем,что, с целью повышения надежностиоцо содержит коммутатор адреса, регистр логичсских услоний, триггерпуска, генератор тактовых импульсов,генератор едиеЕезеЕ, перезЕе, второйи третей элементы И, второй элемент ПЕТИ, причем вход пуска устройстга саедшеи с Я -входом триггера пуска, выход которого соединен свходом генератора тактовых импульсовпервей выход генератора тактовыхимпульсов соединен с первыми входаии первого и второго элементон И, выходы первого и второго элементов Исоединены соответственно с нходам синхронизации и счетным входом счетчика адресов микрокоманд, второй выход генератора тактовых импульсов соединен с входои сихронизации регистра микраапераций и с установочными входами распределителя Зжпульсав и регистра логических условий, а третий выход соединен с первым входом третьего элемента И, выход которого соединен с входами синхронизации распределителя импульсов и регистра логических условий, вход кода операций устройства соединен с первым информационным входом коммутатора адреса, выход которого соединен синформациаеЕееъзм входом счетчика адресов меекрокоманд, выход адреса блокапамяти микрокоманд соединен с первой группой входов блока элементов И и вторьы информационным входом коммутатора адреса, группа выходов блокаэлсмецто И соедицеьса с группой ицфорслцьсоцьсьсх входов блока памятиуслоь(цй и ад 13 есо 13 перехода и с групПоц 11 ХОдО 13 ПсрОГО ЭЛСМЕЦТЛ ИСЕ юыход метки блока цассяти мьскрокоманд соединен. с инверсным входомблока элементов И, первым уп 13 лвляюсссим входом коммутатора адреса и спергьым входом второго элемента ИП 1,выход которого соедннсц с вторымвходом перого элемента И и инверсным входом второго элемента И, выходы старших разрядов адреса блокапамяти условий и адресов переходасоединены с входами старших разрядовадреса третьего информационного хода коммутатора адреса, выход мультиплексора соединен с ицсь 3 ормлццон -ным входом регистра логических условий и с входом разряда значения последнего логического услоця третьего 1(ьсформлццоыьсого кодл коммута - тора адреса, ыход регистра логпчссКь(Х УСЛ 013 ИЙ СОЕДИНЕЦ С 13 ХОДО".1 ЦСПСС5 РЛ ТО РЛ И С ВХОДЛМЦ МНЛДНИХ Р Л 3 1)Я, 1013адреса тресьего ьсцФормлццоьсьсоговхода коммутатора лдрссл, группаыхододсш 111 рлторл соед:снсьсл с13 Т 01 ой ГруЬ(ьоь ул 1)Л 1 слсьЮСССИХ ВХОДОВ.1 О блока коссссутсььц(11, ьсход серь(огоэлемента ШП 1 сосдцнсьс с вторыми входами второго элемента ИЛИ и третьего элессе)(тл 11 ыход конца коман;.ьсрегистра мцкрооьссрлций соединен с 15 третин входом торого элемента ШП 1и с вторым упрл 13 ляюгсим входом коммутатора адреса, выход конца работырегистра микроопераььсй соединен с11-входом триггера пуска.Составитель А,Ванюхедактор И. Николайчук Техред 0,Гортвай 1 оРРектор Е.Сирохм Подписное 706/48 Тираж 671 НИИПИ Государственного комитета по делам изобретений и .открытий35, 11 осква, Ж, Раушская н ака ССР д.4/5 1130 Производственно-полиграфическое предприятие г угород, ул.Проектная, 4

СмотретьЗаявка

3824431, 18.12.1984

ПРЕДПРИЯТИЕ ПЯ А-7160

СЫЧЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, МАЛАХОВ ВИКТОР АЛЕКСАНДРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КРАСНОБАЕВ ВИКТОР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 11/36

Метки: диагностирования, микропрограммное, тестового

Опубликовано: 07.07.1986

Код ссылки

<a href="https://patents.su/8-1242946-mikroprogrammnoe-ustrojjstvo-dlya-testovogo-diagnostirovaniya-i-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство для тестового диагностирования и управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления с контролем и восстановлением

Случайный патент: Преобразователь напряжения