Устройство для контроля блоков микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1599861

Авторы: Благодарный, Еременко, Тимонькин, Ткаченко, Харченко

Текст

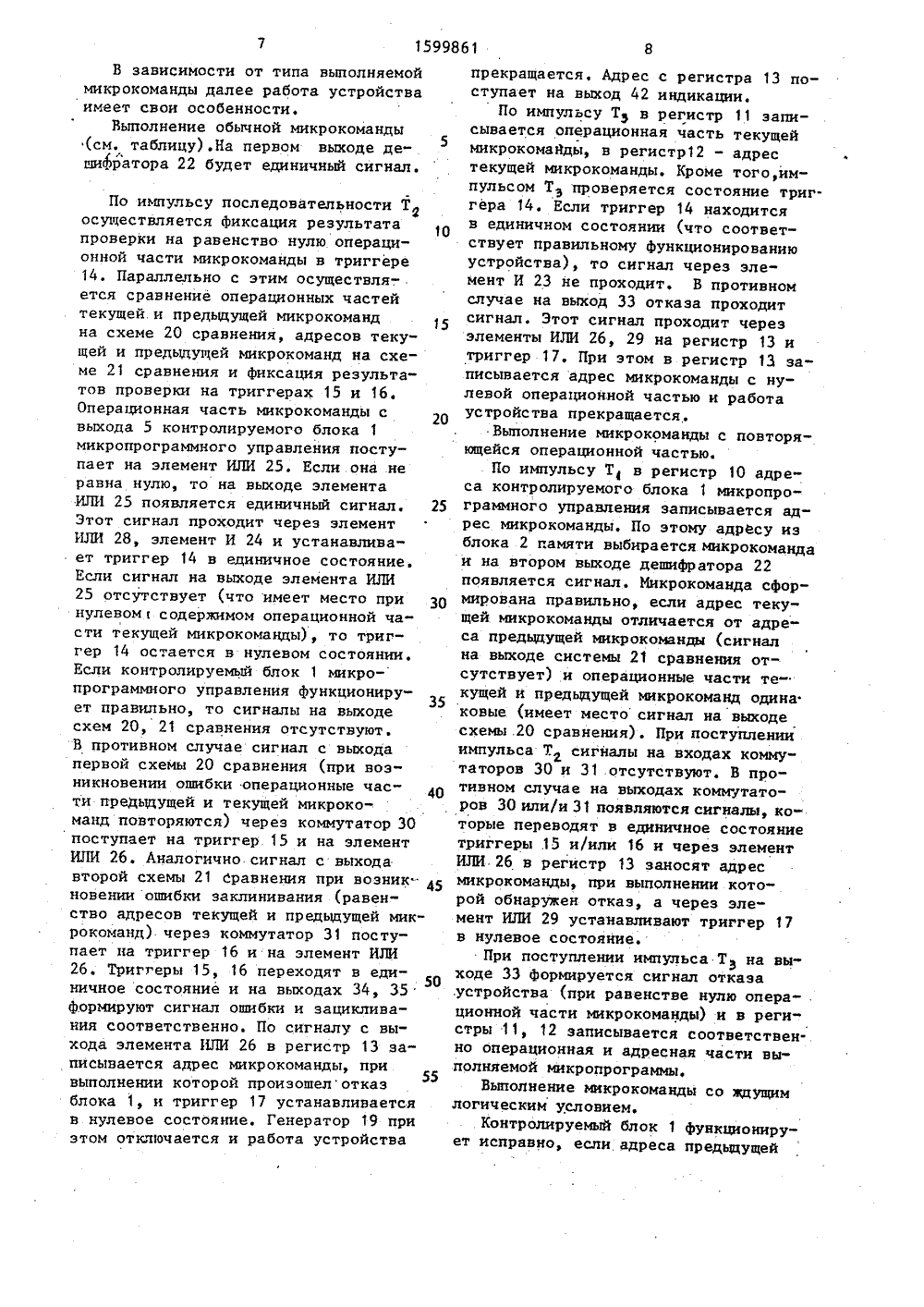

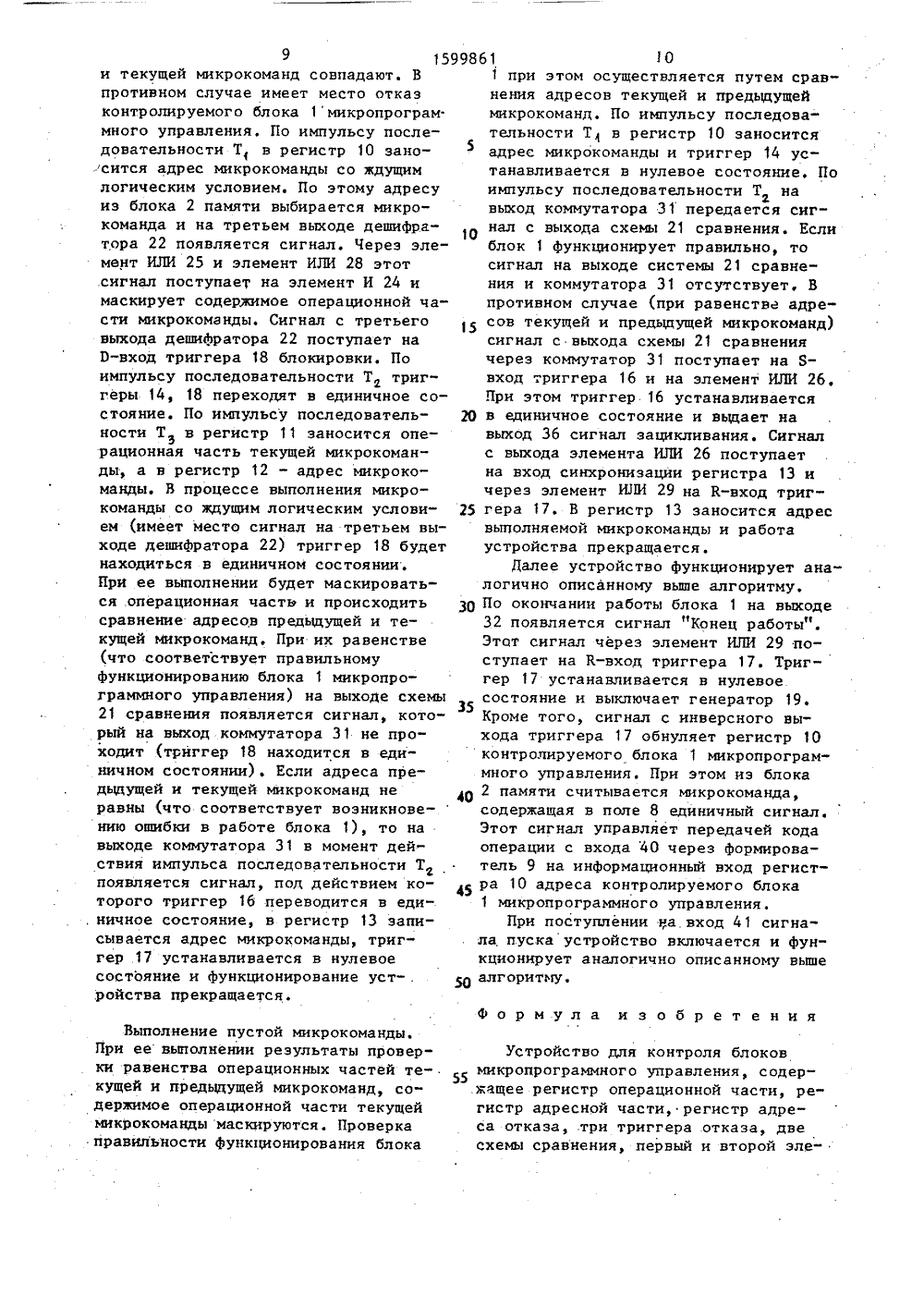

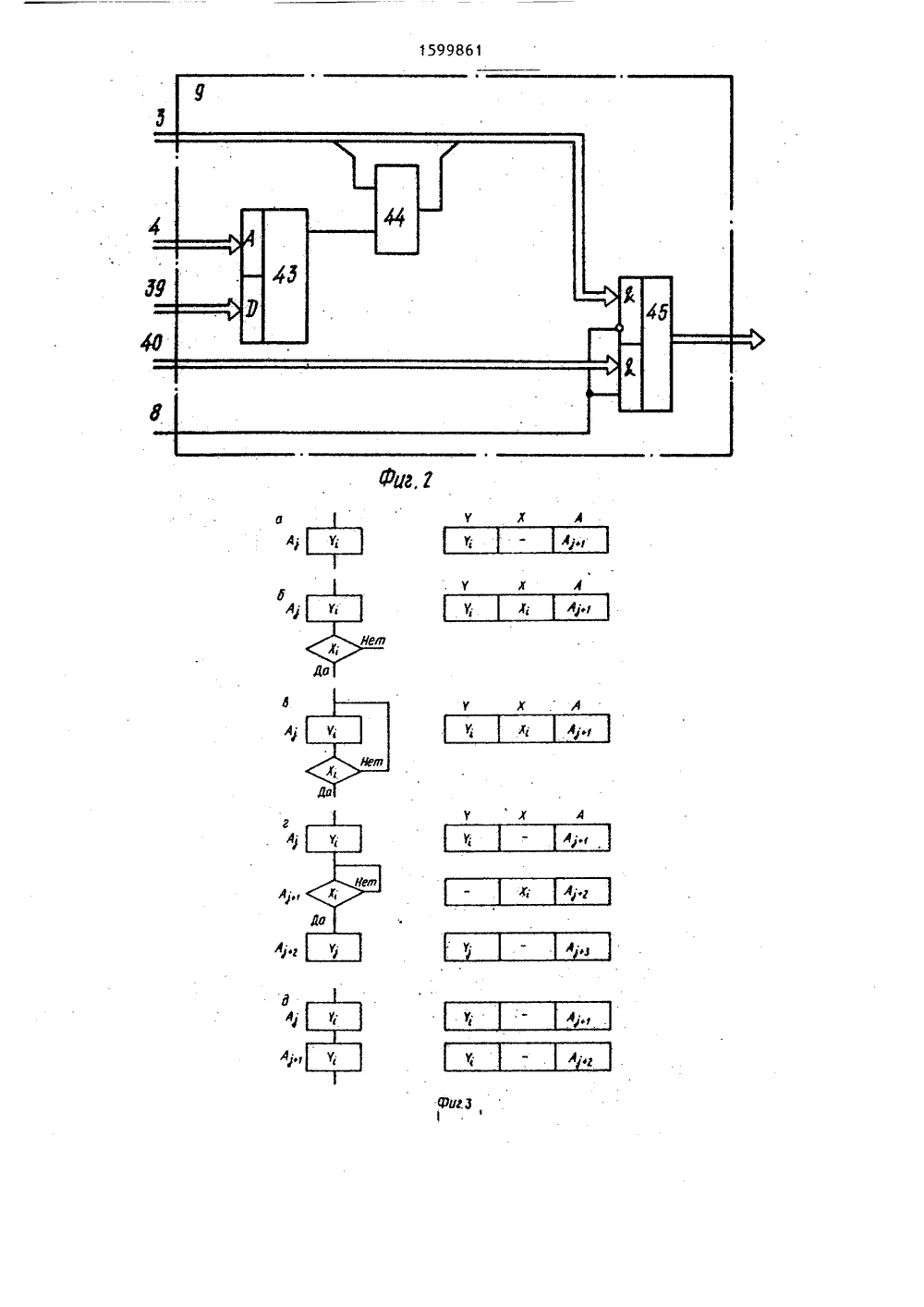

(54) УСТРОЙ МИКРОПРОГР (57) Изобре тике и вычи жет быть ис комплексах тельных и у ТВО ДЛЯ КОНТРОЛЯАММНОГО УПРАВЛЕНИение относитсялительной технользовано в отлмикропрограммныравляющих сист БЛОКОВ автомаке и мо адочных вычислим. Цель иг ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕК АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидУ 940159, кл. С 061982.Авторское свидет1203526, кл. С 06 изобретения -расширение области применения устройства за счет увеличения числа типов проверяемых микрокоманд, .Она достигается введением триггера 17 пуска, триггера 18 блокировки, генератора 19, дешифратора 22,третьего-пятого элементов ИЛИ 27-29,первого и второго коммутаторов 30,31. Вместе с тем устройство для контроля блоков микропрограммного управления содержит регистры операционной части 11, адресной части 12, адреса отказа 13, триггеры 14-16 отказа, схемы 20 и 21 сравнения, элементы И 23 и 24, два элемента ИЛИ 25 и26. Сущность заключается в обеспечении воэможности контроля блоковмикропрограммного управления, реализующих. "пустые" микрокоманды со "жду"щими" логическими условиями. 4 ил.,1 табл.Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе отладочных комплексов микропрограммных вычислительных и управляющих систем.Цель изобретения - расширение области применения за счет увеличения числа типов проверяемых микрокоманд.На фиг. 1 приведена функциональ" ная схема устройства; на фиг.2 - схема блока Формирования адреса команд; на фиг,З - фрагменты реализуемых блоками микропрограммного управления алгоритмов контроля и управления и соответствующие им варианты кодирования полей операционной части, адреса, кода условия микрокоманд; на фиг.4 - временная диаграмма работы устройства.2 ОУстройство для контроля блоков микропрограммного управления (фиг.1) содержит контролируемый блок 1 микропрограммного управления, состоящий из блока 2 памяти микрокоманд с выходами 3 адреса очередной микрокоманды, 4 кода проверяемого логического условия, 5 мнкроопераций, 6, сигналов меток типов выполняемых микрокоманд 8 сигнала конца микропроФ30 граммы, формирователь 9 адреса, регистр 10 адреса, регистр 11 операционной части, регистр 12 адресной части, регистр 13 адреса отказа, первый-третий триггеры 14-16 отказа, триггер 17 пуска триггер 18 блоки ровки, генератор 19 импульсов, первую и вторую схемы 20, 21 сравнения, дешифратор 22, первый, второй элементы И 23, 24, первый-пятый элементы ИЛИ 25-29, первый и второй коммута торы 30, 31, выход 32 коммутатора 31, выходы 33-35 соответственно отказа, ошибки, зацикливания устройства, первый-третий выходы 36-38 генератора 19, вход 39 сигналов логических условий, вход 40 кода операции блока 1 микрокопрограммного управления, вход 41 пуска, выход 42 индикации адреса устройства.50Формирователь 9 адреса контролируемого блока 1 микропрограммного управления может быть выполнен по одной из традиционных схем. Вариант реализации формирователя 9 адреса приведен на Фиг.2. Он состоит из мультиплексора 43 логических условий, сумматора 44 по модулю два коммутатора 45. На фиг.З, 4 использованы обозначения, введенные на фиг.1.Рассмотрим назначение основных элементов и узлов устройства.Регистр 11 служит для хранения кодов операционных частей предыдущих микрокоманд; регистр 12 - для хранения кодов адресов предыдущих микро- команд; регистр 13 - для записи и хранения адресов мирокоманд, при выполнении которых произошел сбой или отказ работы устройства.Первый триггер 14 отказа служит для фиксации отказа, обусловленного физическими отказами на выходе 5 микроопераций блока 1 микропрограммного управления.Второй триггер 15 отказа предназначен для фиксации отказа, обусловленного ошибочным занесением в соседние ячейки одинаковых операционных частей микрокоманд с повторяющимися операционными частями.Третий триггер 16 отказа служит для фиксации отказа, обусловленного зацикливанием микрокоманды на каком- либо адресе, обнаруживаемого при сравнении адресных частей предыдущей и последующей микрокоманд.Триггер 17 пуска служит для включения генератора 19 при пуске устройства и его останова при возникновении в блоке 1 микропрограммного управления отказов, обнаруживаемых устройством. Кроме того, сигналом с инверсного выхода триггер 17 обнуляет регистр 10 адреса контролируемого блока 1 микропрограммного управленияеТриггер 18 блокировки позволяет маскировать результат сравнения адресов предыдущей и текущей микрокоманд при переходе контролируемого блока 1 микропрограммного управления к выполнению микрокоманд ветвления со ждущими логическими условиями.Генератор 19 предназначен для формирования трех последовательностей Т 1, Т, Т тактовых импульсов, синхронизирующих работу контролируемого блока 1 микропрограммного управления и устройства. На выходе 36 генератора.19 формируются импульсы последовательности Т 1, на выходе 37 " импульсы последовательности Т , на выходе 38импульсы последовательности Т. Временные интервалы между импульсами последовательностей Т,-Т з выбирают5 15998 сяисходя из обеспечения устойчивой работы элементов и узлов устройства.Первая схема 20 сравнения предназначена для формирования сигнала,соответствующего факту наличия одинаковых операционных частей соседних микрокоманд.Вторая схема 21 сравнения служит для формирования сигнала, соответствующего факту зацикливания микропрограммы (выполнение микрокоманд с одинаковым адресом).Элемент И 23 предназначен для формирования сигнала отказа на выход 33 устройства при равенстве нулю операционной части микрокоманды.Элементы И 24 и ИЛИ 26-29 предназначены для формирования сигналов управления работой коммутатора 31. 20Дешифратор 22 на одном из выходов формирует сигнал типа выполняемой микрокоманды в соответствии с таблицей. 61 бустройства при равенстве адресов текущей и последующей микрокоманд.Устройство для контроля работы блоков мИкропрограммного управления работает следующим образом.В исходном состоянии все элементы памяти устройства обнулены (цепи установки исходного состояния на схеме условно не показаны). При этом на выходе 8 контролируемого блока 1 микропрограммного управления присутствует единичный сигнал.При поступлении на вход 41 сигнала пуска триггер 17 устанавливается в единичное состояние и включает генератор 19.По первому импульсу последовательности Т в регистр 10 адреса конт-. рольного блока 1 микропрограммного управления с входа 40 через формирователь 9 записывается адрес первой микрокоманды микропрограммы. По этому адресу из блока 2 памяти микрокоманд считывается микрокоманда, содержащая следующие поля;после адреса очередной микрокоманды (поле 3);поле кода проверяемого логического условия (поле 4);поле микроопераций (операционная часть, поле 5);.поле сигнала первой метки (поле 6)фполе сигнала второй метки (поле 7); Номер возбужденного выходадешифратора 22 Код навыходах6, 7 Тип выполняемой микрокоманды Обычная микРокомандаИикрокомандас повторяющейся операционной частьюИикрокомандасо ждущим ло-,Гическим ус 4 Оловием"Пустая" мик- рокоманда О О О 1 1 О 50 Элемент ИЛИ 25 формирует сигнал 45при ненулевом содержимом поля микроопераций выполняемой микрокомандылибо при выполнении микрокоманды сождущим логическим условием. Коммутатор 30 предназначен для формирования сигнала ошибки при равенстве операционных частей предыдущей и текущей микрокоманд или при неравенстве операционных частей в мнкрокомандах с повторяющимися операционными частями,Коммутатор 31 служит для формирования сигнала зацикливания работы поле сигнала микрооперации "Конец команды" (поле 8) .. Операционная часть микрокоманды (поле 5) поступает на первую схему 20 сравнения, на информационные входы регистра 11 и на элемент ИЛИ 25. Код адреса очередной микрокоманды (поле 3) и код проверяемого логического условия (поле 4) поступают на формирователь 9 адреса и участвуют в формировании адреса очередной микрокоманды. Код адреса текущей микрокоманды с выхода регистра 10 адреса поступает на схему 21 сравнения и на информацоинные входы регистров 12, 13, Сигналы логических условий от объекта управления через вход 39 поступают на формирователь 9 контролируемого блока 1 микропрограммного управления и участвуют в формировании исполнительного адреса очередной микрокоманды.В зависимости от типа выполняемой микрокоманды далее работа устройства имеет свои особенности. Выполнение обычной микрокоманды(см. таблицу).На первом выходе де 5 шифратора 22 будет единичный сигнал.По импульсу последовательности Т осуществляется фиксация результата проверки на равенство нулю операционной части микрокоманды в триггере 14, Параллельно с этим осуществляется сравнение операционных частей текущей.и предыдущей микрокоманд15 на схеме 20 сравнения, адресов теку" щей и предыдущей микрокоманд на схеме 21 сравнения и фиксация результатов проверки на триггерах 15 и 16.Операционная часть микрокоманды с выхода 5 контролируемого блока 1 микропрограммного управления поступает на элемент ИЛИ 25. Если она не равна нулю, то на выходе элемента ИЛИ 25 появляется единичный сигнал. 25 Этот сигнал проходит через элемент ИЛИ 28, элемент И 24 и устанавливает триггер 14 в единичное состояние. Если сигнал на выходе элемента ИЛИ 25 отсутствует (что имеет место при нулевомсодержимом операционной части текущей микрокоманды), то триггер 14 остается в нулевом состоянии. Если контролируемый блок 1 микропрограммного управления функционирует правильно, то сигналы на выходе схем 20, 21 сравнения отсутствуют.В противном случае сигнал с выхода первой схемы 20 сравнения (при возникновении ошибки операционные час ти предыдущей и текущей микрокоманд повторяются) через коммутатор 30 поступает на триггер 15 и на элемент ИЛИ 26. Аналогично сигнал с выхода второй схемы 21 сравнения при возник 45 новении ошибки заклинивания (равенство адресов текущей и предыдущей микрокоманд) через коммутатор 31 посту- лает на триггер 16 и на элемент ИЛИ 26. Триггеры 15, 16 переходят в единичное состояние и на выходах 34, 35 формируют сигнал ошибки и зацикливания соответственно. По сигналу с выхода элемента ИЛИ 26 в регистр 13 записывается адрес микрокоманды, при выполнении которой произошел отказ блока 1, и триггер 17 устанавливается в нулевое состояние. Генератор 19 при этом отключается и работа устройства прекращается. Адрес с регистра 13 поступает на выход 42 индикации.По импульсу Т в регистр 11 записывается операционная часть текущей микрокомайды, в регистр 12 - адрес текущей мнкрокоманды. Кроме того,импульсом Тз проверяется состояние триг. гера 14. Если триггер 14 находится в единичном состоянии (что соответствует правильному функционированию устройства), то сигнал через элемент И 23 не проходит. В противном случае на выход 33 отказа проходит сигнал. Этот сигнал проходит через элементы ИЛИ 26, 29 на регистр 13 и триггер 17. При этом в регистр 13 записывается адрес микрокоманды с нулевой операционной частью и работа устройства прекращается.Выполнение микрокомаиды с повторяющейся операционной частью.По импульсу Т в регистр 1 О адреса контролируемого блока 1 микропрограммного управления записывается адрес микрокоманды. По этому адресу из блока 2 гамяти выбирается микрокоманда и на втором выходе дешифратора 22 появляется сигнал. Иикрокоманда сформирована правильно, если адрес текущей микрокоманды отличается от адреса предыдущей микрокоманды (сигнал на выходе системы 23 сравнения отсутствует) и операционные части текущей и предыдущей микрокоманд одина. ковые (имеет место сигнал на выходе схемы .20 сравнения), При поступлении импульса Т сигналы на входах коммутаторов 30 и 31 отсутствуют. В противном случае на выходах коммутаторов 30 или/и 31 появляются сигналы, которые переводят в единичное состояние триггеры .15 и/или 16 и через элемент ИЛИ 26 в регистр 13 заносят адрес микрокоманды, при выполнении которой обнаружен отказ, а через элемент ИЛИ 29 устанавливают триггер 17 в нулевое состояние.При поступлении импульса Т на выходе 33 формируется сигнал отказа .устройства (при равенстве нулю операционной части микрокоманды) и в регистры 11, 12 записывается соответственно операционная и адресная части выполняемой микропрограммы.Выполнение микрокоманды со ждущим логическим условием,Контролируемый блок 1 функционирует исправно, если адреса предыдущей9 1599861 10и текущей микрокоманд совпадают. В при этом осуществляется путем сравпротивном случае имеет место отказ нения адресов текущей и предыдущейконтролируемого блока 1микропрограм. микрокоманд, По импульсу последовамного управления. По импульсу после- тельности Т в регистр 10 заноситсядовательности Т в регистр 10 зано адрес микрокоманды и триггер 14 уссится адрес микрокоманды со ждущим танавливается в нулевое состояние. Пологическим условием. По этому адресу импульсу последовательности Т наиз блока 2 памяти выбирается микро- выход коммутатора 31 передается сигкоманда и на третьем выходе дешифра О нал с выхода схемы 21 сравнения. Еслитора 22 появляется сигнал. Через эле- блок 1 функционирует правильно, томент ИЛИ 25 и элемент ИЛИ 28 этот сигнал на выходе системы 21 сравнесигнал поступает на элемент И 24 и ния и коммутатора 31 отсутствует, Вмаскирует содержимое операционной ча- противном случае (при равенстве адрести микрокоманды. Сигнал с третьего 15 сов текущей и предыдущей микрокоманд)выхода дешифратора 22 поступает на сигнал с выхода схемы 21 сравненияЭ-вход триггера 18 блокировки. По через коммутатор 31 поступает на 8 импульсу последовательности Тг триг- вход триггера 16 и на элемент ИЛИ 26.геры 14, 18 переходят в единичное со- При этом триггер 16 устанавливаетсястояние. По импульсу последователь в единичное состояние и выдает наности Т в регистр 11 заносится опе- выход 36 сигнал зацикливания. Сигналрационная часть текущей микрокоман- с выхода элемента ИЛИ 26 поступаетды, а в регистр 12 - адрес микроко- на вход синхронизации регистра 13 иманды. В процессе выполнения микро- через элемент ИЛИ 29 на К-вход тригкоманды со ждущим логическим услови гера 17. В регистр 13 заносится адресем (имеет место сигнал на третьем вы- выполняемой микрокоманды и работаходе дешифратора 22) триггер 18 будет устройства прекращается.находиться в единичном состоянии. Далее устройство функционирует анаПри ее выполнении будет маскировать- логично описанному выше алгоритму.ся операционная часть и происходить 30 По окончании работы блока 1 на выходесравнение адресов предыдущей и те появляется сигнал "Конец работы".кущей микрокоманд, При их равенстве Этот сигнал через элемент ИЛИ 29 по(что соответствует правильному ступает на К-вход триггера 17. Тригфункционированию блока 1 микропро- гер 17 устанавливается в нулевоеграммного управления) на выходе схемы состояние и выключает генератор 19.3521 сравнения появляется сигнал, кото- Кроме того, сигнал с инверсного вырый на выход коммутатора 3 1 не про" хода триггера 17 обнуляет регистр 10ходит (трнггер 18 находится в еди" контролируемого блока 1 микропрограм"ничном состоянии) . Если адреса пре- много управленияПри этом из блокадыдущей и текущей микрокоманд не 4 О 2 памяти считывается микрокоманда,равны (что соответствует воэникнове-содержащая в поле 8 единичный сигнал.нию ошибки в работе блока 1), то на Этот сигнал управляет передачей кодавыходе коммутатора 31 в момент дей- операции с входа 40 через формироваствия импульса последовательности Т тель 9 на информационный вход регистгпоявляется сигнал, под действием ко ра 10 адреса контролируемого блокаторого триггер 16 переводится в еди микропрограммного управления.. ничное состояние, в регистр 13 запи- При поступлении на. вход 41 сигнасывается адрес микрокоманды, триг- . ла пуска устройство включается и фунгер 17 устанавливается в нулевое кционирует аналогично описанному вышесостояние и Функционирование уст- . 5 О алгоритму.ройства прекращается,Формула изобретенияВыполнение пустой микрокоманды. При ее выполнении результаты проверки равенства операционных частей текущей и предыдущей микрокоманд, содержимое операционной части текущей микрокоманды маскируются. Проверка правильности функционирования блока Устройство для контроля блоков микропрограммного управления, содержащее регистр операционной части, ре" гистр адресной части, регистр адреса отказа, .три триггера отказа, две схемы сравнения, первый и второй эле1 О 11 159 менты И, первый и второй элементы ИЛИ, причем вход устройства для подключения к выходу микроопераций контролируемого блока микропрограммного управления соединен с группой входов первого элемента ИЛИ, информационным входом регистра операционной части ипервым входом первой схемы сравнения, выход регистра операционной части соединен с вторым входом первой схемы сравнения, вход устройства для подключения к адресному выходу контролируемого блока микропрограммного управления соединен с первым входом второй схемы сравнения, информационными входами регистра адресной части и регистра адреса отказа,. Выход реги" стра адресной части соединен с вторым входом второй схемы сравнения, инверсный выход первого триггера отказа соединен с первым входом перво" го элемента И, выход которого соединен с первым входом второго элемента ИЛИ и является выходом отказа устройства, вход пуска которого соединен с В.-входами второго и третьего триггеров отказов, прямые выходы которых являются соответственно выходом ошибки и выходом зацикливания устройства, выход второго элемента ИЛИ соединен с входом синхронизации регистра адреса отказа, выход регист-. ра адреса отказа является выходом индикации адреса отказа устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет увеличения числа типов проверяемых микрокоманд, устройство содержит триггер пуска, генератор импульсов, первый и второй коммутато" ры,третий, четвертый и пятый элемен" ты ИЛИ, триггер блокировки, дешифратор, причем вход пуска устройства соединен с 8-входом триггера пуска, прямой выход которого соединен с входом генератора импульсов первый выход которого соединен с Е-входом первого триггера отказа и выходом устройства для подключения к входу синхронизации контролируемого блока микропрограммного управления, второй выход генератора импульсов соединен с входом синхронизации триггера бло.кировки, с первыми управляющими входами первого и второго коммутаторов, первым входом второго элемента И, третий выход генератора импульсов со единен с входами синхронизации реги 9861 12 стра операционной части, регистраадресной части и вторым выходом первого элемента И, выходы устройствадля подключения к выходам первой ивторой меток контролируемого блокамикропрограммного управления соединены,соответственно с первым и вторым входами дешифратора,первый выход дешифратора соединен с вторым уп. равляющим входом первого коммутатора и первым выходом третьего элемента ИЛИ, второй выход дешифратора соепинен с третьим управляющим входом 15 первого коммутатора и вторым входомтретьего элемента ИЛИ, третий выход дешифратора соединен с входом первого элемента ИЛИ, информационным входом триггера блокировки и вторым управляющим входом второго коммутатора,четвертый выход дешифратора соединен с четвертым управляющим входомпервого коммутатора и первым входомчетвертого элемента ИЛИ, выход первойсхемы сравнения соединен с первыминформационным входом первого коммутатора, выход первого элемента ИЛИсоединен с вторым входом четвертогоэлемента ИЛИ и вторым информационным ЗО входом первого коммутатора, выход которого соединен с 8-входом второготриггера отказа и вторым входом второго элемента ИЛИ, выход третьегоэлемента ИЛИ соединен с третьим управляющим входом второго коммутатора, выход четвертого элемента ИЛИ со"единен с вторым. Входом Второго элемента И, выход второго элемента Исоединен с Я-входом первого триггераотказа, выход триггера блокировки соединен с четвертым управляющим входомвторого коммутатора, выход второйсхемы сравнения соединен с информационным входом второго коммутатора,выход которого соединен с 8-входомтретьего триггера отказа и третьимвходом второго элемента ИЛИ, выходвторого элемента ИЛИ соединегг с первым входом пятого элемента ИЛИ, вход 5 О устройства дпя подкгпочения к выходусигнала микрооперации "Конец работы"контролируемого блока микропрограммного управления соединен с вторым входомпятого элемента ИЛИ, выход которого сое-.динен с К-входом триггера пуска,инверс."ньгй выход триггера пуска соединен с выходом устройства для подключения к входуустановки коитролируемогв блока микро -программного управления.1599861 Редактор А.Маковская Заказ 3144 Тираж 570 ПодписноеВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СЧСР113035, Москва, И, Раушская иаб., д, 4/5 изводственно-издательский комбинат "Патент", г. Ужгород, ул, Гага Состав Техред ель Д.Ван

СмотретьЗаявка

4622556, 20.12.1988

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ЕРЕМЕНКО ОЛЕГ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 11/16

Метки: блоков, микропрограммного

Опубликовано: 15.10.1990

Код ссылки

<a href="https://patents.su/8-1599861-ustrojjstvo-dlya-kontrolya-blokov-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля блоков микропрограммного управления</a>

Предыдущий патент: Устройство для контроля функционирования логических блоков

Следующий патент: Устройство для контроля микропроцессора

Случайный патент: Устройство для измерения ортогональных составляющих сигнала