Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

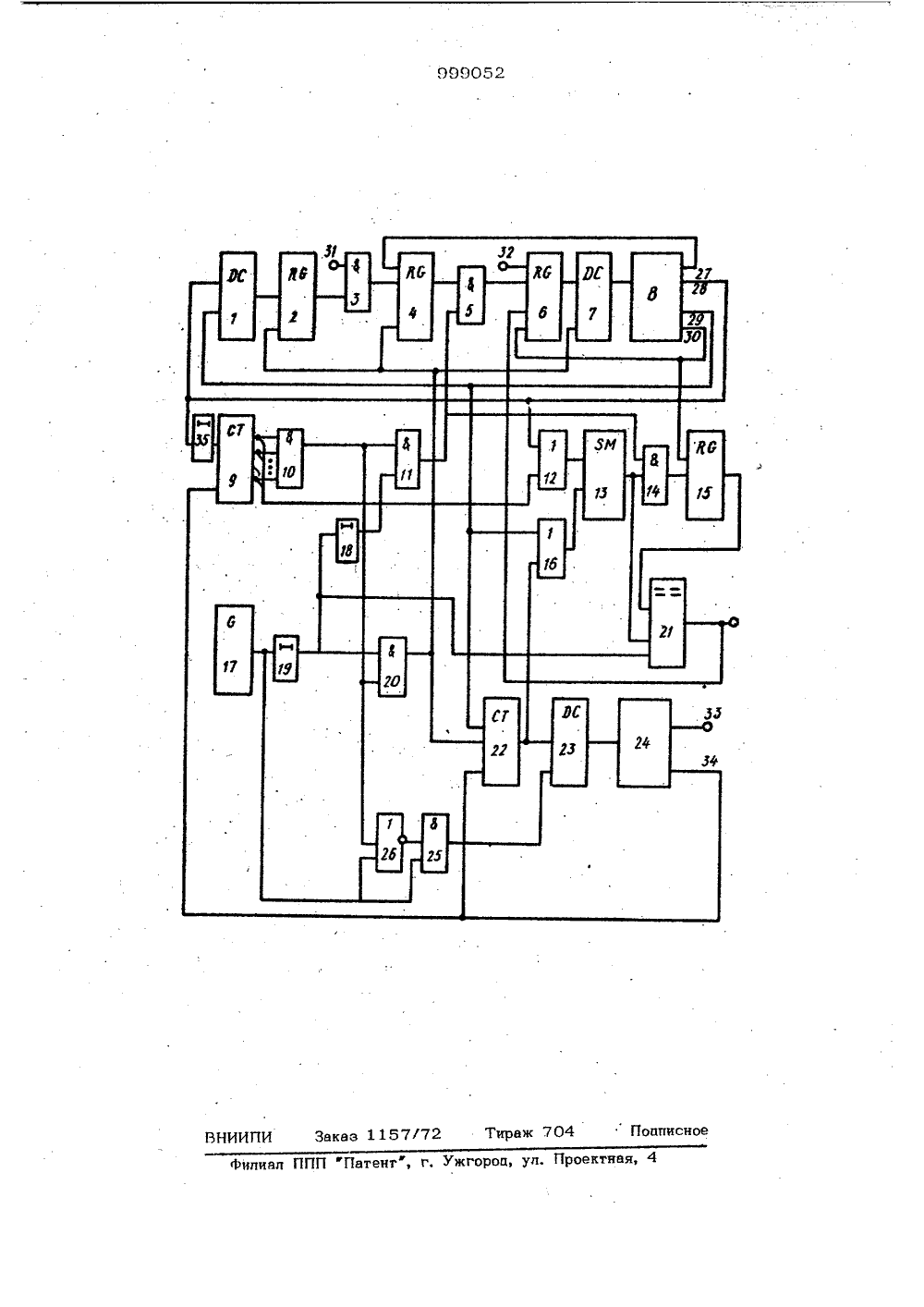

ОП ИСАЙИ ЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 1999052 Со 1 оз Советск ихСоциалистическихРеспублик.(088.8) де аевам взфбретевк и фтермтийДата опубликования описания 25.02.83.Самарский, ВС.Харченко, Г. Н,Чимонькин и"С Я 1"Тка енк1 ЪА . зт1 С,, рЮЪ Заявител 4) МИКРОПРОГРА СТРОИСТВО ЛЕНИЯ 15 тва являет-роля праэтого устро ивность ко Изобретение относится к вычислитель.ной технике и может быть использовано . при построении самоконтролируемых устройств управления микропрограммных ЭВМ и других систем.5Известно устройство. микропрограммного управления, содержащее два запоминающих блока, регистры, логические элементы И,ИЛИ, элементы задержки, дешифрую торы счетчики адресов микрокоманд, 1 о генератор тактовых импульсов 1 1 1,Недостатком этого устройства .являепся .низкая достоверность функционирования, обусловленная отсутствием контроля правильности его функционирования.Известно также микропрограммное устройство управления, содержащее два запоминающих блока, регистры, логическт, элементы И, ИЛЦ, элементы задержки, дешифраторы, два счетчика микрокоманд 20и счетчик адреса, генератор тактовых импульсов 2 3.Недостатком йс ся низкая операт нт 2вильности его функционирования, обусловленная организацией контроля правильнос. ти выполнения микропрограммы на уровне линейных последовательностей.Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому изобретению является микропрограммное устройство управления, содержащее генератор импуль сов; последовательно соединенные первый блок элементов И, регистр адреса, первый дешифратор и первый запоминающий блок, первый выход которого соединен с первым входом буферного регистра, вто- рой выход - с первыми входами,.счетчика микрокоманд и дешифратора логичеоких условий, выход которого соединен с первым входом регистра логических условий, выход счетчика микрокоманд через последовательно соединенные первый и второй элементы И соединен с вторым входом второго блока элементов И, третий выход первого запоминающего блока соединен с втотым входом дещифратора ло3 99905гических условий и первым входом счетчика адреса, выход которого соединен с первым входом второго дешифратора,а входустановки нуля соединен с вторыми входамипервого дешифратора и регистра логических условий, выход которого соединен спервым вхоцом первого блока элементовИ, а также с третьим входом буферногорегистра и выходом третьего элемента И,первый вход которого соединен с выходом 10первого элемента И, а через первый эле.мент НЕ соединен с первым входом четвертого элемента И, выход которого соединенс вторым выходом второго дешифратора.,выход которого соединен с входом второго запоминающего блока, первый выходкоторого соединен с выходом устройства,а второй выход - соединен с вторымивходами счетчиков мшсрокоманд и адреса, второй вход третьего элемента Ичерез второй элемент задержки соединенс вторым входом четвертого элемента Ии выходом генератора импульсов, а через первый элемент задержки - с вторымвходом второго элемента И, четвертыйвыход первого запоминающего блока соединен со входом "Установки.в нуль" регистра адреса 3,Недостатком этого устройства является низкая достоверность функционированияобусловленная отсутствием контроля правильности выполнения данной микрокоманды микропрограммы. В указанном устройстве отказ в любом из функциональных бпоксвможет привести к искажению выполняемой35микропрограммы.Целью изобретения является увеличение разрешающей способности контроляза счет фиксации ошибок в момент ихвозникновения,Поставленная . цель достигается тем,что в микропрограммное устройство управления, содержащее первый и второйблоки памяти, первый и второй дешифраторы адреса, дешифратор логических ус 45повий, счетчик адреса, счетчик микрокоманд, регистр логических условий, регистр адреса, буферный регистр, генератор импульсов, первый и второй элементызадержки, элемент НЕ, первый и второйблоки элементов И, первый, второй, тре 50тий и четвертый элементы,И, причемвход кода операции устройства соединенс первым информационным входом регистра адреса, выход которого соединенс информационным входом первого дешифратора адреса, выход первого дешифратора адреса соединен с вхоцом первогоблока памяти, адресный выход которого 4соединен с первым информационным входом буферного регистра, выход числа микрокоманд первого блока памяти соединен с первым информационным входом дешифратора логических условий, выхоц которого соединен с информационным входом регистра логических условий, выход начального адреса первого блока памяти соединен с вторым информационным входом цешифратора логических условий и информационным входом счетчика адреса, выход которого соединен с информационным входом второго дешифратора адреса, управляющий выход первого блока памяти соединен с установочным входом регистра адреса, выход второго дешифратора адреса соединен с входом второго блока памяти, информационный выход которого является выходом микроопераций устройства, управляющий выход второго блока памяти соединен с счетными входами счетчика адреса и счетчика микрокоманд, выходы которого соединены с входами первого элемента И, выход первого элемента И соединен с первым входом второго элемента И, первым входом третьегоэлемента И, и через элемент НЕ с первым входом четвертого элемента И, генератор импульсов соединен с вторым входом четвертого элемента И и через первый элемент задержки с входом второго элемента задержки и вторым входом третьего элемента И, выход которого соединен с управляющим входом первого дешифратора адреса и с установочными вхоцами счетчика с адрьса, буферного регистра и регистра логических условий, выход второго элемента задержки соединен с вторым входом второго элемента И,.выход которого соединен с первым входом первого блока элементов И, выход четвертого элемента И соединен с управляющим входом второго Вэшифратора адреса, выход регистра логических условий соединен с первым входом второго блока элементов И, выхоц которого соецинен с вторым информационным входом буферного регистра, выход буферного регистра соединен с вторым входом первого блока элементов И, выход которого соединен с вторым информационным входом регистра адреса, второй вход второго блока элементов И является входом логических условий устройства, дополнительно введены сумматор, регистр признака, блок сравнения, первый и второй блоки элементов ИЛИ,третий блок элемен тов И и третий элемент задержки, причем выход числа микрокоманд первого блока9990памяти соединен с первым входом первого блока элементов И и с входом треть его элемента задержки, выход которого соединен с информационным входом счетчика микрокоманд, выходы счетчика мик рокоманд соединены с вторыми входами первого блока элементов ИЛИ, выход которого соединен с первым входом сумматора, выход начального адреса первого блока памяти и выход счетчика адреса соединены соответственно с первым и вторым .входами второго блока элементов ИЛИ, выход которого соединен с вторым входом сумматора, управляющий выход первого блока памяти соединен с устано вочньМ входом регистра признака, выход которого соединен с первым информационным входом блока сравнения, выход второго элемента И соединен с первым входом третьего блока элементов И, выход, 20 которого соединен с информационным входу регистра признака, выход сумматора соединен с вторым входом третьего блока элементов И и вторым информационным входом блока сравнения, выход которого . 25 является выходом сигнала ошибки устройства и соединен с установочным входом регистра адреса, выход первого элемента задержки соединен с управляющим входом блока сравнения. 30 Сущность изобретения состоит в повышении достоверности функционирования микропрограммного устройства управленияпутем использования естественной инфор- З 5 мационной избыточности за счет организации контроля правильности реализации функций, переходов путем сравнения требуемого значения контрольного признака линейной последовательности микрокоманд И с его фактическим значением в каждом такте считывания операционных микрокомана, однозначно определяемом состоянием счетчиков адреса и микрокоманд.формирование требуемого контрольного признака происходит путем суммирования кода числа й ( М; - количество микро- команд в линейной последовательности Ь;) и кода числа А(А - адрес первой микрокоманды в 1 -ой линейной последова 56 тельности).Таким образом, для микропрограммы, состоящей изразличных линейных последовательностей, формируетсяразпиг ных контрольных признаков. Каждый кон 55 трольный признак. позволяет инденти 3фицировать соответствующую линейную последовательность с точностью до значения суммы ее параметров. 52 4формирование фактического значенияконтрольно 1.о признака в процессесчиты- вания онерационных микроксьанд из второго. запоминающего блока происходитпутем суммирования содержелого счетчиков адреба и микроюмаийПри. этом независимо от адреса считываемой микро- команды У Е Ь и количества уже реализованных микрокоманд в линейной последоватепьиоств; значение Ядолжно быть величиной постоянной и ври прайщпнОм функционировании микропрограммаого устройства управления должно выполняться условие Выполнение. этого условия свщетевьствует о правильности реайизайии в микропрограммном устройстве управленИя функций переходов. В противном случае условие (1) не выполняется. Следоцатепьно,предлагаемая процедура контроля основана на использовании для проверки функционирования естественной информационнойизбыточности, что позволяет вводить вустройство минимальный объем средствпроверки.На чертеже представлена функциональная схема микропрограммного устройства управления,Устройство содержит дешифратор 1 логических условий, регистр 2 погическихусловий,второй блок 3 элементов И, .буферный регистр 4, первый блок 5 элементов И, адресный регистр 6, первыйдешифратор 7 адреса, первый блок 8 памяти, счетчик 9 микрокоманд, первыйэлемент И 10, второй элемент И 11,первый блок 12 элементов ИЛИ, сумматор 13, третий блок 14 элементов И,регистр 15 признака, второй блок 16элементов ИЛИ, генератора 17 импульсов и второй элемент 18 задержки, первый элемент 19 задержки, третий элемент И 20, блок 21 сравнения, счетчИк22 адреса, второй дешифратор 23 адреса, второй блок 24 памяти, элемент НЕ25 и четвертый элемент И 26, адресныйвыход 27, выход 28 числа микрокомиид,выход 29 начального адреса и управляющий выход 30 первого блока 8, вход 31логических условий устройства, вход 32кода операций устройства, информационный33 и управляющий выходы 34 второгоблока 24, соответственно, третий элемент 35 задержки.В первый блок 8 памяти записываютсяадресные микрокоманды, которые вкпюча52 .8ферного регистра 4, регистра 2 логичеоких условий, счетчика 22 адреса, а также открывает дешифратор 7. С выхода 30 первого запоминающего блока 8 в, буферный регистр 4 записывается косвенный адрес первой микрокоманды очередной линейной последовательности, с выхода 31 в счетчик микрокоманд 9 через второй блок элементов ИЛИ 12 в сумматор 13 подается код числа микро- команд в выполняемой линейной последовательности, С выхода 32 запоминающего блока 8 .в сумматор 1 3 через блок элементов ИЛИ 16 поцается код адреса первой микрокоманды текущей линейной последовательности. Этот же, коц запишется в счетчик 22 адреса. В сумматоре 1 3 происходит формирование контрольного признака ;, который поступает на входы блока 14 элементов И и узла 21 сравнения. Через блок 14 элементов И контрольный признак запишется в регистр 15 и далее поступит на блок 21 сравнения. После записи информации в счетчик 9 его содержимое станет отличным от нуля и на выходе элемента И 10 появится нулевой сигнал, который закроет элемент И 11. Нулевой сигнал с выхода этого элемента закроет блок 14 элементов И, Нулевым сигналом .с выхода элемента И 10, инвертируемым элементом НЕ 25, откроется четвертый элемент И 26.Очередной тактовый импульс с выхода генератора 17 через открытый элемент И 26 произведет считывание информации из .запоминающего блока 21. финичным сигналом с управляющего выхода 34 произойдет увеличение (уменьшение) содержимого счетчиков адреса 22 и микрокоманд 9 на единицу. Коды с: выходов этих счетчиков поступят соответственно на входы блоков 16 и 12 элементов ИЛИ и в сумматоре 13 произойдет формирование значения контрольного признака. Я. , который поступит на вход узла 21 сравнения. По. сигналу с выхода элемента 19 задержки в узле 21 сравнения произойдет сравнение соответствующих кодов.В случае их совпадения, что свидетель ствует о правильной реализации функции переходов микропрограммным устройством управления, на выхбде узла 21 сравнения сигнал будет отсутствовать и очередным тактовым .импульсом произойдет считывание информации из второго блока 24, В дальнейшем, в случае .правильной реализации последовательности, после считывания последней операционной микрокоманды из 7 9990ют адрес первой микрокоманды текущейлинейной последовательности, которыйсчитывается с входа 32; косвенный адресмикрокоманды операционной линейной по-следовательности, который считывается с 3выхода 30; код числа микрокоманд, входящих в линейную последовательность,который считывается -с входа 31.Во втором блоке 24 записаны операционные микрокоманды, входящие в микроподпрограммы (линейные последовательности), образующие микропрограммы,После считывания информации из первого запоминающего блока 8 о косвенномадресе очередной микрокоманды, адресе фпервой микрокоманцы текущей последовательности, а также о коде числа микрокоманд, входящих в реализуемую линейную последовательность происходит формирование требуемого значеция контрольногопризнака Я , в сумматоре 13 и запись его в регистр 15 для дальнейшегохранения.В процессе реализации микропрограммы при считывании каждой операционной 25микрокоманды из второго запоминающегоблока происходит формирование фактического значения контрольного признака всумматоре 13. При этом независимо отномера и адреса микрокоманды в соот, ветствующей линейной последовательности, фактическое значение контрольногопризнака остается неизменным в случаеправильной реализации микропрограммы.Требуемое и фактическое значения контрольного признака сравнивается узлом21 сравнения. В случае их равенства вмикропрограммном устройстве управления происходит считывание очереднойоперационной микрокоманцы из второгоблока 8 памяти и т.д,В случае несовпадения значений Е: иЕ; сигналом с выхода узла сравненияпроисходит автоматическое отключениемикропрограммного устройства управления от реализации заданной микропрограммы и начинается реализация диагностической микропрограммы путем записификсированного адреса в регистр 6.М икропрограммное устройство управления работает следующим образом,В исходном состоянии все элементыпамяти обнулены, Код операции поступает на вход регистра 6 и задает адрессоответствующей ячейки памяти в блоке 8.ЯПервый импульс генератора 17 черезэлемент 19 задержки и открытый элементИ 20 производит установку в нуль бу9 9990 Микропрограммное устройство уцравле ния, содержащее первый и второй блоки памяти, первый и второй дешифраторы адреса, дешифратор логических условий, счетчик адреса, счетчик микрокоманд, регистр логических условий, регистр адреса, буферный регистр, генератор иь-, пульсов, первый и второй элементы задержки, элемент НЕ, первый и второй блоки элементов И, первый и второй, третий и четвертый элементы И, причем вход кода операции устройства соединен с первым . информационным входом регистра адреса, выход которого соединен с информационным входом первого дешифратора адреса, выход первого дешифратора адреса соединен свходом первого блока памяти, адресный выход которого соединен с первым информационным входом буферного регистра, выход числа микрокоМанд первого блока памяти соединен с первым инфор . мационным входом дешифратора логических условий, выход которого соединен с информационным входом регистра логичвоких условий, выход начального адреса .первого блока памяти соединен с вторым информационным входом дешифратора логических условий и информационным входом счетчика адреса, выход которого сое динен с информационным входом второго дешифратора ацреса, управляющий выход первого блока памяти соединен с установочным входом регистра адреса, выход второго дешифратора адреса соединен с входом второго блока памяти, информа ционный выход которого является выходом .микроопераций устройства, управла 4 ющий выход второго блока памяти сое динен с счетными входами счетчика адреса и счетчика микрокоманд, выходы которого соединены с входами первого элемента И, выход первого элемента И сое: динен с первыми входами второго, треть- его и четвертого элементов И, выходгенератора импульсов - с вторым входом четвертого элемента И и через первый элемент задержки - с входом второго элемента задержки и вторь 1 м входом тре тьего элемента И, выход которого соединен с управляющим .входом первого дешифратора адреса и с установочными входами счетчика адреса, буферного регистра и регистра логических условий,второго блока 24 произойдет обнулениесчетчика 9 микрокоманд и на выходе элемента И 10 появится единичный сигнал,который откроет элемент И 11. Тактовымимпульсом с выхода генератора 17, проходящим через элементы 19 и 18 задержки и элемент И 11, произойдет записьадреса следующей адресной микрокомандылинейной последовательности через открытый блок 5 элементов И.в адресный ре3гистр 6. Тактовым импульсом с выходагенератора 17 через элемент 19 задержки и элемент И 20 произойцет обнуление счетчика 22 адреса, регистров 2 и 4,а также запуск дешифратора 7. При,счи- Зтывайии информации из блока 8 сигналомс выхода 30 произойдет обнуление регистра 15 и подготовка его для записи оче-,редного значения контрольного признакаУ1. В дальнейшем работа устройства . 20будет протекать аналогично описанной выше,Рассмотрим работу микропрограммногоустройства управления при возникновенииотказов во время считывания микрокоманд 23Отказы такого рода могут возникнутьлибо в счетчике 9, либо в счетчике 22,непосредственно участвующих в реализации функпий переходов.При возникновении.отказов в указенныхщблоках блок 21 сравнения фиксирует вы полнение условия У ф. н на его выходе появляется единичный сигнал, кото-.Рый поступает на.вход адресного регистра 6, прекращая выполнение заданноймикропрограммы и задавая фиксированныйадрес первой микрокоманды диагносте.ческой микропрограммы.Кроме того, в микропрограммном устройстве управления организуется конероль правильности функционирования такихузлов схемы контроля как сумматор 13,регистр 15, Отказ в любом из этих блоков приводит к выполнению условия иобуславливает воэможность самоконтролясредств проверки микропрограммного устройства управления.Таким образом, в предлагаемом микроцрограммном устройстве управления осуществляется контроль правильности реализации функции переходов, что позволяет повысить достоверность функционирования микропрограммного устройства уп-,равления, Кроме того, в предлагаемомустройстве средства контроля обладаютИнекоторыми возможностями для самопроверки.Использование предлагаемого изобретения позволяет строить самоконтролиру 52 10юшке микропрограммные устройства с высокой достоверностью функционирования. Формула изобретениявыход второго элемента задержки соединен с вторым входом второго элемента И, выход которого соединен с первым . входом первого блока элементов И, выход четвертого элемента И соединен через элемент НЕ с управляющим входом второго дешифратора адреса, выход регистра логических условий соединен с первым входом второго блока элементов И, выход которого соединен с вторым инфор мационным входом буферного регистра, второй вход второго блока элементов И является входом логических условий устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения разрешающей 5 способности контроля за счет фиксации ошибок в момент их возникновения, в него введены сумматор, регистр признака, блок сравнения, первый и второй блоки элементов ИЛИ, третий блок элементов 20 И, третий элемент задержки, причем выход числа микрокоманд первого блока памяти соединен с первым входом первого блока элементов И и с входом третьего элемента задержки, выход которого сое динен с информационным входом счетчика микрокоманд, выходы счетчика микрокоманд соединены с вторыми входами первого блока элементов ИЛИ, выход которого соединен с первым входом сумматора,выход начального адреса первого блока памяти и выход счетчика адреса соединены соответственно с первым и вторымвходами второго блока элементов ИЛИ,выход которого соединен с вторым входомсумматора, управляющий выход первогоблока памяти соединен с установочнымвходом регистра признака, выход которогосоединен с первым информационным входом блока сравнения, выход второго элемента И соединен с первым входом третьего блока элементов И, выход которогосоединен с информационным входом регистра признака, выход сумматора соединен с вторым входом третьего блокаэлементов И и вторым информационнымвходом блока сравнения, выход которогоявляется выходом сигнала ошибки устройства и соединен с установочным входомрегистра адреса, выход первого элементазадержки соединен с управляющим входом блока сравнения,Источники информации,принятые во внимание при экспертизе 1, Авторское свидетельство СССР Мц 482744, кл. ( 06 Г 9/16, 1974. 2. Авторское свидетельство СССР Мо 849891, кл, С, 06 Р 9/16, 1981 3. Авторское свидетельство СССР М 703811, кл. С, 06 Г 9/16, 1981

СмотретьЗаявка

3310255, 02.07.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ

САМАРСКИЙ ВИКТОР БОРИСОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.02.1983

Код ссылки

<a href="https://patents.su/7-999052-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для выполнения команд реализации систем многоместных логических функций

Следующий патент: Устройство для выполнения условного перехода

Случайный патент: Загрузочное устройство