Устройство для вычисления функции =2

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

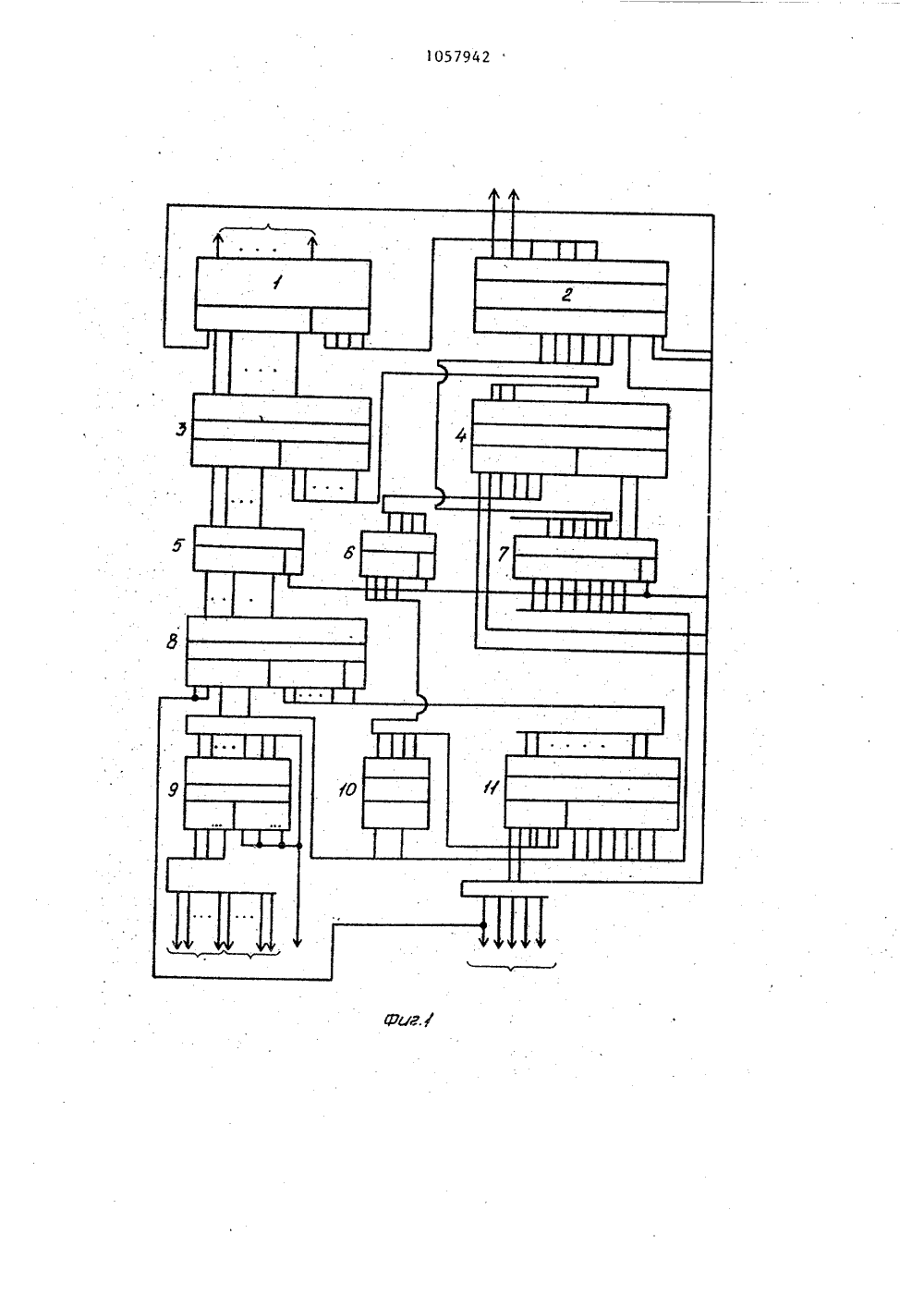

(9 0 52 ГО ПИСАНИЕ ИЗОБРЕТЕНИЯ СКОМУ СВИ К(прототип). ельство ССС52, 1978.ьство СССР52, 1978 ДАРСТВЕННЫЙ НОМИТЕТ СССРЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯФУНЩИИ у=2 , содержащее три регистра, первый сумматор, первый блокпамяти, блок управления и сдвигатель, причем выход первого сумматорасоединен с информационным входом первого регистра, о т л и ч а ю щ е -е с я тем, что, с целью повышениябыстродействия, в него введены дешиФратор, второй блок памяти, группа сумматоров по модулю два и второй сумматор, причем блок управления содержит три элемента И, дваэлемента НЕ, два элемента ИЛИ, двасумматора и группу сумматоров помодулю два, выходы которых соединены с первой группой входов первого сумматора, первый, второй и четвертый разряды второй группы входовкоторого соединены с выходом первогоэлемента НЕ и первыми входами сумматоров по модулю два группы, вторыевходы которых соединены с выходамивторого сумматора, первый и третийразряды первой группы входов которого соединены с выходом яервого элемента ИЛИ, входы которого соединеныс выходами первого и второго элементов И и второго элемента НЕ, выход которого соединен с первым входом,второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выходы элементов ИЛИ соединены с выходом признака масштабирования устройства, вход первого элемента НЕ соединен с выходом знака второго регистра, вход задания знака устройства соединен с вторым и четвертым разрядами первой группы входов второго сумматора и третьим разрядом второй группы входов первого сумматора блока управления, первые входы элементов И и вход второго элемента НЕ соединены с первым входом задания режима уст-ройства, второй вход задания режима которого соединен с вторыми входами элементов И, первый выход второго регистра соединен с третьим входом первого элемента И и первым разрядом второй группы входов второго сумматора блока управления, второй разряд второй группы входов которого соеди юв нен с вторым разрядным выходом вто- ( рого регистра, четвертым входом пер- д вого и третьим входом второго элемен. тов И, пятый и четвертый входы которых соединены соответственно с тре тьим и четвертым разрядными выходами второго регистра и третьим и четвертым разрядами второй группы входов второго сумматора блока управления, пятый разрядный выход второго регистра аргумента устройства соединен с третьим входом третьего элемента И, входы мантиссы и порядка аргумента устройства соединены с первыми входами сумматоров по модулю два группы, вторые входы которых соединены с входом знака аргумента1057942 30 устройства, выходы сумматоров по модулю два группы соединены с первыминформационным входом первого блокапамяти и информационным входом второго регистра., входы синхронизациивсех регистров соединены с входомтактовых импульсов устройства, выходдешифратора соединен с информаци- .онным входом третьего регистра ивторым информационным входом первого блока памяти, третий информационный вход которого соединен с входомзадания знака устройства и первыминформационным входом второго блокапамяти, выход первого блока памятисоединен с первой группой входовпервого сумматора, входы младшихразрядов второй группы которого сое,динены с выходами сумматоров по модулю два группы, входы старших раз- .,Устройство относится к вычислительной технике и может быть использовано в цифровых устройствах фильтрации сигналов.Известно устройство для вычисления показательных функций, содержащее регистр аргумента, накопитель, состоящий из й сдвигающих регистров, блок умножения, (и+1) элементов И и блок выборки информации, выходы блока управления соединены с входами блока умножения, входами управления сдвигакпцих регистров накопи. теля, входом блока выборки информации, выходы блока выборки соединены с входами блока умножения, входы сдвигающих регистров являются входами усъройства, а выходы через. элементы И соединены с входами блока выборки 1) .Недостатком устройства является ограниченное быстродействие, обусловленное последовательным рекурсивным методом выполнения вычисли" тельных операций.Наиболее близким по технической сущности к предлагаемому является устройство для возведения в степень, содержащее регистр операнда, регистры промежуточных и окончательных результатов, сумматор, блок управрядов второй группы первого сумматора соединены с входом задания знака устройства, выход первого регистра соединен с первой группой входоввторого сумматора, вторая группавходов которого соединена с выходомвторого бпока памяти, второй информационный вход которого соединен с выходом третьего регистра третий информационный вход второго блока памяти соединен с выходом второго регистра, выход второго сумматора соединен с информационным входом младших разрядов .сдвигателя, вход старшего разряда которого соединен свходом задания знака устройства, уп, равляющий вход сдвигателя соединенс выхода первого сумматора блока управления,выход сдвигателя соединен с выходом кода результата устройства. 2 ления, причем входы регистров проме жуточных результатов подключены квыходам сумматора, первая группа входов которого подключена к выходамрегистров промежуточных результатов,первый выхоп блока управления нодключен к управляющим входам сдвига регистров окончательных и промежуточных результатов, счетчик, сдвига- щО тель, распределитель сигналов, кодопреобразов,атель и .триггеры цифр результатовв, выходы счетчика подключены к входам регистров окончательных результатов, выходы которых под ключены к входам счетчика, а такжек входам сдвигателя, вторая группавходов сумматора подключена к выходамрегистра операнда, а третья группавходов - к выходам сдвигателя, выхо 2 О ды прямых и инверсных значений трех старших разрядов сумматора подключены к входам кодопреобразователя,первый и второй входы которогО соединены с входами первого и второго триггеров цифр результата, другие входы которых подключены к первому выходу блока управления, входы которого соединены с выходами триггеров цифр результата, а также с управля-. ющими входами счетчика и регистраоперанда, выхоДы распределителя сигйалов подключены к входам младшихразрядов регистра операнда и к управляющим входам сдвигателя, входныешины устройства подключены к управляющим входам сдвигателя и регистра 5операнда, второй выход блока управления соединен с управляющими входа"ми регистра операнда и распределителя сигналов, остальные 2 выходовблока управления подключены к выход Оным шинам устройства 2,20 50 Недостаток известного устройствазаключается в ограниченном быстродей-.ствии, обусловленном последовательным рекурсивным характером вычислений,Цель изобретения - повышение быстродействия.Поставленная цель достигаетсятем, что в устройство для вычисления функции у=2", содержащее трирегистра, первый сумматор, первый.блок памяти, блок управления и сдвигатель, причем выход первого сумматора соединен с информационным входомпервого регистра, дополнительно введены дешифратор, второй блок памяти,группа сумматоров по модулю два ивторой сумматор, причем блок управ"30ления содержит три элемента И, дваэлемента НЕ, два элемента ИЛИ, двасумматора и группу сумматоров по модулю два, выходы которых соединеныс первой группой входов первогосумматора, первый, второй и четвер 35тый разряды второй группы входов ко-,торого соединены с выходом первогоэлемента НЕ и первыми входами сумматоров по модулю два группы вто.40рые входы которых соединены с выходами второго сумматора, первый и тре"тий разряды первой группы входов которого соединены с выходом первогоэлемента ИЛИ, входы которого соеди 45нены с выходами первого и второгоэлементов И и второго элемента НЕ,выход которого соединен с первым входом второго элемента ИЛИ, второйвход которого соединен с выходомтретьего элемента И, выходы элементов ИЛИ соединены с выходом признака масштабирования устройства, входпервого элемента НЕ соединен с выходом знака второго регистра, вход задания знака ус-ройства соединен свторым и четвертым разрядами первойгруппы входов второго сумматора итретьим разрядом второй группы входов первого сумматора блока управления, первые входы элементов И и входвторого элемента НЕ соединены с первым входом задания режима устройства, второй вход задания режима которого соединен с вторыми входамиэлементов И, первый вход второго регистра соединен с третьим входомпервого элемента И и первым разрядом второй группы входов второго сумматора блока управления, второй разояд второй группы входов которогосоединен с вторым разрядным выхо-.дом второго регистра, четвертымвходом первого и третьим входом второго элементов И, пятый и четвертыйвходы которых соединены соответственно с третьим и четвертым разрядными выходами второго регистра итретьим и четвертым разрядами второй группы вхоДов второго сумматора блока управления, пятый разрядный выход второго регистра аргумента устройства. соединен с третьимвходом третьего элемента И, входымантиссы и порядка аргумента уст"ройства соединены с первыми входами сумматоров по модулю два группы,вторые входы которых соединеньг свходом знака аргумента устройства,выходы сумматоров по модулю два груп"пы соединены с первым информационным входом первого блока памяти иинформационным входом второго регистра, входы синхронизации всех регистров соединены с входом тактовыхимпульсов устройства, выход дешифратора соединен с информациЬнным вхо.дом третьего регистра и вторым информационным входом первого блокапамяти, третий информационный входкоторого соединен с входом заданиязнака устройства и первым информационным входом второго блока памяти,выход первого блока памяти соединенс первой группой входов первого сумматора, входы младших разрядов второйгруппы которого соединены с выходами сумматоров по модулю два группы,входы старших .разрядов второй группыпервого сумматора соединены с входом задания .знака устройства, выходпервого регистра соединен с первойгруппой входов второго сумматора,вторая группа входов которого соединена с выходом второго блока памяти, второй информационный вход которого соединен с выходом третьегорегистра, третий информационный1057942 Таблица 1 Я заключающаяся в том, что если порядокчисла превышает определенную величину.то для управления сдвигателем используется значение порядка, уменьшенноеиа эту величину, а на специальном вы" ходе устройства вырабатывается сигнал-признак масштабирования,Масштабирование и выработка кодаупрайления сдвигателем производится в блоке 2 управления. Предусматривается два режима масштабирования - автоматический и принудительный, эаьдаваемые с помощью управляющих сиг,налов у,1 и у, подаваемых на первый и второй входы управления устрой.ством. На первом и втором информационных выходах блока 2 управления при этом вырабатывается соответстПогрешностьвычнслений ачеМ,090 0,0 Таб Режим масштабирования Значение ков масш Операция Значения риэна- бирова авляющи игналов У 1 томатический ринудительный Уменьшение (П)на 11 Уменьшенина 16 Уменьшенина 27 0 7ряде, и умножении его на 2 п,где и порядок (целочисленная часть) кода Х. Такое умножение эквивалентно объемному сдвигу 1 вправо или влево) в зависимости от знака кода Х, сформированного кода на Ю разрядов. Так как порядок числа Х представляется 5"ти разрядным кодом, что с учетом знака для непосредственного выполнения этой операции требует наличия большого количества информационных выходов у сдвигателя 1, .Для сокращения числа выходов сдвигателя 1 используется техника масштаби овани венно первый н второй сигналы-признаки масштабирования Г и Гу.Значения сигналов для различныхрежимов масштабирования приведеныв табл. 2.Таким образом, введение в уст-ройство новых элементов и связей позволило повысить скорость вычислений.В устройстве исключена длинная опе О рация умножения, ограничивающая про"изводительность устройства-прототи-.па.арственного к иэобретеиий иЖ, Раушс Подписноеитета СССРткрытийя наб д, 4

СмотретьЗаявка

3352442, 02.07.1981

ПРЕДПРИЯТИЕ ПЯ В-8117

ХАСКИН ЮРИЙ АБРАМОВИЧ, ГАЙДАЙ ДМИТРИЙ ФЕДОТОВИЧ, ЛУКЬЯНЧУК ИГОРЬ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, функции

Опубликовано: 30.11.1983

Код ссылки

<a href="https://patents.su/7-1057942-ustrojjstvo-dlya-vychisleniya-funkcii-2.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции =2</a>

Предыдущий патент: Сумматор по модулю три

Следующий патент: Устройство для возведения в квадрат импульсных сигналов

Случайный патент: Устройство для перемещения зданий