Устройство для умножения десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1016780

Авторы: Кожемяко, Короновский, Мартынюк, Тимченко

Текст

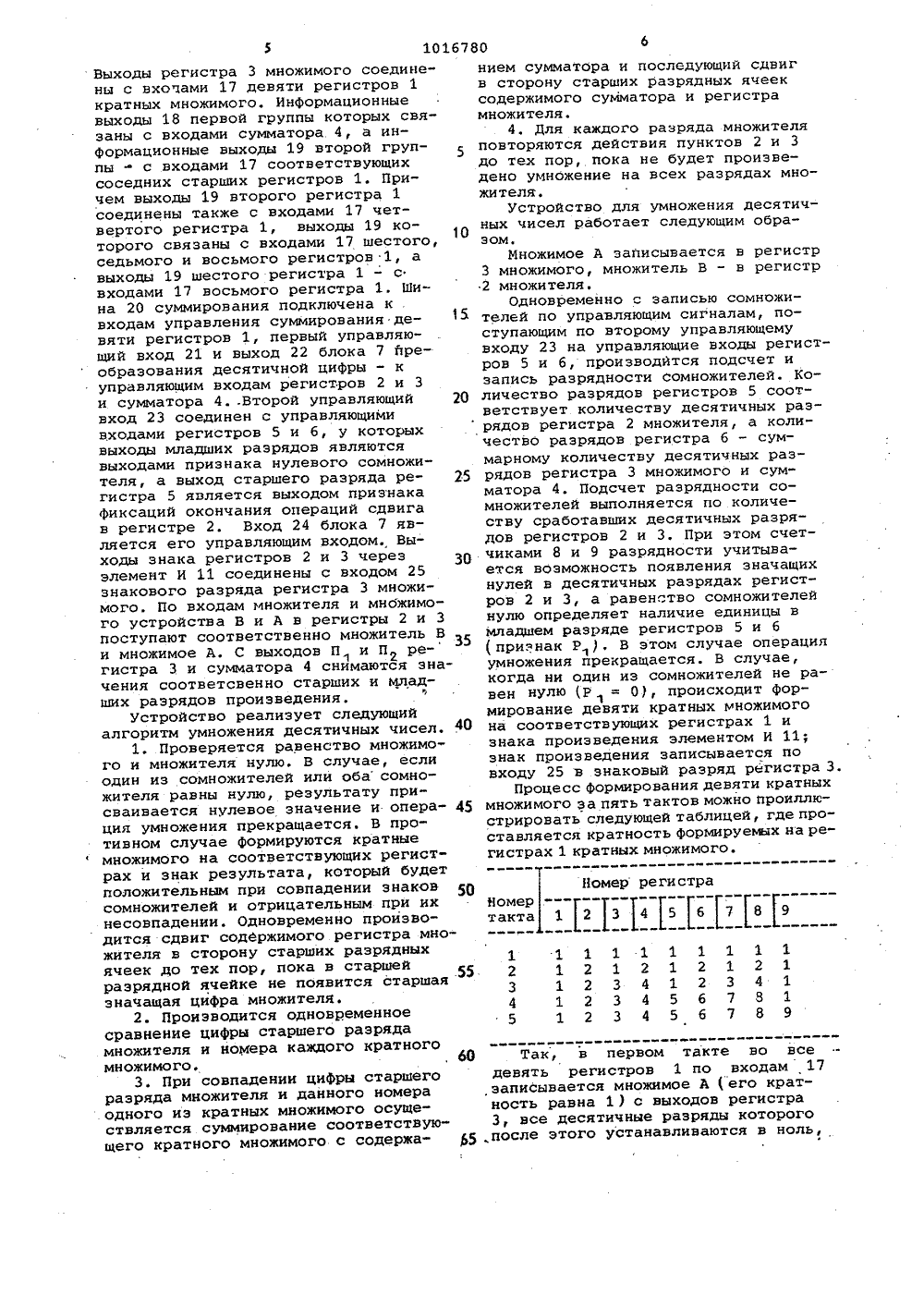

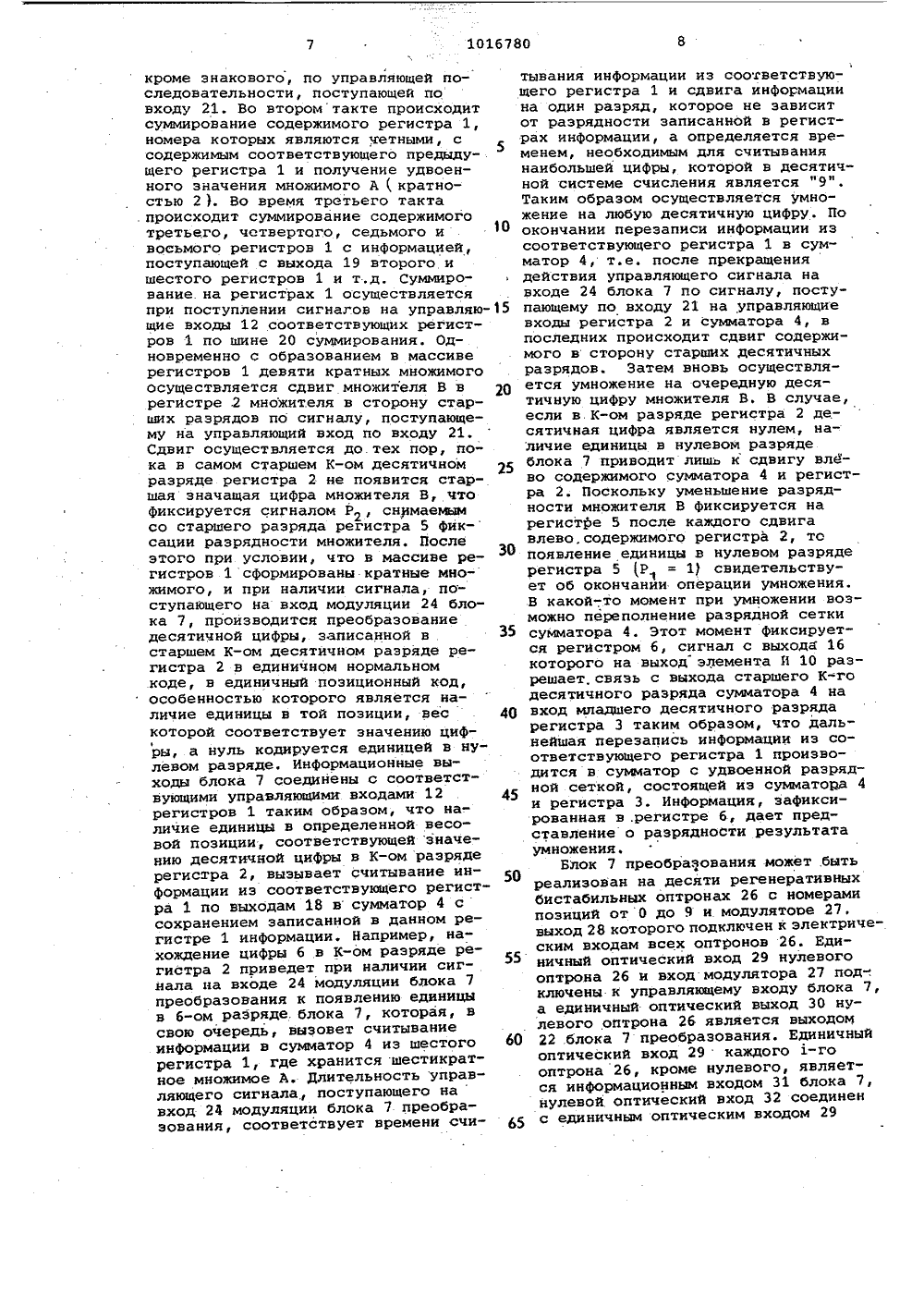

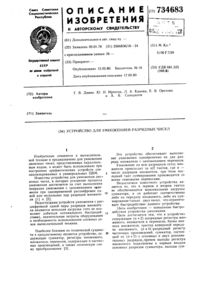

СОКО СОшЕТСНИШЭВЛКИИЯИХРЕСПУБЛИК 06 Р 7/49 ТЕНИ ЗОБР ТОРСНОМУ СВ В 17 Т.Б. Мартынюк,и Л.И. Тимченколитехнический инюл ко 3,ГОСУДАРСТВЕННЬЙ КОМИТЕТ СССРПО ДЕЛАЮ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИ(56) 1. Авторское свидетельство СССР В 652560, кл.06 Г 7/39, 1979.2.Кожемяко В.П, и др. О реали-. зации алгоритмов умножения и вычитания десятичных чисел на оптоэлектронных сумматорах, - Известия вузов. Приборостроение, 1976, 9 с. 62-65 (прототип).(54)(57) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее регист множителя, регистры кратных миожнмо го и сумматор, о т л и ч а ю щ ее с я тем, что, с целью повышения однородности устройства и сокращения аппаратных затрат, оно содержит регистр множимого, блок преобразо-. вания десятичной цифры из единичного нормального в единичный позицйонный код, два счетчика разрядности, регистр фиксации разрядности множителя,. регистр фиксации разрядности множимого и произведения и два элемента И, причем информационные входы регистров множителя и множимого подключены к соответствующим входам множителя и множимого устройства, выходы старшего десятичного разряда регистра множителя соединены с соответствующими информационными входами блока преобразования десятичной цифры иэ единичного нормального в единичный позиционный код, управляющий вход которого подключен к входу модуляции. устройства, информационные выходы блока преобразования десятичной цифры из единичного801016780 А нормального в единичный позиционный код подключены к соответствующим управляющим входам регистров крат.ных множимого, а управляющий выход блока преобразования десятичной. цифры из единичного нормального в единичный позиционный код - к первым управляющим входам регистров множителя и множимого и сумматора, вторые управляющие входы которых подключены к первому управляющему входу устройства, выходы всех десятичных разрядов регистра множителя подключены к соответствующим входам первого счетчика разрядности, выходы которого подключены к соответствующим информациониным входам регистра фиксации разрядности множителя, выход старшего разряда которого подключен к выходу фиксации окончания операции сдвига устройства, а выход младшего разряда - к выходу признака нулевого множителя устройства, выход знака регистра множителя.нодключен к первому входу первого элемента И, второй вход которого подключен к выходу знака реГистра.множимОГоу а выход к входу знака регистра множимого, выходывсех десятичных разрядов регистра множимого подключены к соответствующим входам первой группы второго .счетчика разрядности, входы второй группы которого подключены к выходам соответствующих десятичщюс разрядов сумматора, выходы .второго счетчика разрядности подключены к соответствующим информационным входам регистра фиксации разрядности миожимого и произведения, выход переполнения которого подключен к первому входу второго элемента И, второй,виод которого соединен с выходом старшего разряда сумматора, а выход - с входом младшего разряда регистра множимого, выход младшего разряда регистра фиксации разряд1016780 10 ности множимого и .произведения подключен к выходу признака нулевогомножимого устройства, управляющиевходы регистров фиксации разрядностимножителя, множимого и произведенияподключены к второму управляющемувходу устройства, выходы всех разрядов регистра множимого подключены,к соответствующим первым группам информационных входов регистров кратных множимого, вторая группа информационных входов 1-го (1=2,9)регистра кратных множимого, подключена к первой группе выходов(1 -1) -горегистра кратных множимого, выходыпервой группы второго регистра кратных множимого подключены к соответствующим информационным входам третьей группы четвертого регистракратных множимого, выходы первой 1Изобретение относится к вычислительной технике и может быть использовано в оптоэлектронных арифметических устройствах, выполняющих операции над десятичными числами с 5фиксированной запятой,Известно устройство для умножениядесятичных чисел, содержащее регистрмножителя, блок формирования множимого, сумматор, блок управления,первый выход которого соединен свходом управления регистра множителя, выход которого связан с входомблока управления, второй выход которого соединен с входом управлениясумматора, информационные входы которого соединены с информационнымивыхОдами блока формирования множимого, первый и второй входы управления которого соединены соответственно с третьим и четвертым выходами блока управления, информационные входы дополнительного регистра связаны с информационнымиВыходами младших тетрад блока формирования множимого, информационные входы старших тетрад которбгоподключены к выходам дополнительного регистра, к управляющему входукоторого подключен пятый вход блокауправления 1 3 30Умножение осуществляется за чис,ло циклов, равное разрядности десятичных операндов, при этом в каждом цикле осуществляется умножениемножимого на один десятичный разряд,множителя, начиная с младшего. Таким образом, к недостатку данногоустройства можно отнести значительное время, затрачиваемое на операцию умножения, поскольку каждый группы которого подключены к соответствующим информационным входамтретьей группы шестого, седьмого ивосьмого регистров кратных множимого, выходы первой группы шестогорегистра кратных множимого подключены к соответствующим информационным входам четвертой группы восьмогорегистра кратных множимого, выходывторых групп всех регистров кратныхмножимого подключены к соответствующим информационным входам сумматора,входы управления суммированием всехрегистров кратных множимого подключены к шине суммирования устройства,выхсды сумматора являются выходамимладших разрядов произведения устройства, а выходы регистра множимогоявляются выходами старших разрядов произведения устройства. цикл состоит из четырех тактов, по: числу разрядов представления десятичных цифр в двоично-десятичной системе 8-4-2-1,Наиболее близким к предлагаемому является устройство умножения десятичных чисел, содержащее регистр множителя, сумматор, восемь дополнительных регистров для хранения кратных множимого и девять схем сравнения, входы которых соединены с выходом младшего разряда регистра множителя и выходом разряда признака соответствующих регистров хранения кратных множимого, причем выходы девяти регистров хранения кратных множимого через соответствующие схемы сравнения подключены к входу сумматора. Выходы каждого регистра хранения кратных множимого, кроме девятого, соединены с входом следующего соседнего регистра 2 3.Недостатком такого устройства является необходимость использования девяти схем сравнения, а также последовательйое формирование девяти кратных множимого на соответствующих регистрах; что в .конечном счете ограничивает быстродействие оптоэлектронного устройства умножения.Цель изобретения - повышение однородности устройства для умножения десятичных чисел и снижение аппаратных затрат.Поставленная цель достигается тем, что устройство для умножения десятичных чисел, содержащее регистр множителя:, регистры кратных множимого и сумматор, содержит регистр множимого, блок преобразования десятичной цифры, счетчика раэрядности, регистр фиксации разрядности множителя, регистр фиксации разрядности множимого и произведения и два элемента И, причем информационные входы регистров множителя и множимого подключены ксоответствующим входам множителя и множимого устройства, выходы старшего десятичного разряда регистра множителя соединены с соответствующими информационными входами блока преобразования десятичной цифры иэ единичного нормального в единичный позиционный код, управляющий вход которого подключен к входу модуляции устройства, информационные выходы блока преобразования десятичной цифры иэ единичного нормального в единичный позиционный код подключены к соответствующим управляющим входам регистров .кратных множимого, а управляющий выход блока преобразования десятичной цифры иэ единичного нормального в единичный позиционный код - к первым управляющим входам регистров множимого и множителя и сумматора, вторые управляющие входы которых подключены к первому управляющему входу устройства, выходы всех десятичных разрядов регистра множителя подключены к соответствующим входам первого счетчика разрядности, выходы которого подключены к .соответствующим информационным . входам регистра фиксации разрядности множителя, выход старшего разряда которого подключен к выходу фиксации окончания операции сдвига устройства, а выход младшего разрядак выходу признака нулевого множителя устройства, выход знака регистра множителя подключен к первому входу первого элемента И, второй вход которого подключен к выходу знака регистра множимого, а выход - к входу знака регистра множимого, выходы всех десятичных разрядов регистра множимого подключены к соответствующим входам первой груп- пы второго счетчика разрядности, входы второй группы которого подключены к выходам соответствующих десятичных разрядов сумматора, выходы второго счетчика разрядности подключены к соответствующим информационным входам регистра Фиксации разрядности множимого и произведения, выход переполнения которого подключен к первому входу второго элемента И, второй вход которого соединен с выходом старшего разряда сумматора, а выход - с входом младшего разряда регистра множимого, вы:ход младшего разряда регистра фиксации разрядности множимого и произведения подключен к выходу признака нулевого множимого устройства, управляющие входы регистров фиксации разрядности множителя, множимого и произведения подключены к второмууправляющему входу устройства, выходы всех разрядов регистра множимого подключены к соответствующиминформационным входам первых групп 5 регистров кратных множимого информационные входы второй группы 1-го(1=2,9) регистра кратных множимого подключены к соответствующим выходам первой группы (1 - 1)-го регистра кратных множимого, выходыпервой группы второго регистра кратных множимого подключены к соответствующим информационным входам третьейгруппы четвертого регистра крат ных множимого, выходы первой группыкоторого подключены к соответствующим информационным входам третьейгруппы шестого, седьмого и восьмого регистров кратных множимого, выходы первой группы шестого регистра 20 кратных множимого подключены к соответствующим информационным входамчетвертой группы восьмого регистракратных множимого, выходы вторыхгрупп всех регистров кратных множи мого подключены к соответствующиминформационным входам сумматора,входы управления суммирования всехрегистров кратных множимого подключены к шине суммирования устройства,выходы сумматора являются. выходамимладших разрядов произведения устройства, а выходы регистра множимого являются выходами старших разрядов произведения устройства.35На фиг. 1 представлена блок-схема устройства для умножения десятичных чисел; на Фиг. 2 - структурнаясхема блока преобразования десятичной цифры из единичного нормальногокода в единичный позиционный код.40 устройство умножения содержитдевять регистров 1 кратных множимого, регистр 2 множителя, регистр 3множимого, сумматор 4, регистр 5фиксации разрядности множителя, ре гистр 6 Фиксации разрядности множимого и произведения, блок 7 преобразования десятичной цифры, счетчики 8 и 9 разрядности и элементы И10 и 11. Выходы. старшего К-го де О сятичного разряда регистра 2 соединены через блок 7 преобразованиядесятичной цифрь 1 с управляющими входами первой группы 12 девяти регистров 1 кратных маожимого, а выходы13 регистра 2 через счетчик 8 разрядности - с входом регистра 5 Фиксации разрядности множителя. Выходы 14 регистра 3 множимого и выходы15 сумматора через счетчик 9 разрядности связаны с .входами регистра 6фиксации разрядности множимого ипроизведения, выходы 16 которого ивыход старшего К-го десятичного разряда сумматора 4 через элемент И 10соединены с входом младшего десятичного разряда регистра 3 множимого.нием сумматора и последующий сдвигв сторону старших разрядных ячеексодержимого сумматора и регистрамножителя,4. Для каждого разряда множителяповторяются действия пунктов 2 и 3до тех пор, пока не будет произведено умножение на всех разрядах множителя.Устройство для умножения десятичных чисел работает следующим образом.Множимое А записывается в регистр3 множимого, множитель В - в регистр2 множителя.Одновременно с записью сомножителей по управляющим сигналам, поступающим по второму управляющемувходу 23 на управляющие входы регистров 5 и б, производйтся подсчет изапись разрядности сомножителей. Количество разрядов регистров 5 соответствует количеству десятичных разрядов регистра 2 множителя, а количество разрядов регистра б - суммарному количеству десятичных разрядов регистра 3 множимого и сумматора 4. Подсчет разрядности сомножителей выполняется по количеству сработавших десятичных разрядов регистров 2 и 3. При этом счетчиками 8 и 9 разрядности учитывается возможность появления значащихнулей в десятичных разрядах регистров 2 и 3, а равенство сомножителейнулю определяет наличие единицы вмладшем разряде регистров 5 и 6(признак Р, В этом случае операцияумножения йрекращается. В случае,когда ни один из сомножителей не равен нулю (Р = О), происходит фор 1мирование девяти кратных множимогона соответствующих регистрах 1 изнака произведения элементом И 11;знак произведения записывается повходу 25 в знаковый разряд регистра 3.Процесс Формирования девяти кратныхмножимого эа пять тактов можно проиллюстрировать следующей таблицей, где проставляется кратность Формируеьых на регистрах 1 кратных множимого,такта 1 2 3 4 5 6 7 8 9 1 1 1 1 2 1 1 2 3 5 6 7 5 6 7 Так, в первом такте во все девять регистров 1 по входам 17 записывается множимое А (его кратность равна 1 ) с выходов регистра 3, все десятичные разряды которого 5 1016780 6 Выходы регистра 3 множимого соединены с входами 17 девяти регистров 1 кратных множимого, Информационные выходы 18 первой группы которых связаны с входами сумматора 4, а информационные выходы 19 второй группы с входами 17 соответствующих соседних старших регистров 1. Причем выходы 19 второго регистра 1 соединены также с входами 17 четвертого регистра 1, выходы 19 которого связаны с входами 17 шестого, седьмого и восьмого регистров 1, а выходы 19 шестого регистра 1 - с входами 17 восьмого регистра 1. Шина 20 суммирования подключена к входам управления суммирования девяти регистров 1, первый управляющий вход 21 и выход 22 блока 7 йреобразования десятичной цифры - к управляющим входам регистров 2 и 3 и сумматора 4 Второй управляющий 20 вход 23 соединен с управляющими входами регистров 5 и б, у которых выходы младших разрядов являются выходами признака нулевого сомножителя, а выход старшего разряда ре гистра 5 является выходом признака Фиксаций окончания операций сдвига в регистре 2. Вход 24 блока 7 является его управляющим входом. Выходы знака регистров 2 и 3 через элемент И 11 соединены с входом 25 знакового разряда регистра 3 множимого. По входам множителя и мнбжимого устройства В и А в регистры 2 и 3 поступают соответственно множитель В З 5 и множимое А. С выходов П и П регистра 3 и сумматора 4 снймаются значения соответсвенно старших и младших разрядов произведения.Устройство реализует следующий алгоритм умножения десятичных чисел. 401. Проверяется равенство множимого и множителя нулю. В случае, если один из сомножителей или обасомножителя равны нулю, результату присваивается нулевое значение и опера ция умножения прекращается. В противном случае формируются кратные множимого на соответствующих регистрах и знак результата, который будет положительным при совпадении знаков 50 Номер регистра сомножителей и отрицательным при их несовпадении. Одновременно производится сдвиг содержимого регистра множителя в сторону старших разрядных ячеек до тех пор, пока в старшей разрядной ячейке не появится старшая значащая цифра множителя.2. Производится одновременное сравнение цифры старшего разряда множителя и номера каждого кратного множимого,, 603. При совпадении цифры старшего разряда множителя и данного номера одного иэ кратных множимого осуществляется суммирование соответствующего кратного множимого с содержа- ц после этого устанавливаются в ноль,кроме знакового, по управляющей последовательности, поступающей по входу 21Во второмтакте происходит суммирование содержимого регистра 1, номера которых являются четными, с содержимым соответствующего предыдущего регистра 1 и получение удвоенного значения множимого А ( кратностью 2 ). Во время третьего такта происходит суммирование содержимого третьего, четвертого, седьмого и восьмого регистров 1 с информацией, поступающей с выхода 19 второго.и шестого регистров 1 и т.д. Суммирование.на регистрах 1 осуществляется при поступлении сигналов на управляющие входы 12 соответствующих регистров 1 по шине 20 суммирования. Одновременно с образованием в массиве регистров 1 девяти кратных множимого осуществляется сдвиг множителя В в регистре .2 множителя в сторону старших разрядов по сигналу, поступающему на управляющий вход по входу 21. Сдвиг осуществляется до.тех пор, пока в самом старшем К-ом десятичном разряде регистра 2 не появится старшая значащая цифра множителя В, что фиксируется сигналом Р 2, снимаемым со старшего разряда регистра 5 фик- сации разрядности множителя. После этого при условии, что в массиве регистров 1 сформированы кратные множимого, и при наличии сигнала, поступающего на вход модуляции 24 блока 7, производится преобразование десятичной цифры, записанной в . старшем К-ом десятичном разряде регистра 2 в единичном нормальном коде, в единичный позиционный код, особенностью которого является наличие единицы в той позиции, вес которой соответствует значению цифры, а нуль кодируется единицей в нулевом разряде. Информационные выходы блока 7 соединены с соответствующими управляющими входами 12 регистров 1 таким образом, что наличие единицы в определенной весовой позиции, соответствующей значению десятичной цифры в К-ом разряде регистра 2, вызывает считывание информации из соответствующего регистра 1 по выходам 18 в сумматор 4 с сохранением записанной в данном регистре 1 информации. Например, нахождение цифры б в К-ом разряде регистра 2 приведет при наличии сигнала на входе 24 модуляции блока 7 преобразования к появлению единицы в б-ом разряде. блока 7, которая, в свою очередь, вызовет считывание информации в сумматор 4 из шестого регистра 1, где хранится шестикратное множимое А. Длительность управляющего сигнала, поступающего навход 24 модуляции блока 7 преобразования, соответствует времени считывания информации из соответствующего регистра 1 и сдвига информациина один разряд, которое не зависитот разрядности записанной в регистрах информации, а определяется временем, необходимым для считываниянаибольшей цифры, которой в десятичной системе счисления является "9".Таким образом осуществляется умножение на любую десятичную цифру. Поокончании перезаписи информации изсоответствующего регистра 1 в сумматор 4, т.е, после прекращениядействия управляющего сигнала навходе 24 блока 7 по сигналу, посту пающему по входу 21 на управляющиевходы регистра 2 и сумматора 4, впоследних происходит сдвиг содержимого всторону старших десятичныхразрядов. Затем вновь осуществля ется умножение на очередную десятичную цифру множителя В. В случае,если в. К-ом разряде регистра 2 де. -сятичная цифра является нулем, наличие единицы в нулевом разрядеблока 7 приводит лишь к сдвигу влево содержимого сумматора 4 и регистра 2Поскольку уменьшение разрядности множителя В фиксируется нарегистре 5 после каждого сдвигавлево, содержимого регистра 2, топоявление единицы в нулевом разрядерегистра 5 Р = Ц свидетельству 1ет об окончании операции умножения.В какой-то момент при умножении возможно переполнение разрядной сетки 35 сумматора 4. Этот момент фиксируется регистром б, сигнал с выхода 16которого на выход элемента И 10 разрешает, связь с выхода старшего К-.годесятичного разряда сумматора 4 на 40 вход младшего десятичного разрядарегистра 3 таким образом, что дальнейшая перезапись информации из соответствующего регистра 1 производится в сумматор с удвоенной раэряд ной сеткой состоящей иэ сум атораи регистра 3Информация, зафиксированная в .регистре б, дает представлейие о разрядности результатаумножения.Блок 7 преобразования может, быть 50 реализован на десяти релнеративныхбистабильных оптронах 26 с номерамипозиций отО до 9 и модуляторе 27,выход 28 которого подключен к электрическим входам всех оптронов 26Единичный оптический вход 29 нулевогооптрона 26 и вход модулятора 27 под-,ключены к управляющему входу блока 7,а единичный оптический выход 30 нулевого оптрона 26 является выходом 60 22 блока 7 преобразования. Единичныйоптический вход 29 каждого 1-гооптрона 26, кроме нулевого, является информационным входом 31 блока 7,нулевой оптический вход 32 соединен 65 с единичным оптическим входом 29соответс=венно (1 + 1)-го оптрона. Оптический выход 30 каждого оптрона 26, кроме нулевого, является информационным выходом блока 7.Блок 7 преобразования работает следующим образом. При поступлении на единичный вход 29 нулевого оптрона 26 и вход модулятора 27 оптического сигнала происходит.срабатывание соответствующего оптрона 26 и появление на его единичном выходе 30 1 О оптического сигнала, который является управляющим сигналом считыванля информации для соответствующего регистра 1. При этом срабатывает тот оптрон 26, на единичный вход 29 ко торого поступает оптический сигнал, а"на нулевом входе 32 он отсутствует. В случае, когда на обоих входах оптрона 26 либо присутствует, либо отсутствует оптический сигнал, опт-. рон 26 находится в нулевом состоянии и на его выходе 30 оптический сигнал отсутствует. Случай, когда на единичном входе 29 .оптрона 26 оптический сигнал не существует, а на нулевом входе 32 - существует, невозможен при единичном нормальном кодировании информации, которое применяется в оптоэлектронных устройствах и заключается в том, что каждой десятичной цифре ставится в соответ ствие количество последовательно сработавших оптронов, равное весуданной десятичной цифры. Таким образом, единичный сигнал может возникнуть только на одном из оптических выходов 30 оптронов 26. Использование блока 7 позволяет отказаться от традиционных схем сравнения. Этим достигается значительное уменьшение аппаратурных затрат, поскольку, одним блоком 7 преобразования заменяется девять схем сравнения, необходимых для выполнения операции сравнения цифр в десятичной системе счисления, а построение блока 7 преобразования на десяти регенеративных бистабильных оптронах повышает однородность оптоэлектронного десятичного. устройства умножения и позволяет организовать считывание информации из соответствующих регистров 1 по оптическому сигналу, поступающему с выхода блока 7 преобразования.Кроме того, при выполнении устройства. для умножения десятичных чисел на оптоэлектронных регистрах, в в которых использованы регенеративные бистабильные оптроны, а передача информации и управление узлами устройства осуществляется на оптическом уровне, повышается однородность реализации.. Состаая ,Техред ель Н. ЗахМигунова орректор м. шароыиБез Ред аз 3387/48 . Тираж ВНИИПИ Государственно по делам изобретени 113035, Москва, Ж, 06 П о комитета. СССР и открытий. Раушская наб., д. 4

СмотретьЗаявка

3367439, 18.12.1981

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОЖЕМЯКО ВЛАДИМИР ПРОКОФЬЕВИЧ, МАРТЫНЮК ТАТЬЯНА БОРИСОВНА, КОРОНОВСКИЙ АЛИМ ИВАНОВИЧ, ТИМЧЕНКО ЛЕОНИД ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: десятичных, умножения, чисел

Опубликовано: 07.05.1983

Код ссылки

<a href="https://patents.su/7-1016780-ustrojjstvo-dlya-umnozheniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения десятичных чисел</a>

Предыдущий патент: Вычислительное устройство

Следующий патент: Устройство для вычитания

Случайный патент: Устройство для автоматического управления сбрасывающими тележками надсилосных транспортеров зерновых элеваторов