Устройство для вычисления суммы квадратов к -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

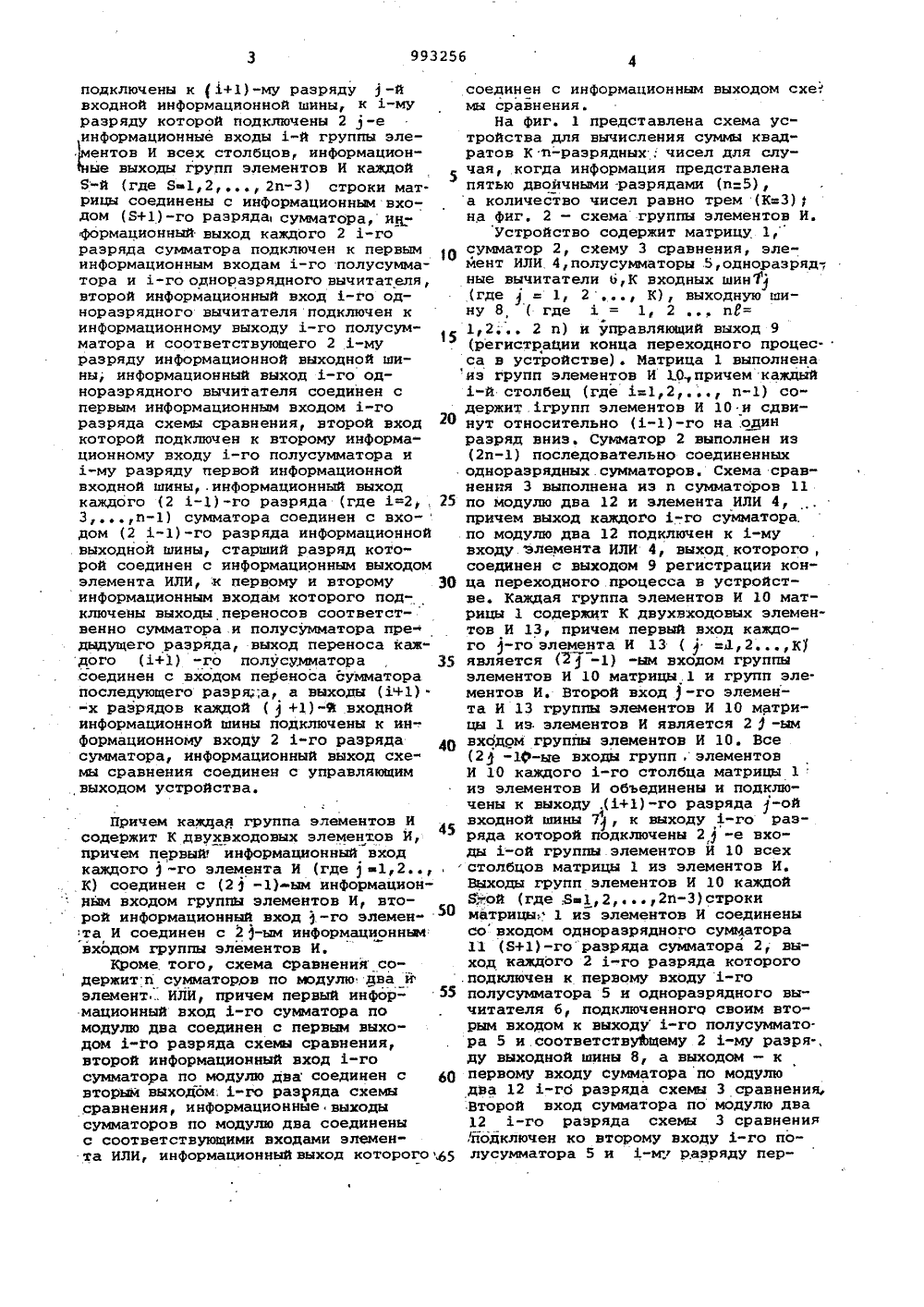

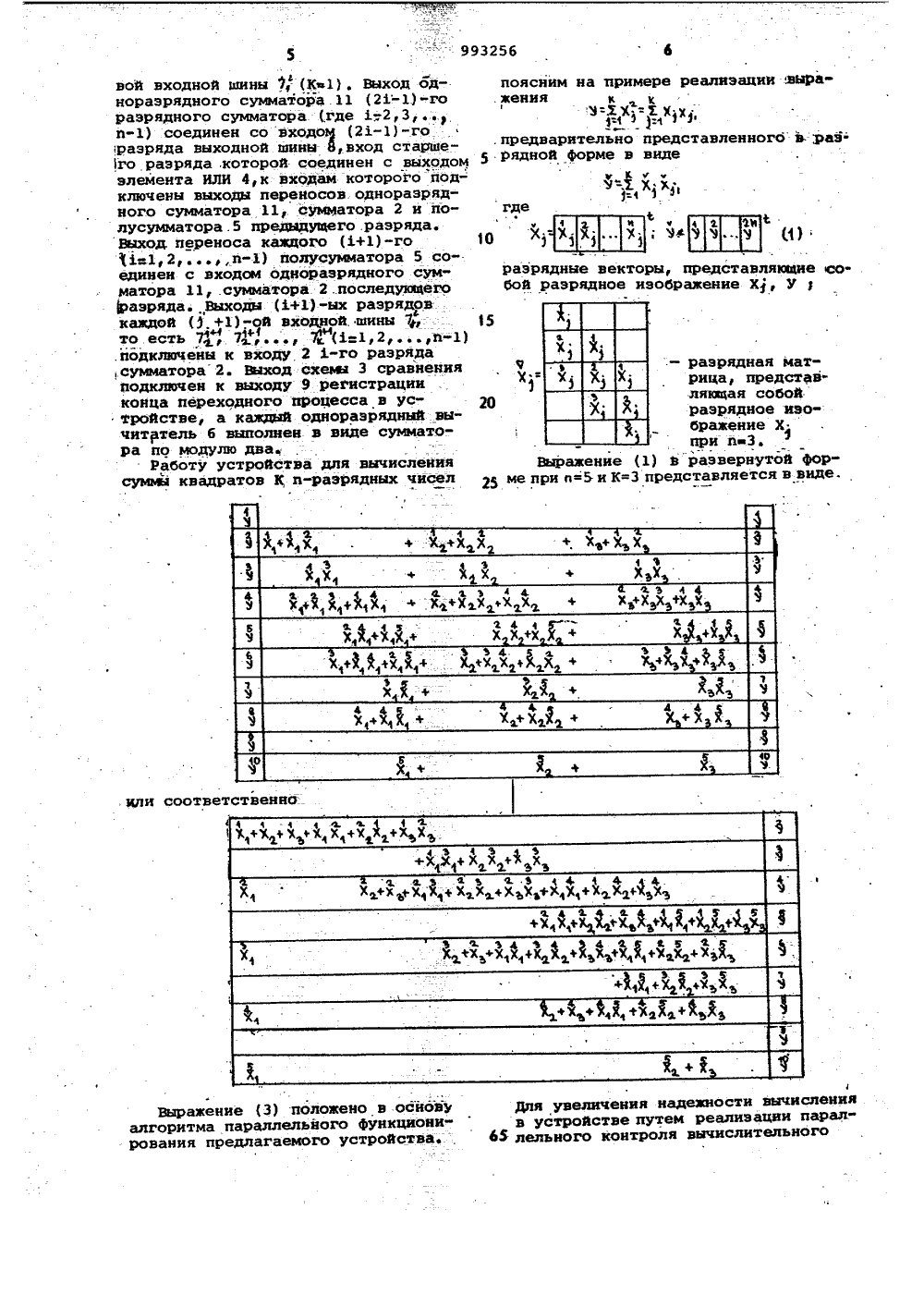

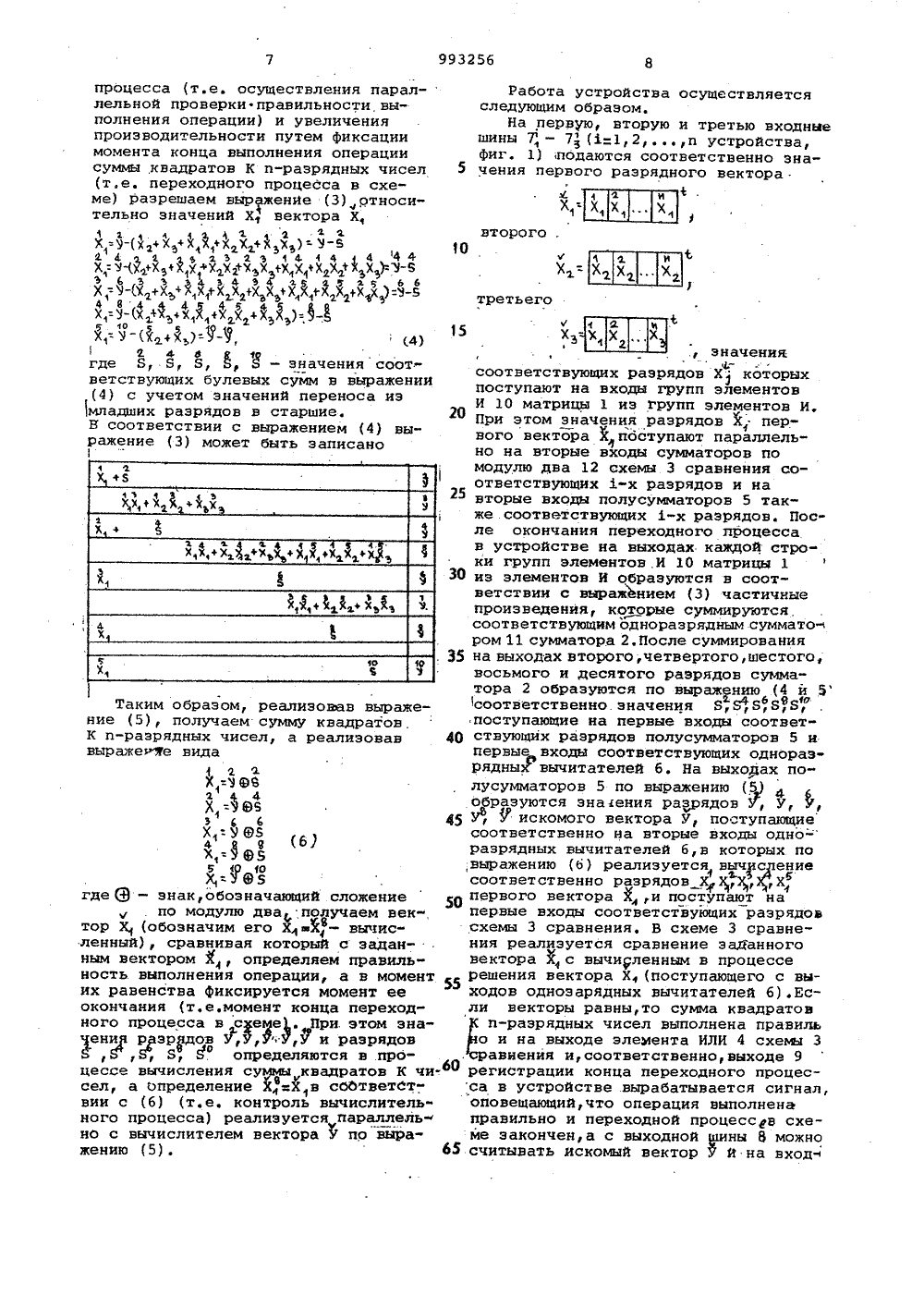

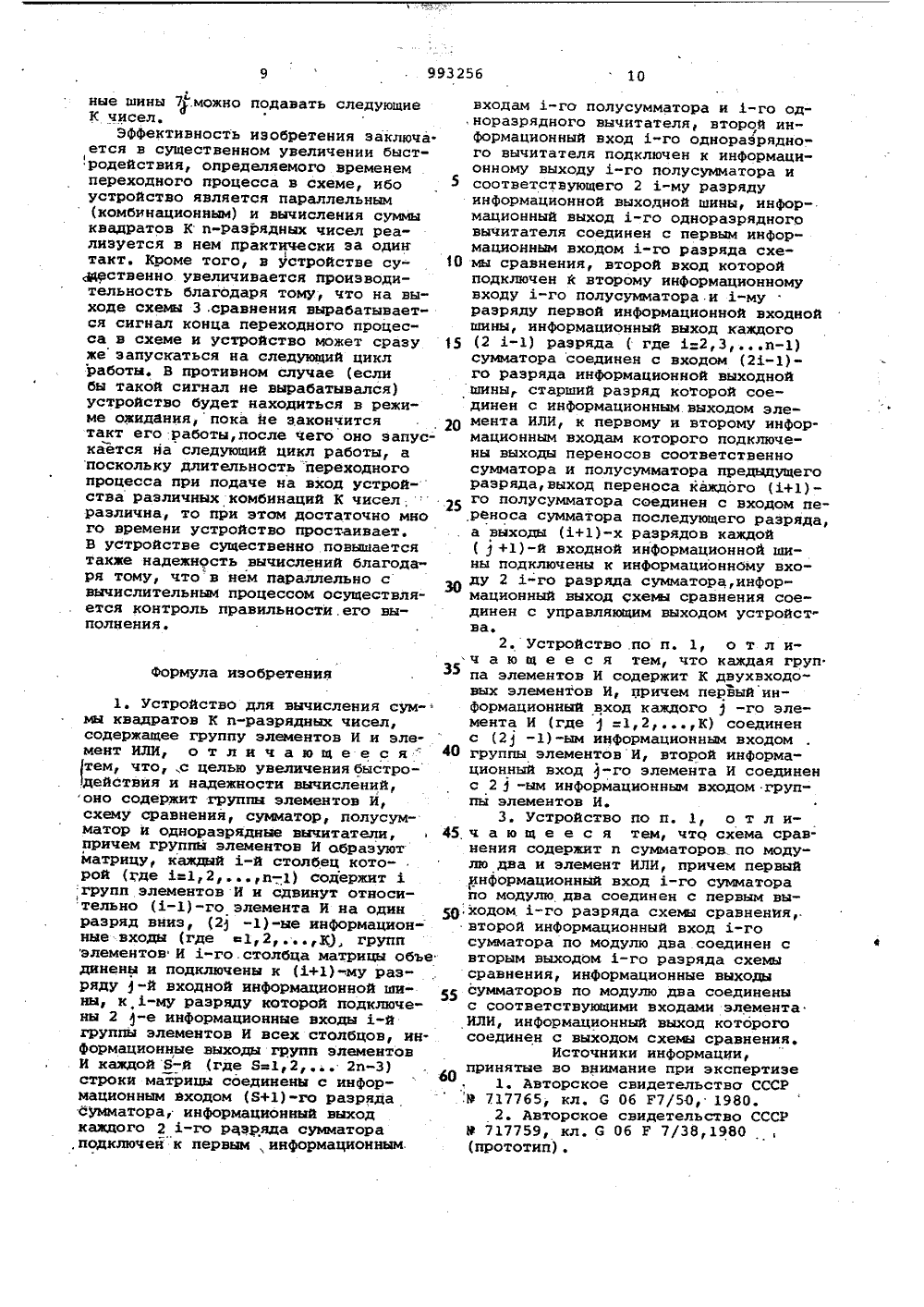

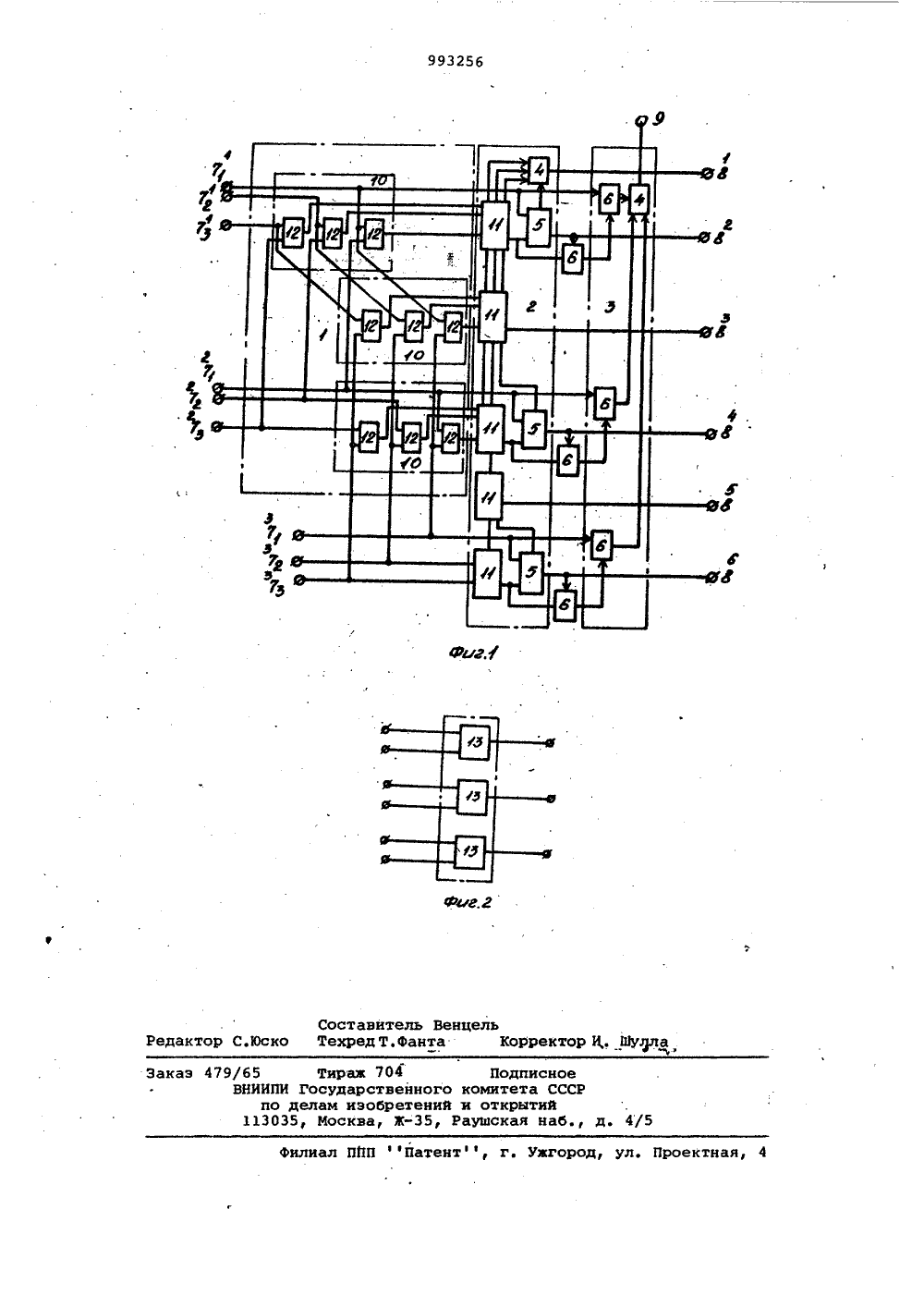

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскияСоциалистическикРеспублик н 11993256 ф(61) Дополнительное к авт. свид-ву- (22) Заявлено 090281 (21)3245246/18-24 с присоединением заявки Йо 51) М. Кл. 0 06 Р 7/544 Государственный комитет СССР по делам изобретениИ и открытий(088,8) Опубликовано 3001.83. Бюллетень Но 4 Дата опубликования описания 30.01,83 Мй;щ,Г.Е.Пухов, А.И.Стасюк, ф.Е.Лисник и А,Игузенко(72) Авторы изобретения Киевский ордена Трудового Красного Знамени-институт инженеров гражданской авиации(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММЫ КВАДРАТОВ К и-РАЗРЯДНЫХ ЧИСЕЛ Изобретение . относится к вычислит ельной технике и может быть применено в качестве сйецпроцессора в комплексе с цифровой вычизлительной машиной для оперативного вычисления суммы квадратов К и-разрядных чисел.Известно устройство для вычисления суют парных произведений, содержащее регистр множимого, регистр множителя, узел сдвига, сумматор, узел управления, группы элементов И, элементы И, ИЛИ, группу элементов ИЛИ) 11,. Недостатком этого устройства яв- ляется относительно низкое быстродействие из-эа последовательной организации вычислительного процесса и невысокая надежность вычислений, определяемая тем, что в устройстве не организован контроль вычислитель ного процесса.Наиболее близким к предлагаемому является устройство для вычисления суюсь квадратов К и-разрядных чисел, содержащее счетчик основания, разрядные выходы которого через элементы И группы соединены с выходами соответствующих разрядов накопителя, формирователи строб-импульсов, К" звейная линия задержки, К-ключей и элемен ты ИЛИ, выход первого из которых соединен со входом второго разряда счетчика основания и К-звенной линии задержки 21Недостатками этого устройства явля ются его низкое быстродействие, определяемое тем, что вычисление суммы квадратов чисел в нем реализуется в виде последовательности шагов, и от" носительно невысокая надежность изэа невозможности реализации одновременного контроля вычислительного процесса.Цель изобретения - увеличение быст" родействия и надежности вычислений суюы квадратов К и-разрядных чисел.Поставленная цель достигается тем, что устройство для вычисления суюаю квадратов К п-разрядных чисел, содержащее. группу элементов И и элемент ИЛИ, содержит группы элементов И, схему сравнения, сумматор, полу- сумматор и одноразрядные вычитатели, причем. группы элементов И образуют й матрицу,.каждый 1-й столбец которой (где 1:1,2п) содержит 3. групп элементов Й и сдвинут относительно (1-1)-го элемента И на один разряд вниз,.(2-1)-е информационные входы (где:1,2, К) групп элементов И ,1-го столбца матрицы объединены,иподключены к ( 1+1) -му разряду 3 -й входной информационной шины, к 1-му разряду которой подключены 2 )-е информационные входы 1-й группы элеентов И всех столбцов, информационые выходы групп элементов И каждой Я-й (где Яв 1,2 2 п) строки матрицы соединены с информационным входом (Я+1)-го разряда сумматора, информационный выход каждого 2 1-го разряда сумматора подключен к первым информационным входам 1-го полусумма- тора и 1-го одноразрядного вычитателя, второй информационный вход 1-го одноразрядного вычитателя подключен к информационному выходу 1-го полусумматора и соответствующего 2 1-му разряду информационной выходной шины, информационный выход 1-го одноразрядного вычитателя соединен с первым информационным входом 1-го разряда схемы сравнения, второй вход которой подключен к второму информационному входу 1-го полусумматора и 1-му разряду первой информационной входной шины,.информационный выход каждого (2 1-1) -го разряда (где 1=2, Зп) сумматора соединен с вхо-дом (2 1-1)-го разряда информационной выходной шины, старший разряд которой соединен с информационным выходом элемента ИЛИ, к первому и второму информационным входам которого подключены выходы переносов соответственно сумматора и полусумматора предыдущего разряда, выход переноса каж" дого (1+1) -го полусумматора соединен с входом переноса сумматора последующего разряа, а выходы (1+1)-х разрядов каждой (+1)-й входной информационной шины подключены к информационному входу 2 1-го разряда сумматора, информационный выход схемы сравнения соединен с управляющим выходом устройства. Причем каждая группа элементов И содержит К двухвходовых элементов И, причем первый информационный вход каждого ) -го элемента И (где ) 1,2. К) соединен с (2 3 -1) ым информационным входом группы элементов И, второй информационный вход ) -го элемента И соединен с 2 7-ым информационньм: входом группы элементов И.Кроме того, схема сравнения содержит и сумматоров по модулю два й элемент. ИЛИ, причем первый информационный вход 1-го сумматора по модулю два соединен с первым выходом 1-го разряда схемы сравнения, второй информационный вход 1-го сумматора по модулю два соединен с вторым выходом. 1-го разряда схемы сравнения, информационные выходы сумматоров по модулю два соединены с соответствующими входами элемен" та ИЛИ, информационный выход которого соединен с информационным выходом схе.мы сравнения.На фиг. 1 представлена схема устройства для вычисления суммы квадратов К и-разрядных; чисел для слу чая, когда информация представленапятью двоичными разрядами (и:5),а количество чисел равно трем (КщЗна Фиг. 2 - схема группы элементов И.Устройство содержит матрицу 1, о сумматор 2, схему 3 сравнения, элемент ИЛИ 4,полусумматоры .5,одноразряд-,ные вычитатели 6,К входных шин 7(регистрации конца переходного процесса в устройстве) . Матрица 1 выполненанз групп элементов И 10 причем каждый1-й столбец (где 1 а 1,2 и) содержит 1 групп элементов И 10 и сдви нут относительно (1-1)-го на,одинразряд вниз. Сумматор 2 выполнен из(2 п) последовательно соединенныходноразрядных. сумматоров. Схема сравнения 3 выполнена из и сумматоров 11 25 по модулю два 12 и элемента ИЛИ 4,причем выход каждого 1-го сумматора.по модулю два 12 подключен к 1"мувходу.элемента ИЛИ 4, выход которого,соединен с выходом 9 регистрации кон- ЭО ца переходного процесса в устройстве. Каждая группа элементов И 10 матрицы 1 содержит К двухвходовых элементов И 13, причем первый вход каждого -го элемента И 13 ( у :з 1,2,К 35 является Л-1) -ым входом группйэлементов И 10 матрицы.1 и групп элементов И. Второй вход-го элемента И 13 группы элементов И 10 матрицы 1 из элементов И является 2 1 -ым 40 входом" группы элементов И 10. Все(2 -1-ые входы групп, элементовИ 10 каждого 1-го столбца матрицы 1из элементов И объединены и подключены к выходу,(1+1)"го разряда -ойвходной шины 7, к выходу 1-го разряда которой подключены 2 ) -е входы 1-ой группы элементов И 10 всехстолбцов матрицы 1 из элементов И.Выходы групп элементов И 10 каждойВ-ой (где 31,22 п) строкиматрицы; 1 из элементов И соединенысо входом одноразрядного суьщатора11 (Я+1)-горазряда сумматора 2, выход каждого 2 1-го разряда которого.подключен к первому входу 1-го 55 полусумматора 5 и одноразрядного вычитателя б, подключенного своим вторым входом к выходу 1-го полусуммато.ра 5 и.соответствующему 2 1-му разря-,ду выходной шины 8, а выходом - к 6 О первому входу сумматора по модулюдва 12 1-гб разряда схемы 3 сравнения,Второй вход сумматора по модулю два12 1-го разряда схемы 3 сравненияйодключен ко второму входу 1-го полусумматора 5 и 1-му разряду перные шины 7,.можно подавать следующие К чисел.Эффективность изобретения заключается в существенном увеличении быстродействия, определяемого временем переходного процесса в схеме, ибо устройство является параллельным (комбинационным) и вычисления суммы квадратов К и-разрядных чисел реализуется в нем практически за один такт. Кроме того, в устройстве су,щественно увеличивается производительность благодаря тому, что на выходе схемы 3 .сравнения вырабатывается сигнал конца переходного процесса в схеме и устройство может сразу же запускаться на следующий цикл работы. В противном случае (если бы такой сигнал не вырабатывался) устройство будет находиться в режиме ожидания, пока не закончится такт его работы, после чего оно запускается на следующий цикл работы, а поскольку длительность переходного процесса при подаче на вход устрой-ства различных комбинаций К чисел; различна, то при этом достаточно мно го времени устройство простаивает. В устройстве существенно повышается также надежность вычислений благодаря тому, чтов нем параллельно с вычислительным процессом осуществляется контроль правильности.его выполнения.Формула изобретения1. Устройство для вычисления сум" мы квадратов К и-разрядиых чисел, содержащее группу элементов И и эле- . мент ИЛИ, о т л и ч а ю щ е е с ятем, чтос целью увеличения быстродействия и надежности вычислений, оио содержит группы элементов И, схему сравнения, сумматор, полусумматор и одноразрядные вычитатели, причем группы элементов И Образуют матрицу, каждый 1-й столбец которой (где 1 а 1,2п) содержит 1 групп элементов И и сдвинут относительно (1-1)-го элемента И на один разряд вниз, (2 -1)-ые информацион- ные входы (где 1,2К), групп элементов И 1-го.столбца матрицы объе динены и подключены к (1+1)-му разряду-й входной информационной шины, к 1-му разряду которой подключены 2 -е информационные входы 1-й группы элементов И всех столбцов, инФормационные выходы групп элементов И каждой Я-й (где Я:1,2, 2 п) строки матрицы соединены с информационным входом (Я+1)-го разряда Сумматора, информационный выход каждого 2 1-го разряда сумматора ,подключей к первым ,информационным. входам 1-го полусумматора и 1-го одноразрядного вычитателя, второй инФормационный вход 1-го одноразрядного вычитателя подключен к информационному выходу 1"го полусумматора и5 соответствующего 2 1-му разрядуинформационной выходной шины, информационный выход 1-го одноразрядноговычитателя соединен с первым информационным входом 1"го разряда схе(О мы сравнения, второй вход которойподключенвторому информационномувходу 1-го полусумматора и 1"муразряду первой информационной входнойшины, информационный выход каждого5 (2 1-1) разряда ( где 1-2,3,п)сумматора соединен с входом (21-1)- го разряда информационной выходнойшины старший разряд которой соединен с информационным. выходом эле 20 мента ИЛИ, к первому и второму информационным входам которого подключены выходы переносов соответственносумматора и полусумматора предыдущегоразряда, выход переноса каждого (1+1)- го полусумматора соединен с входом переноса сумматора последующего разряда,а выходы (1+1)-х разрядов каждой( ) +1)-й входной информационной шины подключены к информационнОму входу 2 1-го разряда сумматора,информационный выход схемы сравнения соединен с управляющим выходом устройства.2. Устройство .по п. 1, о т л ич а ю щ е е с я тем, что каждая группа элементов И содержит К двухвходовых элементов И, причем первый информационный вход каждого 7 -го элемента И (где 7:1,2К) соединенс (2 -1)-ым информационньвс входом40 группы элементов И, второй информационный вход -го элемента И соединенс 2 3 -ым информационным входом группы элементов И.3. Устройство по п. 1, о т л и 45 ч а ю щ е е с я тем, что схема сравнения содержит и сумматоров.по модулю два и элемент ИЛИ, причем первыйинформационный вход 1-го сумматорапо модулю два соединен с первым вы 50 ходом. 1-го разряда схемы сравнения,.второй инФормационный вход 1-госумматора по модулю два.соединен свторым выходом 1-го разряда схемысравнения, информационные выходы55 сумматоров по модулю два соединеныс соответствующими входами элементаИЛИ, информационный выход которогосоединен с выходом схемы сравнения.Источники инФормации,принятые во внимание при экспертизе1, Авторское свидетельство СССРР 717765 кл. 6 06 Г 7/50 1980,2. Авторское свидетельство СССРУ 717759 кл. С 06 Р 7/38,1980993256 е Составитель Венц льо Техред Т.фанта КорректоР 1, Шуу Редакто Закаэ 479/65 Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий 113035, Москва, Ж, Раушская наб.

СмотретьЗаявка

3245246, 09.02.1981

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ПУХОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ, СТАСЮК АЛЕКСАНДР ИОНОВИЧ, ЛИСНИК ФЕДОР ЕРЕМЕЕВИЧ, ГУЗЕНКО АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, квадратов, разрядных, суммы, чисел

Опубликовано: 30.01.1983

Код ссылки

<a href="https://patents.su/6-993256-ustrojjstvo-dlya-vychisleniya-summy-kvadratov-k-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления суммы квадратов к -разрядных чисел</a>

Предыдущий патент: Устройство для умножения -разрядных чисел

Следующий патент: Устройство для получения квадратичной зависимости

Случайный патент: Электродвигатель постоянного тока