Устройство для умножения -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

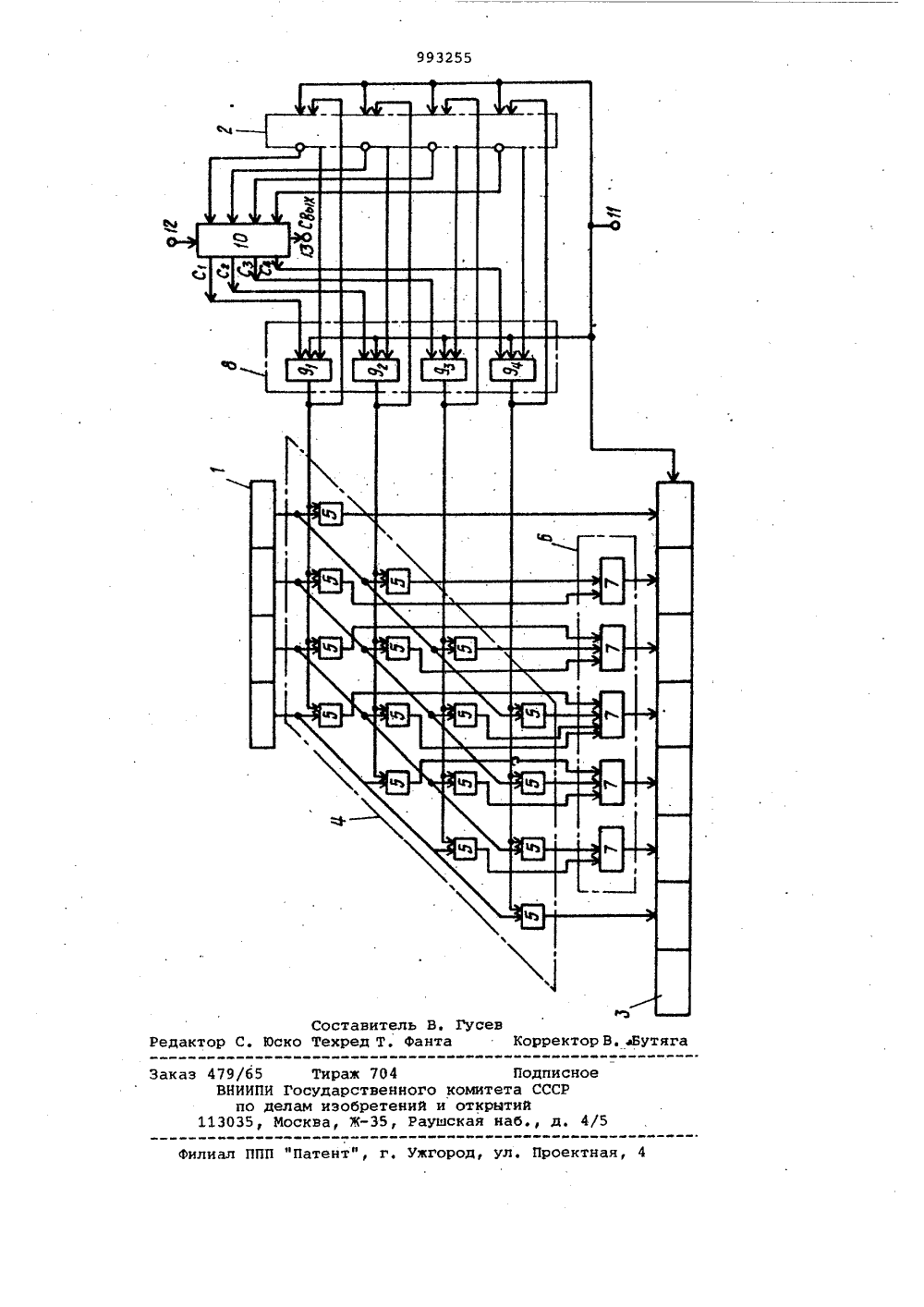

Союз СфветскикСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТОЬСТВУ н 1993255(И 1 М. Ка.з С 06 Г 7/52 Государственный комитет СССР но. делам изобретений н открытий(088, 8) Дата опубликования описания 30.01.83(У 1 ) Заявитель Минский радиотехнический институт.(54) УСТРОЙСТНО ДЛЯ УМНОЖЕНИЯ и-РАЗРЯДНЫХв ЧИС Изобретение относится к вычислительной технике и может быть использовано при разработке быстродейству- ющих устройств умножения асинхронного типа. Известно устройство для умножения и-разрядных чисел, содержащее и-разрядные Регистры множимого, множителя и результата, сумматор и блок управления 1 11.Недостатком известного устройства является его низкое быстродействие, вызванное тем, что время, затрачиваемое на сдвиги информации в регистрах, не зависит от числа единиц в разрядах множителя и всегда равно и йсо.Известно также устройство для Умножения п-разрядных чисел, содержащее и-разрядные регистры множимого и множителя, 2 п-разрядный сумматор, матрицу из п 2 элементов И, блок из (2 п) элементов ИЛИ н два блока из и элементов И каждый 2.).Недостаток известного устройства- низкое быстродействие, поскольку .длительность такта работы устройства зависит от времени переходного процесса во втором блоке элементов И. Наиболее близким к предлагаемомуявляется устройство для умноженияи-разрядных чисел, содержащее п-раз-.Рядный Регистр множимогои-Разрядный регистр небожителя, (2 п)-разрядный накапливающий сумматор, матрицу.из и элементов И, (2 п)-разрядный2.,блок элементов ИЛИ, и-разрядный блокэлементов И и и-разрядный комбина,ционный сумматор, причем выходырегистра множимого соответственносоединены с первой группой- входовматрицы элементов И, выходы (2, ..,2 п)-го .РазРядов которой соедйненыс соответствующими входами элементовИЛИ блока элементов ИЛИ, выходы элементов ИЛИ которого соответственносоединены с (2, , 2 п)-ми вход ными разрядами накапливающего сумматора, первый и (2 п)-й разрядныевходы накапливающего сунвнатора сонответственно соединены с первым и и -мвыходами матрицы элементов И, втораягруппа входов которой соответствен но соединена с выходами элементовИ блока элементов И, первые входы.которых соответственно соединены спрямыми выходами регистра множителя,вторые входы элементов И блока элементов И соответственно соединеныс выходами комбинационного сумматора, а третьи входы объединены и соединены с управляющим входом накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения 1,3).Недостаток известного устройства - сложность.Цель изобретения - упрощение устройства.Поставленная цель достигается тем,что в устройстве для умножения и-разрядных чисел, содержащем и-разрядный регистр множимого, и-разрядный ре-. гистр множителя, (2 п)-разрядный накапливающий сумматор, матрицу из и элементов И, (2 п)-разрядный блок элементов ИЛИ, и-разрядный блок элементов И и и-разрядный комбинационный сумматор, причем выходы регистра множимого соответственно соединены с первой группой входов матрицы элементов И, выходы (2, 2 п)-го разрядов которой соединены с соответствующими входами элементов ИЛИ блока элементов ИЛИ, выходы эле-. ментов ИЛИ которого соответственно соединены с (2., 2 п)ми входными разрядами накапливающего сумматора, первый и (2 п)-й разрядные входы накапливающего сумматора соответственно соединены с первым и п"м выходами матрицы элементов И, вторая группа входов которой соответственно соединена с выходами элементов И бло ка элементов И, первый входы элементов И блока элементов И соответственно соединены с прямыми выходами регистра множителя, вторые входы элементов И блока элементов И соответственно соединены с выходами комбинационного сумматора, а третьи входы объединены и соединены с управляющим входом накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения, выходы элементов И блока элементов И соответственно соединены с входами установки в нуль и раз рядов регистра множителя, инверсные выходы, которого соответственно соединены с входами комбинационного сумматора, а вход разрешения записи регистра множителя соединен с шиной синхронизации устройства.На чертеже изображена структурная схема устройства для умножения и-разрядных чисел (для п).Устройство для умножения и-разрядных чисел содержит и-разрядный регистр 1 множимого, и-разрядный регистр 2 множителя, (2 п)-разрядный накапливающий сумматор 3, матрицу 4 иэ п элементов И 5, (2 п)-разрядный блок б элементов ИЛИ 7, п-разряд.ный блок 8 элементов И 9, и-разрядный комбинационный сумматор 10, ши ну 11 синхронизации, управляющийвход 12 и выход 13 индикации окончания опеоации умножения, причем выходы регистра 1 множимого соответственно соединены с первой группой входов матрицы 4 .элементов И 5, выходы (2, , 2 п)-го разрядов которой соединены с соответствующими входами элементов ИЛИ 7 блока б элементов ИЛИ, выходы элементов ИЛИ 7 которого соответственно соединены с (2. . . 2 п)-ми входными разрядами накапливающего сумматора 3, первый и (2 п)-й разрядные входы на" капливающего сумматора 3 соответственно соединены с первым и и -м выходами матрицы 4 элементов И 5, вторая группа входов которой соответственно соединена с выходами элементов И 9 блока 8 элементов И и с входами установки в ноль и разрядов регистра 2 множителя, первые вхоцы элементов И 9 блока 8 элементов И соответственно соединены с прямыми выходами регистра 2 множителя инверсные выходы кото- рого соответственно соединены с вхо- ЗО дами комбинационного сумматора 10,выходы комбинационного сумматора 10 соответственно соединены с вторыми входами элементов И 9 блока 8 элементов И, третьи входы которых объ единены и соединены с управляющимвходом накапливающего сумматора 3, входом разрешения записи регистра 2 множителя и шиной 11 синхронизации устройства, управляющий вход 12 уст О ройства соединен с входом переносакомбинационного сумматора 10, выходпереноса которого соединен с выходом13 индикации окончания операции умножения.45 Устройство Работает следующим образом.Пусть требуется перемножить множимое х на множитель у = у 4 у у у, =1010. В исходном состоянии в регистре 1 хранится двоичный код множимого х без знака, а в регистре 2двоичный код множителя у также беззнака, сумматор 3 обнулен, а на выходе счетчика сФормирован результатссс с с 0101 + 0001 = 0110.Собственйо работа устройства начинается с момента прихода первогосинхроимпульса на вход 11 устройства.По этому синхроимпульсу Формируетсяуправляющий сигнал на выходе второ го элемента И 9 блока 8 элементов И(так как только с у 1), которыйпроизводит передачу соответствующим .образом сдвинутого множимого с выходов элементов И 5 второй строки 65 матрицы 4 через блок б элементовИЛИ 7 в накапливающий сумматор 3,а также осуществляет установку второго разряда регистра 2 множителяв нуль с разрешения синхроимпульса,поступающего на его вход разрешениязаписи с,шины 11 синхронизации устройства. После этого одновременнос суммированием частичного произведения в накапливающем сумматоре 3 вкомбинационном сумматоре 10 формиру. ется результат сс 4,с с с.п 0111 + 10+ 00011000.Во втором такте работы устройствас приходом второго синхроимпульсана шину 11 синхронизации устройствана выходе четвертого элемента И 94блока 8 элементов И ФоФмируется управляющий сигнал (с 4 1 и у 1),который производит передачи соответствующим образом сдвинутого множимого с выходов элементов И 5 четвертойстроки матрицы 4 элементов И 5 черезблок 6 элементов ИЛИ 7 в накапливакв 1 ий сумматор 3 и осуществляет установку четвертого разряда регистра 2множителя в ноль. После этого, одновременно с суммированим в накапливающем. сумматоре 3 очередного частичного произведения, комбинационномсумматоре 10 формируется результатс ю с 4 с с сщ 1111 + 0001 = 0000 ивозникает перенос сзых= 1. Поскольку 30с = 1, то на выходе 13.индикацииустройства присутствует сигнал, чтоозначает окончание операции узеожения чисел,Отсутствие, по сравнению с прототипом, и-разрядного буферного регистра и второго блока элементов И значительно упрощает устройство, неснижая его быстродействия.40Формула изобретенияУстройство для умножения и-разрядных чисел, содержащее и-разрядный 45 регистр множимого, и-разрядный регистр множителя, (2 п)-разрядный накапливающий сумматор, матрицу из п элементов И, (2 п)-разрядный блок элементов ИЛИ, п-разрядный блок элементов И и и-разрядный комбинационный сумматор, причем выходы регистра множимого соответственно соединены.с первой группой входов,матрицы элементов И, выходы (22 п -2)-го разрядов которой соединеныс соответствующими входами элементовИЛИ блока элементов ИЛИ, выходы элементоэ ИЛИ которого соответственносоединены с (2, , 2 п)-ми входными разрядами накапливакнцего сумматора, первый и (2 п)-й разрядныевходы накапливающего суюатора соответственно соединены с первым и и -мвыходамн матрицы элементов И, втораягруппа входов которой соответственносоединена с выходами элементов И блока элементов И, первые входы элементов И блока элементов И соответственно соединены с прямыми выходами регистра множителя, вторые входы элементов И блока элементов И соответственно соединены с выходами комбинационного суююатора, а третьи входыобъединены и соединены с управляющимвходом, накапливающего сумматора ишиной синхронизации устройства, входи выход переноса комбинационногосумматора являются соответственноуправляющим входом устройства и выходом индикации окончания операцииумножения, о т л и ч а ю щ е е с ятем, что, с целью упрощения устройства, выходы элементов И блока элементов И соответственно соединеныс входами установки в нуль и разрядов регистра множителя, инверсныевыходы которого соответственно соединены с входами комбинационногосумматора, а вход разрешения записирегистра множителя соединен с шинойсинхронизации устройства.Источники информации,принятые во внимание при экспертизе1. Карцев М. А. Арифметика цифровых машин. И., фНаукаф, 1969, с, 350,364.2. Авторское свидетельство СССР9 482740, кл, О 06 Г 7/52, 1974.3. Авторское свидетельство СССРпо заявке 9 3321307/18-24,кл, 6 06 Г 7/52, 1981 (прототип).993255 Составитель В. ГусевЮско Техред Т, Фанта Корректор В. Бутнга а гой иауы лиал ППП фПатентф, г. Ужгород, ул. Проектн Заказ 479/65 Тираж 704 ПодписноеВНИИПИ Государственно комитета СССРпо делам изобретени открытий113035, Москва, Ж, Р окая наб., д. 4/

СмотретьЗаявка

3343801, 28.07.1981

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЛОПАТО ЛИЛИЯ ГРИГОРЬЕВНА, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

Опубликовано: 30.01.1983

Код ссылки

<a href="https://patents.su/4-993255-ustrojjstvo-dlya-umnozheniya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения -разрядных чисел</a>

Предыдущий патент: Сумматор-вычитатель

Следующий патент: Устройство для вычисления суммы квадратов к -разрядных чисел

Случайный патент: Киносъемочный аппарат для съемки по способу "блуждающая маска"