Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

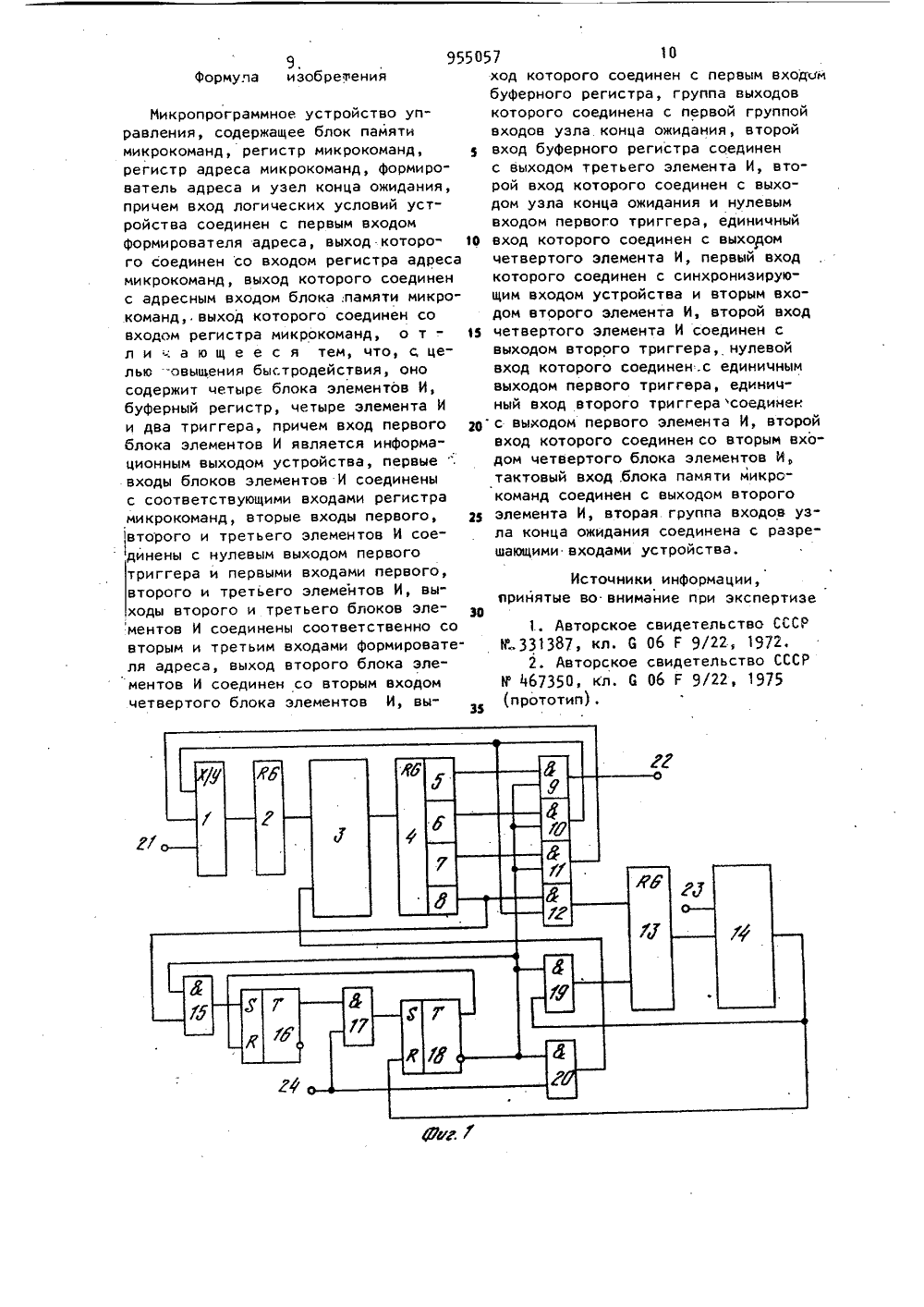

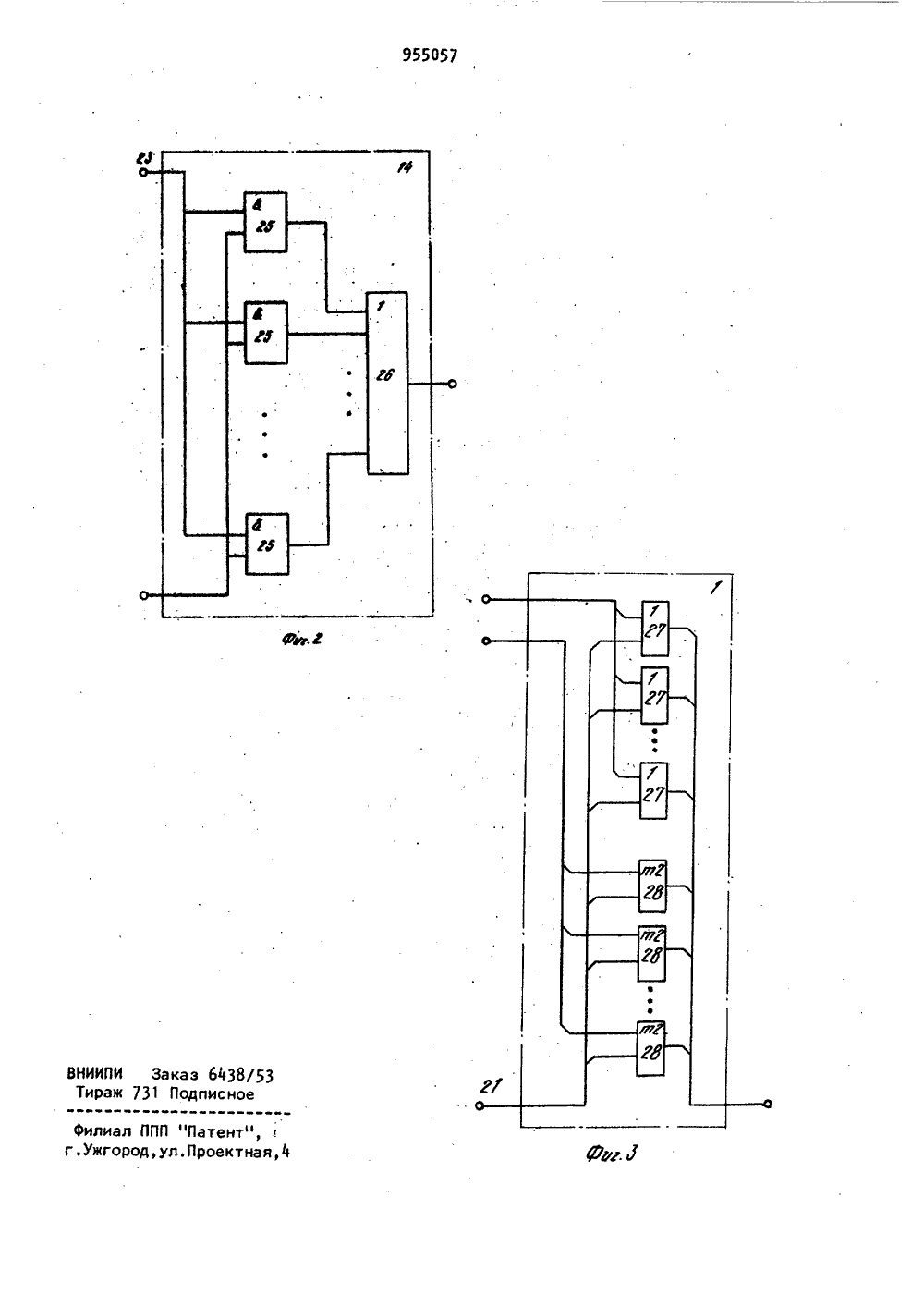

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п 1955057 Союз СоветсиикСоциапистичесииаРеспубпии(51)М, Кл. С 06 Г 9/22 3 Ьоудоротюныб комдтот СССР до делам дзобретеикд и открытий(53) УДК 681.325(088.8) Опубликовано 30,08.82. Бюллетень32 Дата опубликования описания 30. 08, 82) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕН Изобртельнойзовано в Недостатком известного устроиства является низкое быстродействиеЦель изобретения - повышение::быстродействия.Поставленная цель достигаетсятем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микро- команд, регистр адреса микрокоманд, формирователь адреса и узел конца ожидания, причем вход логических условий устройства соединен с первым входом формирователя адреса, выход которого соединен со входом регистра адреса микрокоманд, выход которого соединен с адресным входом блока памяти микрокоманд, выход которогр соединен со входом регистра микро команд, введены четыре блока элемен тов И буферный регистр, четыре элемента И и два триггера, причем выход первого блока элементов И является информационным выходом устройства, первые входыблоков элементов И соеится к вычислижет быть испольравляющего уст- вычислительных ение отно хнике и м ачестве у ектронных стем. иства э шин и с Известно микропрограммное устройство управления,. содержащее блокпамяти микрокоманд регистр микрокоманд, регистр адреса микрокоманд ЯОднако указанное устройство Ьблаизкими функциональными возмоВи, обусловленными ограничениемдействия при выполнении микромм с ожидаемыми логическими уси и избыточностью структуры.Наиболее близким к предлагаемомупо технической сущности и достигаемому эффекту является микропрограм"мное устройство управления, котороесодержит блок памяти микрокоманд,регистр микрокоманд, регистр адресамикрокоманд, формирователь адресаи схему конца ожидания 12,дает н ностям быстро програ ловиям В.С. Харченко, Г.Н. Тимонькин, С.Н. Ткаченко В.И. Сидоренко, А.В. Захаренко и Н,А, Е9 Я 05 динены с соответствующими выходамирегистра микрокоманд, вторые входыпервого, второго и третьего блоковэлементов И соединены с нулевым выходом первого триггера и с первыми 5входами первого, второго и третьегсэлементов И, выходы второго и тре-тьего блоков элементов И соединенысоответственно со вторым и третьимвходами Формирователя адреса, выход 10второго блока элементов И соединенсо вторым входом четвертого блокаэлементов И, выход которого соединенс первым входом .буферного регистра,группа выходов которого соединена 15с первой группой входов узла концаожидания, второй вход буферного регистра соединен с выходом третьегоэлемента И, второй вход которого сое.динен с выходом узла конца ожидания 20и нулевым входом первого триггера,единичный вход которого соединен свыходом четвертого элемента И, первый вход которого соединен с синхронизирующим входом устройства и вторым входом второго элемента И, второй,вход четвертого элемента И соединен с выходом второго триггера, нулевойвход которого соединен с единичным выходом первого триггера, единичный вход второго триггера. соединен с .выходом первого элемента И, второйвход которого соединен со вторым входом четвертого блока элементов И,тактовый вход блока памяти;микрокоманд соединен с выходом второго эле 35мента И, вторая группа входов узлаконца ожидания соединена с разрезающими входами устройства.На фиг. 1 представлена функциональ 40ная схема микропрограммного устройства управления; на фиг. 2 - функциональная схема узла конца ожидания; на фиг. 3 - структурная схемаформирователя адреса.Микропрограммное устройство уп 45равления (фиг. 1) содержит формирователь 1 адреса, регистр 2 адресамикрокоманд, блок 3 памяти микрокоманд, регистр 4 микрокоманд с полем5 микрооперации, полем 6 ожидаемых50логических условий, полем 7 модифи"кации и полем 8 метки, блоки элементов И 9- 12, буферный регистр 13,узел 14 конца ожидания; элемент И 15,.триггер 16, элемент И 17, триггер13, элемент И 19, элемент И 20, вход21.условий устройства, информационный выход 22 устройства, кодовый 7 авход 23 устройства и синхронизирующий вход 24 устройства.Узел конца ожидания (фиг; 2) содержит группу элементов И 25 и элемент ИЛИ 26,формирователь адреса (фиг, 3)содержит группу элементов ИЛИ 27группу сумматоров 28 по модулю два.формирователь 1 адреса (кодопреобраэователь) предназначен дляформирования адреса очередной микрокоманды в соответствии с содержимымполя б ожидаемых логических условийи поля 7 модификации регистра микрокоманд 4 и кодом операций, подаваемымсо входа устройства 21.Регистр 2 адреса микрокоманд предназначен для хранения адреса микрокомгнды, сформированного формироватет.лем 1,Блок 3 памяти микрокоманд преднаэначен для хранения и выдачи микрокоманд в регистр 4 в соответствиис адресом микрокоманды, записанным врегистре 2,Регистр 4 предназначен для хранения микрокоманды, считанной иэ блока3, при этом в поле 5.микрооперацийхранится код микроопераций, в поле божидаемых логических условий -код ожидаемых логических условий,необходимый для перехода х выполнению следующей микрокоманды, в поле 7 модификации - код модификации,позволяющий совместно с кодом ожидаемых логических условий образоватьадрес следующей микрокоманды, Еслив микрокоманде нет ожидаемых логических условий, то адрес следующеймикрокоманды определяется непосредственно содержимым полей 6 и 7 регистра 4 микрокоманд. Поле 8 метки регистра микрокоманд 4 позволяет фиксировать наличие ожидаемых логических условий в данной микрокоманде(например, путем записи в этом поле "1") или их отсутствие (например, путем записи в нем 0 ).н 1Блок элементов И 9 предназначендля выдачи кода микроопераций навыход 22 устройства только в томслучае, если триггер 18 находитсяв нулевом состоянии. Блок элементов И 10,предназначен для выдачи кода ожидаемых логических условий в формирователь 1 адреса только в том случае, если триггер 18 находится в нулевом состоянии,5 955057 6Блок элементов И 11 предназначен формировдтель 1 адреса выдает адресдля выдачи кода модификации в фор-. первой микрокоманды на вход регистмирователь 1 адреса только в том слу- ра адреса 2 микрокоманд. С регистрачае, если триггер 18 находится в адреса 2 микрокоманд адрес выдаетсянулевом состоянии. на первые входы блока 3 памяти. ПриБлок элементов И 12 предназначен поступлении на второй вход блока 3длля выдачи кода ожидаемых логичес- тактового импульса из этого блокаких условий нх условий на вход буферного регист- считывается первая микрокоманда, кора 13 только в том случае, если в торая поступает на вход регистраполе 8 метки записи информация о на и запоминается в нем. Указанный такличии ожидаемых логических условий товый импульс поступает с синхров данной микрокоманде. низирующего входа 24 устройства чеБуферный регистр 13 предназначен рез элемент И 20, управляемый потендля хранения кода ожидаемых логи- циальным сигналом с выхода триггецеских условий. 15;ра 18.Узел 14 конца ожидания предназначен для выдачи сигнала только в том Бсли в считываемой микрокомандеслучае, если на вторые входы 23 пос- нет ожидаемых логических условий,тупает информация о выполнении ожи- то содержимое поля 5 микрооперацийдаемого логического условия, код кото 20,регистра 4 микрокоманд поступаетрого записан в буферном регистре 13 на первый вход блока элементов И 9.Вход 21 устройства предназначен При этом на второй вход блока эледля подачи в устройство кода опера- ментов И 9 поступает сигнал с нулевого выхода второго триггера 18Выход 22 устройства предназначен ЪЪ поскольку в исходном состояниидля выдачи кодов микроопераций на триггер 18 находится в нулевомуправляемые объекты. состоянии. Указанный потенциальныйВход 23 устройства предназначен сигнал разрешает прохождение индля подачи в устройство информации формации, записанной в поле 5 микроо выполнении ожидаемого логического зр операций регистра 4 микрокоманд че- .рез блок элементов И 9. Таким обраСинхронизирующий вход 24 устрой- зом, код микрооперации поступает. ства предназначен для подачи в уст- на выходы 22 микропрограммного устройство тактовых импульсов. ройства управления на исполнение. ИзГруппа элементов И 25 узла 14 . з поля 6 ожидаемых логических условийконца ожидания (фиг. 2) предназна- в регистре 4 микрокоманд соответстцена для выдачи сигналов на входы вующая информация поступает на перэлемента ИЛИ 26 только в том случае, вый вход блока элементов И 110. Весли на первые входы узла конца ожида-. то же время на второй вход блока элечния подается код данного ожидаемого 4 ментов И 10 поступает потенциальныилогического условия из буферного ре- сигнал с нулевого выхода триггерагистра 13, а на вход устройства 23 18, а поскольку последний находитсяпоступает информация о выполнении в исходном состоянии, то этот сигналэтого же ожидаемого логического . разрешает прохождение информации, записанной в поле 6 ожидаемых логичес-4%Элемент ИЛИ 26 узла 14 конца ожи- ких условий регистра 4, через блок,вания предназначен для выдачи сигна- элементов И 10. Укаэанная .информацияла на выход узла 14 конца ожидания поступает при этом на вход Формитолько в тех случаях, когда группа рователя 1 адреса и на второй входэлементов И 25 формирует хотя бы блока элементов И 12,один сигнал на его выходах. Из поля 7 модификации регистра 4Микропрограммное устройство управ- соответствующая информация поступаетления работает следующим образом. на первый вход блока элементов И 11.В исходном состоянии все элемен- Одновременно на второй вход этоготы памяти находятся в нулевом сос" блока элементов И поступает потентоянии. Работа микропрограммного уст- циальный сигнал с нулевого выходаройства управления начинается по триггера 18. Этот сигнал разрешаети иходу кода операции на его вход прохождение информации из поля 721. В соответствии с этим кодом модификации регистрачерез блприхз блок7 9550элементов И 11 на вход формирователя 1 адреса.Ввиду того, что рассматриваетсярежим работы микропрограммного устройства управления, когда считывае-мые микрокоманды не содержат ожидаемых логический условий, то в поле8 метки регистра 4 отсутствует признак наличия в данной микрокомандеожидаемых логический условий (едини 1"ца). Вследствие этого через блокэлементов И 12 на буферный регистр13 информация с поля 6 ожидаемыхлогических условий регистра 4 непроходит. Кроме того, и на второй 13вход элемента И 15 с поля 8 меткирегистра 4 информационный сигнал(единица) также не подается.формирователь 1 адреса на основе информации, поступающей на его 20входы, вырабатывает адрес следующеймикрокоманды. Процесс обработки вустройстве сформированного адресаидентичен рассмотренному до тех пор,пока не будет считана микрокоманда, 25содержащая ожидаемые логические условия.В этом случае в поле 8 метки . регистра 4 содержится признак наличия ожидаемых логических условий Зв("единица"). При этом наряду с описанным процессом обработки информации в микропрограммном устройствеуправления дополнительно реализуется следующее.Единица, содержащаяся в поле 8метки регистра микрокоманд 4, поступает на первый вход блока элементовИ 12, тем самым разрешая прохождениекода ожидаемых логических условий с выхода блока элементов И 10 на первыйвход буферного регистра 13. С буферного регистра 13 информация ожидаемых логических условиях выдается навход узла 14 конца ожидаемых. При этом на выходе узла 14 конца ожидаемых не будет формироваться сигнал до тех пор, пока на его второй вход не поступит информация о выполнении .;данного ожидаемого логического условия со входа 23.Кроме того, наличие в поле 8 метки регистра 4 единицы обуславливает появление на выходе элемента И 15 управляющего си"нала, так как триггер 18 находится в нулевом состоянии ф Указанный управляющий сигнал устанавливает триггер 16 в единичное состояние. При этом на выходе триг 57 8гера 16 формируется разрешающий сигнал, поступающий на первый вход элемента И 17. Наличие этого сигнала разрешает прохождение через элементИ 17 тактовых импульсов, поступающих с синхронизирующего входа 24 микропрограммного устройства управления.1 о приходу тактового импульса второйрлемент И 17 выдает сигнал на единич,ный вход триггера 18 и устанавливает рго в единичное состояние. Пока такговый импульс пройдет элемент И 17установит триггер 18 в единичное состояние, он поступит на тактовыйвход блока 3 через элемент И 20.Тем самым из блока 3 инициируетсясчитывание очередной микрокоманды.После перехода триггера 18 в единичное состояние на его нулевом выходе прекращает Формироваться разре.шающий сигнал, подававшийся ранее на вторые входы блоков элементов И 9-11 соответственно и на первыевходы элементов И 15-20. Одновременно на единичном выходе триггера 18 вырабатывается сигнал, устанавливающий триггер 16 в нулевое состояние. Таким образом,инФормация о следующей микрокоманде, содержащаяся на регистре 4 микрокоманд через блоки элементов И 9- 12 не проходит. Кроме того, отсутствие потенциального сигнала на втором выходе триггера 18 запрещает прохождение тактовых импульсов через элемент И 20 на тактовый вход блока 3. Тем самым запрещается считывание следующей микрокоманды.С приходом на второй вход. узла 14 конца ожидания информации о выполнении данного ожидаемого логического условия на его выходе формируется сигнал. Этот сигнал устанавливает триггер 18 в нулевое состояние, а с появлением потенциального сигнала на нулевом выходе триггера 18 через элемент И 19 обнуляет буферный регистр 13, Таким образом, следующая микрокоманда, хранящаяся в регистре 4 микрокоманд, начинает обрабатываться согласно алгоритму, изложенному выше.Таким образом, быстродействие, а следовательно, экономичность предлагаемого устройства повышается,за счет совмещения операции обработки поступающих логических условий и считывания очередной микрокоманды из бло ка.памяти.9. 9550формула изобретения Микропрограммное устройство управления, содержащее блок памятимикрокоманд, регистр микрокоманд, регистр адреса микрокоманд, формирователь адреса и узел конца ожидания, причем вход логических условий устройства соединен с первым входом формирователя адреса, выход которо О го соединен со входом регистра адреса микрокоманд, выход которого соединен с адресным входом блока:памяти микро- команд,. выход которого соединен со входом регистра микрокоманд, о т - И л и -: а ю щ е е с я тем, что, с целью "овышения быстродействия, оно содержит четыре блока элементов И буферный регистр, четыре элемента И и два триггера, причем вход первого рф блока элементов И является информационным выходом устройства, первые ". входы блоков элементов И соединены с соответствующими входами регистра микрокоманд, вторые входы первого, 2 З второго и третьего элементов И соединены с нулевым выходом первого триггера и первыми входами первого, второго и третьего элементов И, выходы второго и третьего блоков элементов И соединены соответственно со вторым и третьим входами формирователя адреса, выход второго блока элементов И соединен со вторым входом четвертого блока элементов И выЭЗ 57 10ход которого соединен с первым входом буферного регистра, группа выходов которого соединена с первой группой входов узла. конца ожидания, второй вход буферного регистра соединен с выходом третьего элемента И, второй вход которого соединен с выходом узла конца ожидания и нулевым входом первого триггера единичный вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с синхронизирующим входом устройства и вторым входом второго элемента И, второй вход четвертого элемента И соединен с выходом второго триггера, нулевой вход которого соединен.с единичным выходом первого триггера единичный вход второго триггера соединен с выходом первого элемента И, второй вход которого соединен со вторым входом четвертого блока элементов И, тактовый вход .блока памяти микро- команд соединен с выходом второго элемента И, вторая группа входов узла конца ожидания соединена с разрешаоцими входами устройства.Источники информации,принятые во внимание при экспертизе1 Авторское свидетельство СССРИ 331387, кл. 6 06 Е 9/22, 1972,2. Авторское свидетельство СССРй 167350, кл. 6 06 Р 9/22, 1975955057НИИПИ Заказ 6438/5Тираж 731 Подписное Филиал ППП "Патент",

СмотретьЗаявка

2972602, 12.08.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СИДОРЕНКО ВАЛЕНТИН ИВАНОВИЧ, ЗАХАРЕНКО АЛЕКСАНДР ВЛАДИМИРОВИЧ, ЕМЕЛЬЯНОВ НИКОЛАЙ АНТОНИЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/6-955057-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Регулируемая гидромуфта