Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

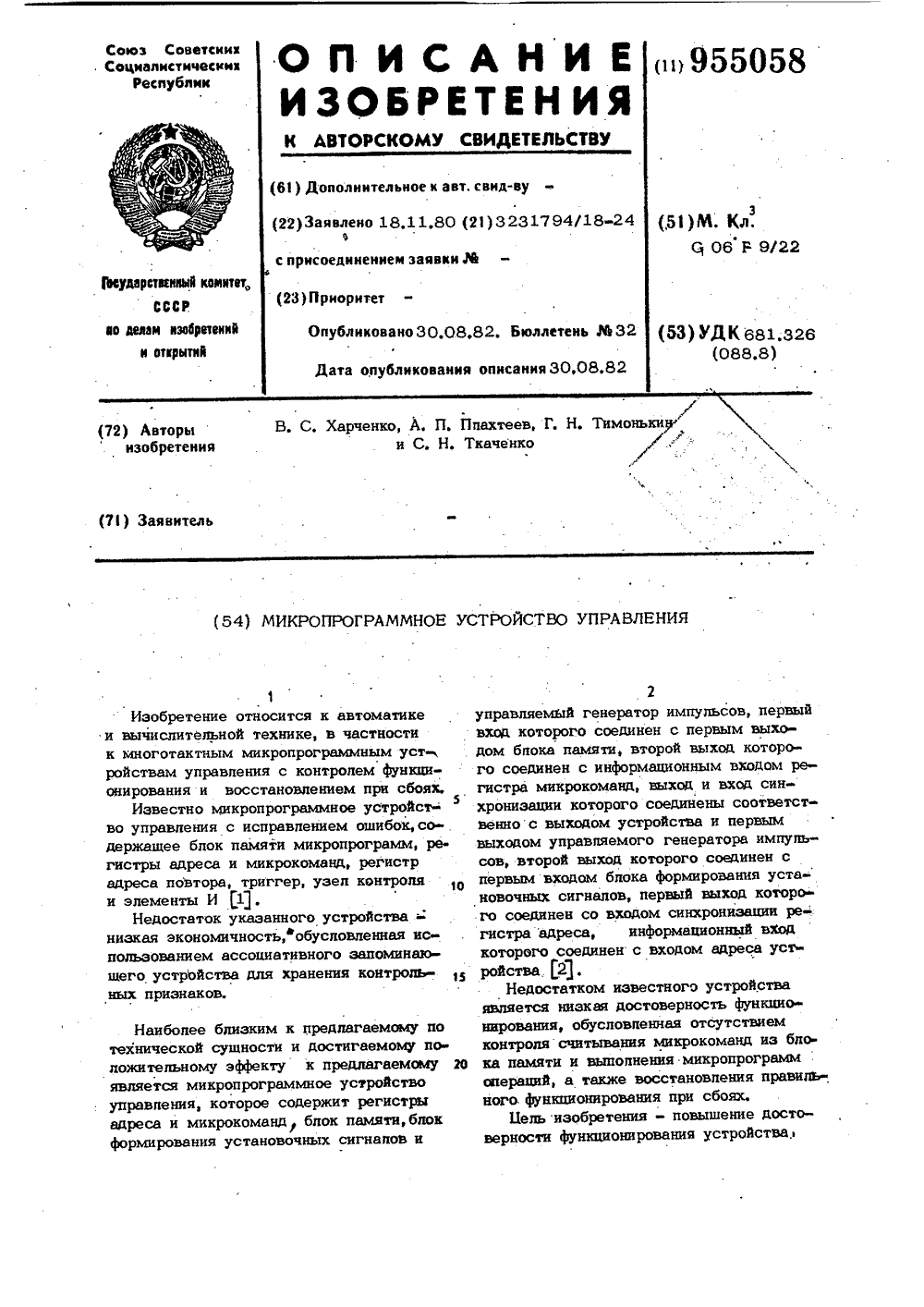

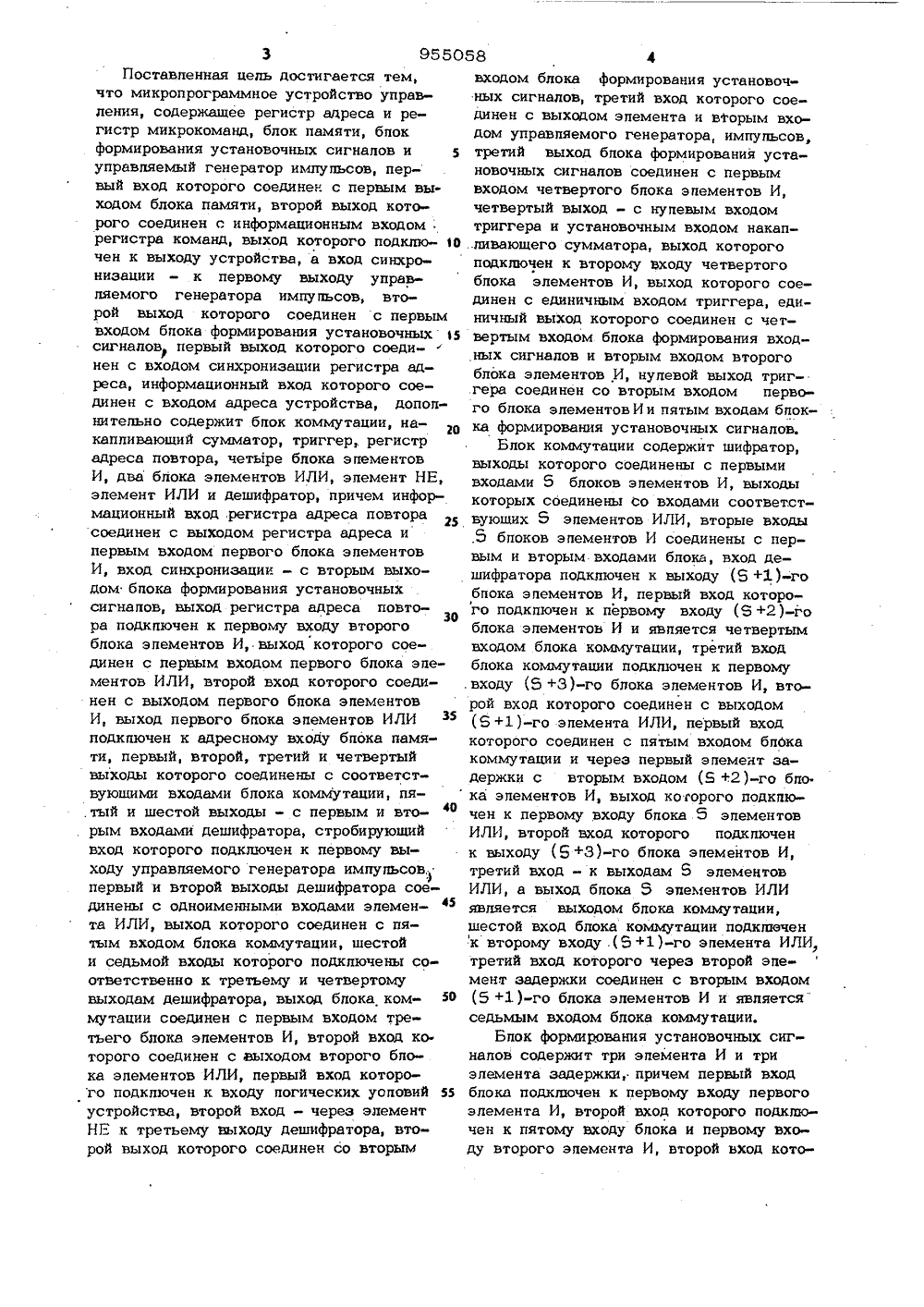

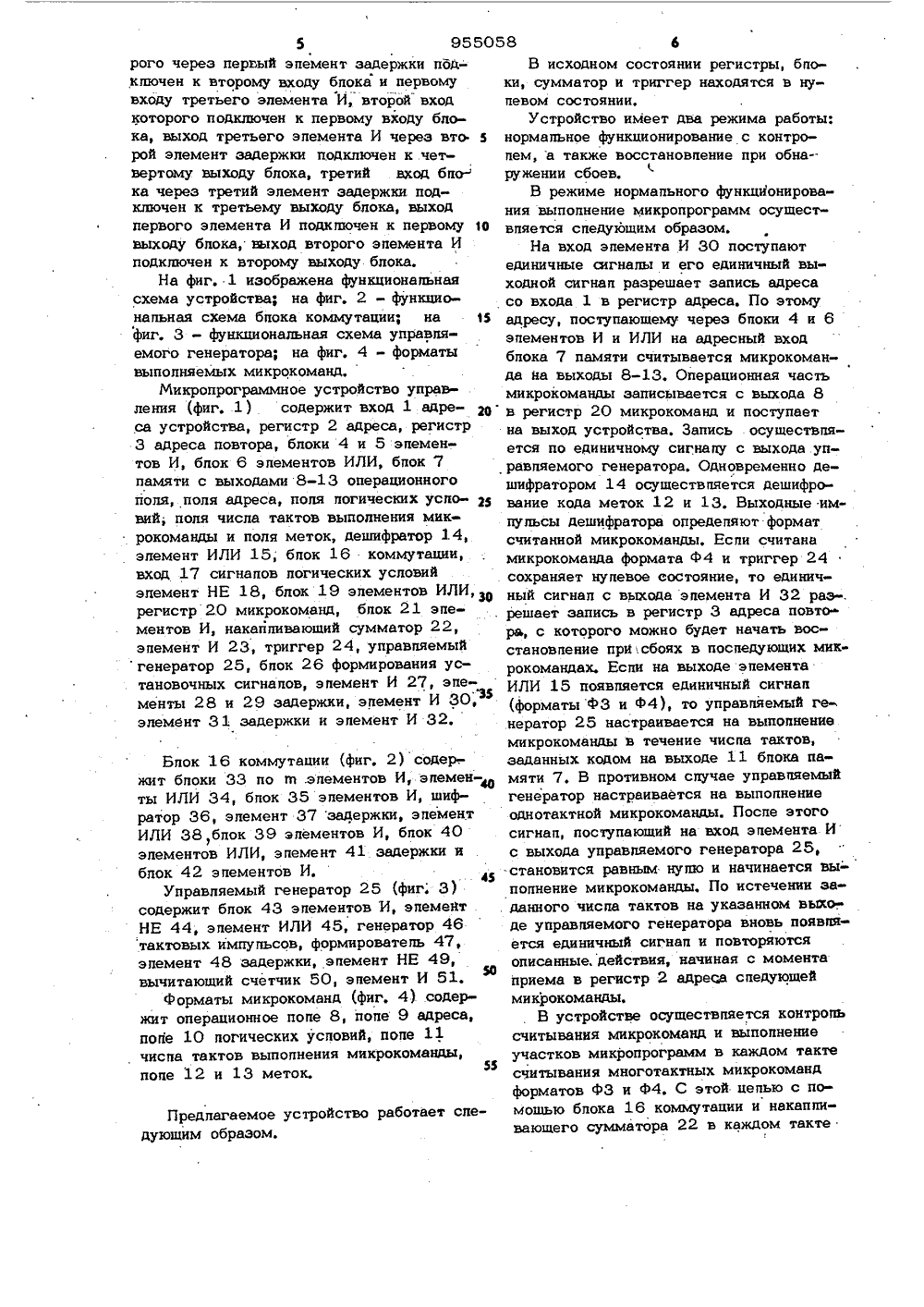

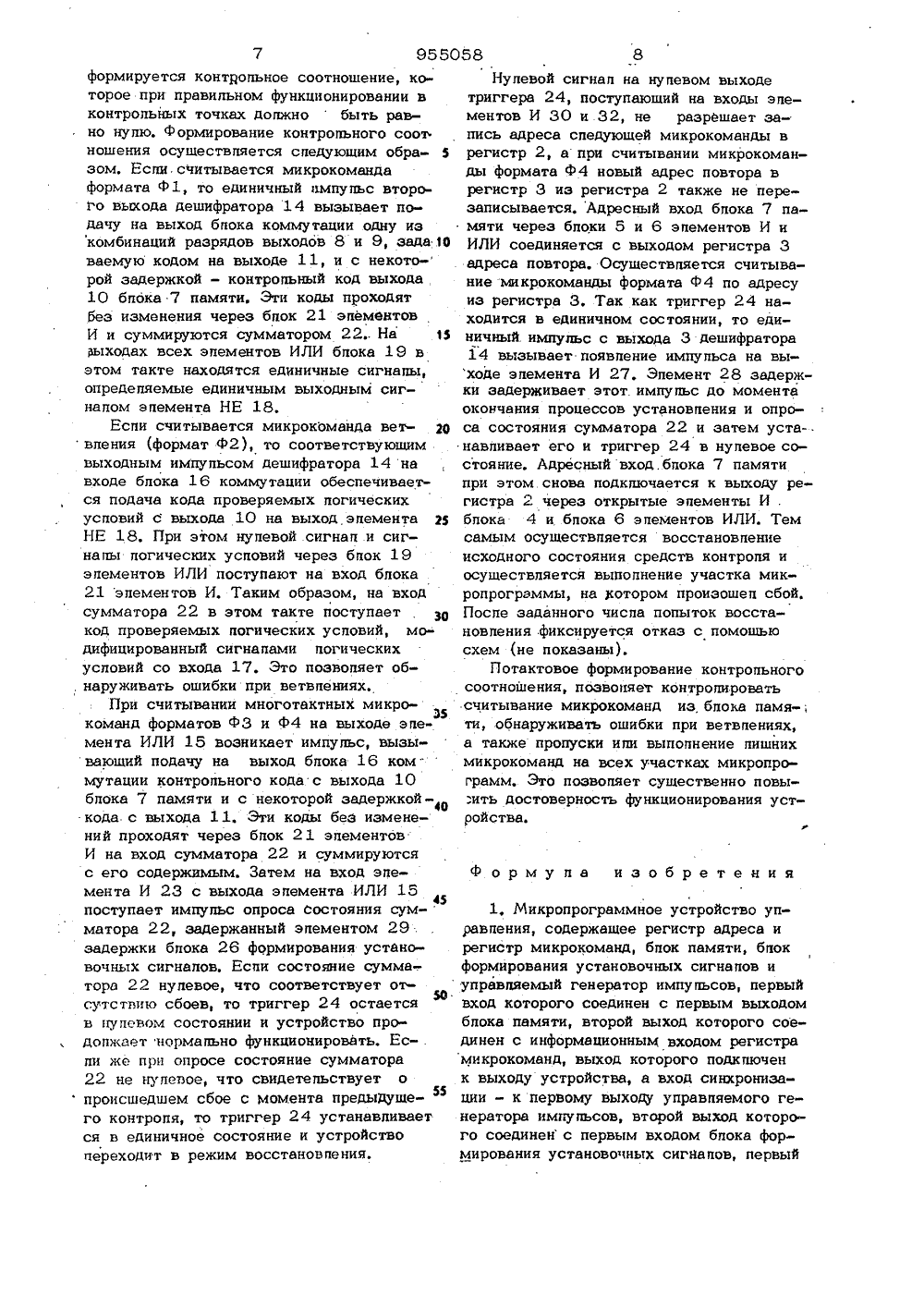

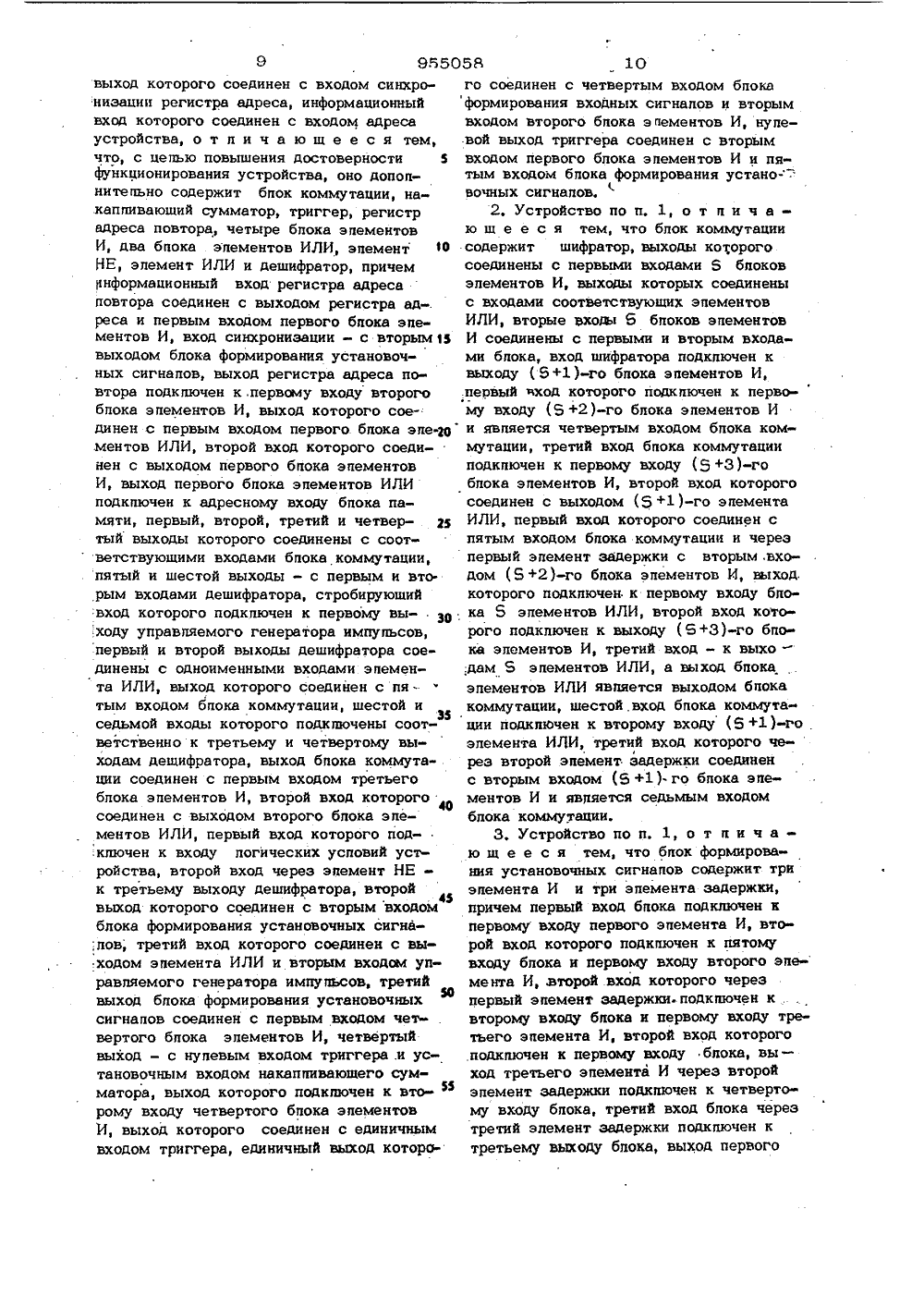

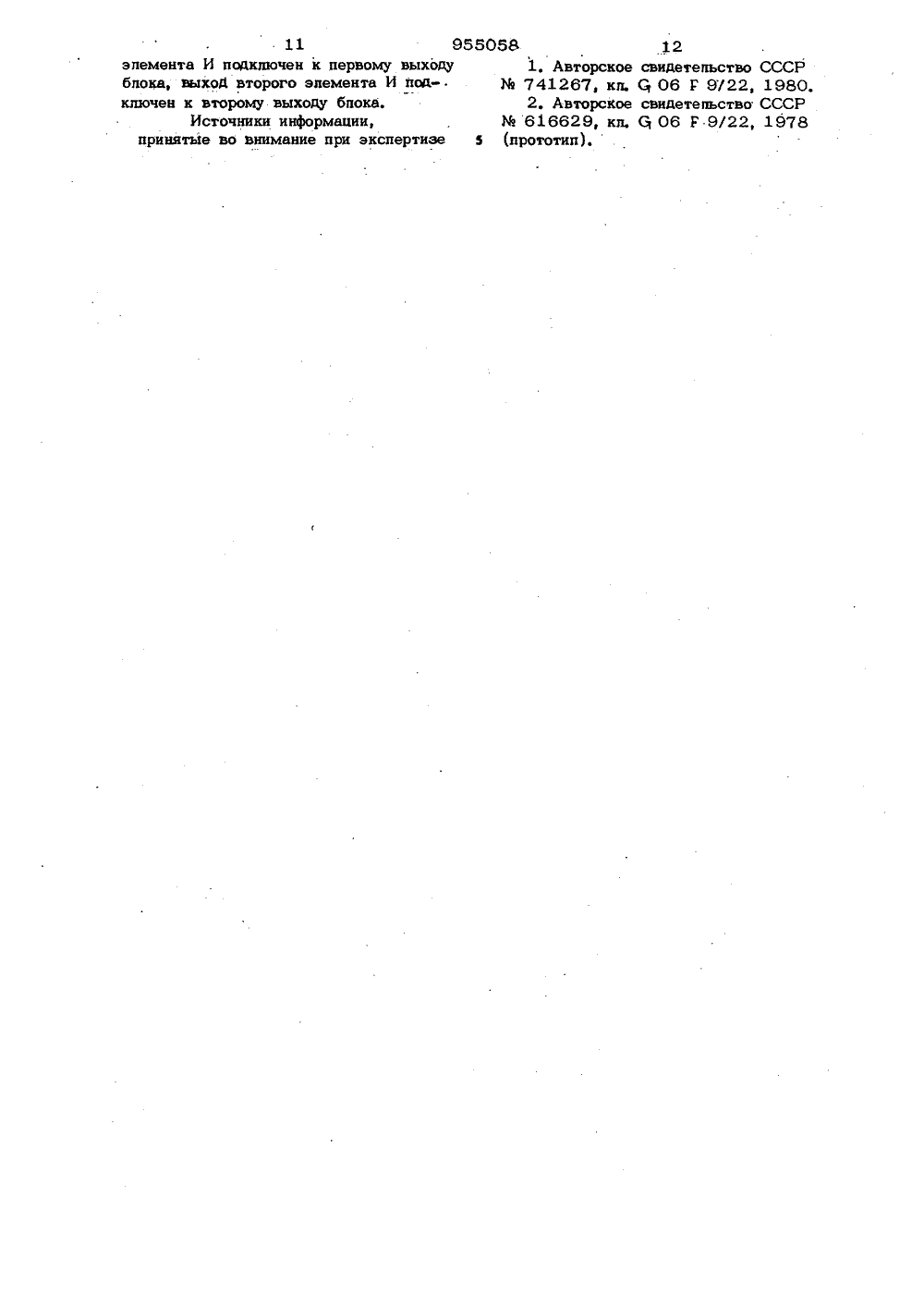

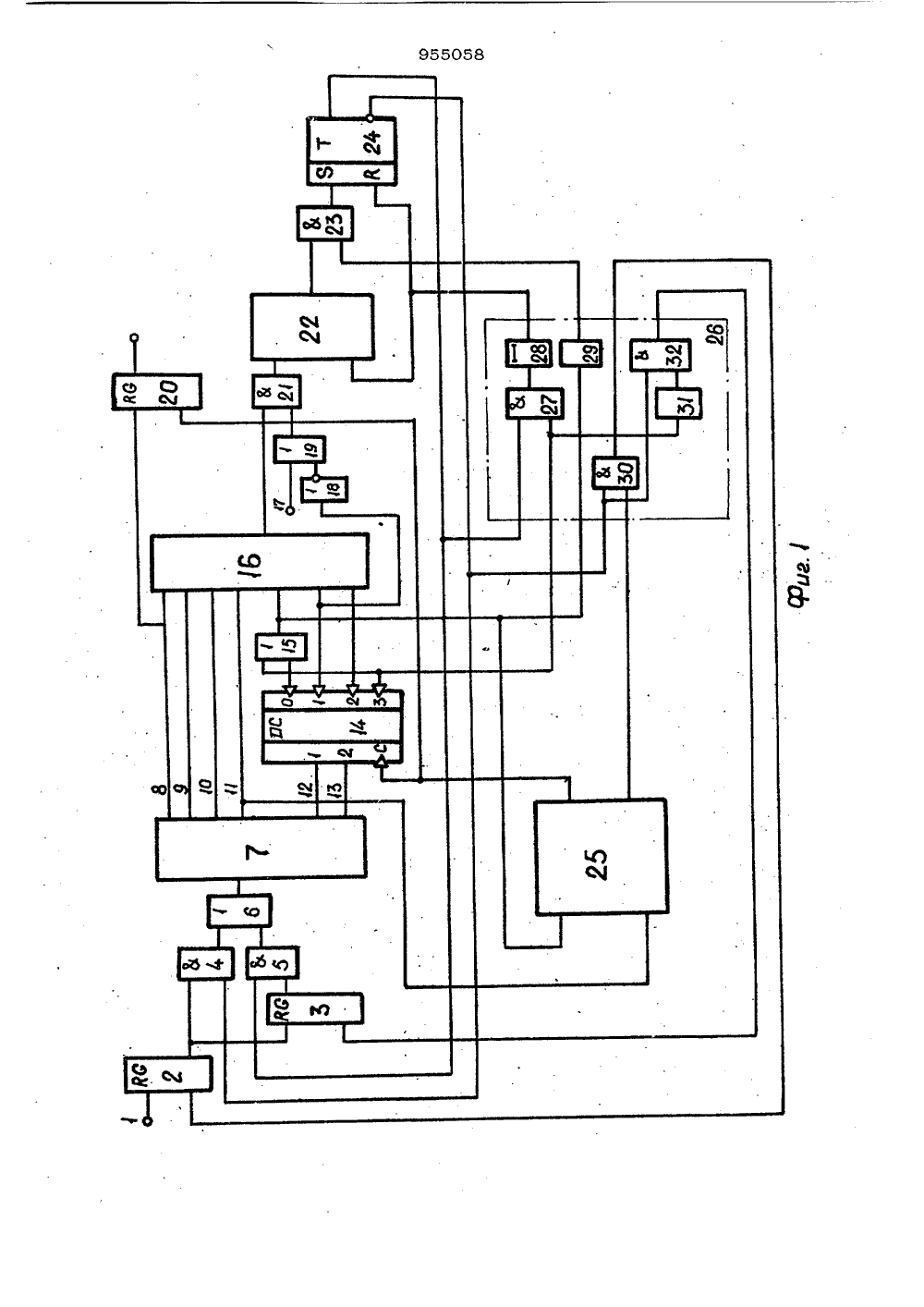

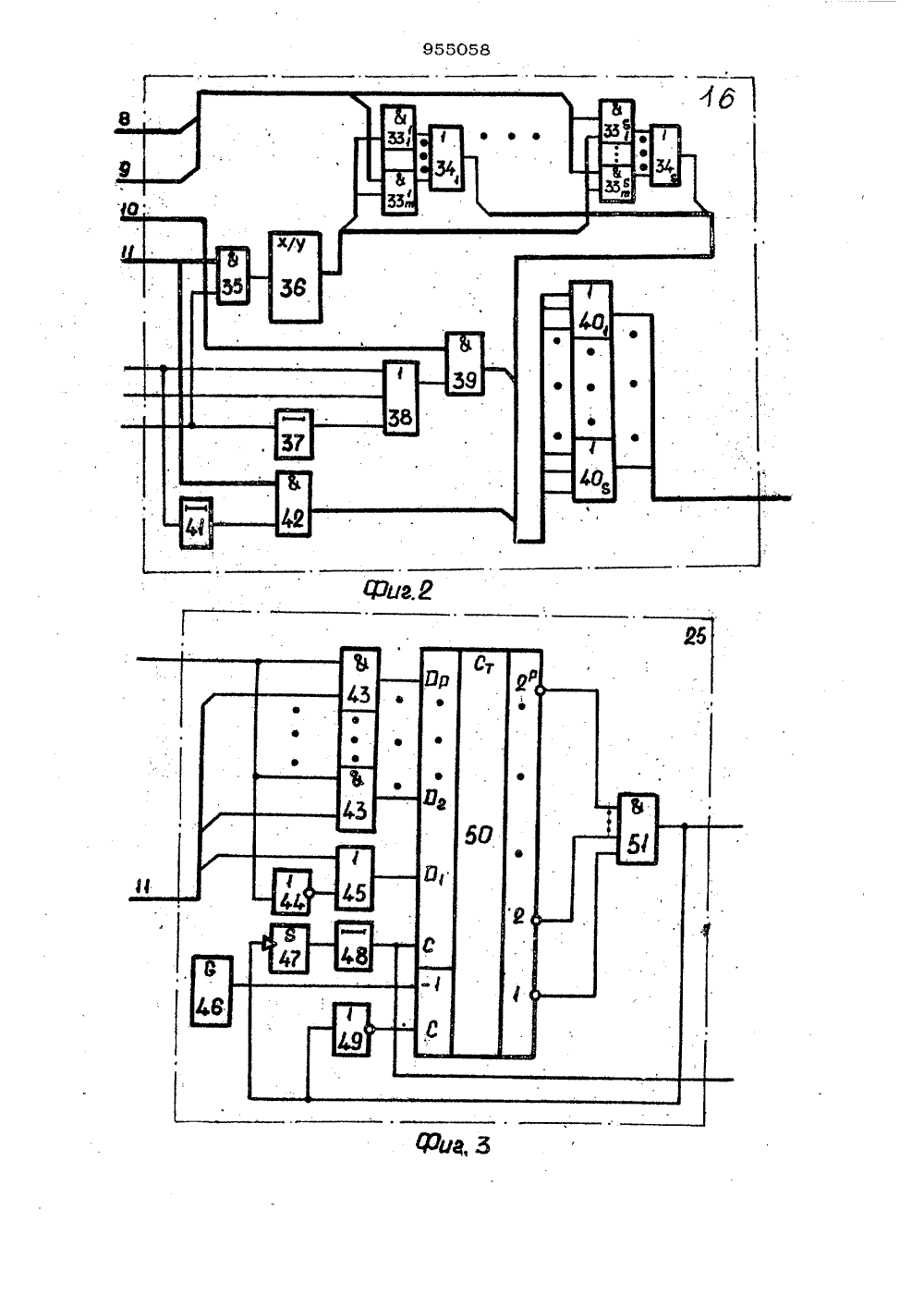

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветсиикСоциалистическиеРеспублик(23) Приоритет ЪеудврстееииыЯ кемитет,СССР ав лелем изебретеииЯ и втерытий(088.8) Опубликоваио 30.08,82. Бюллетень Рй 32 Дата опубликования описания 30,08.82(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ 1Изобретение относится к автоматикеи вычислительной технике, в частностик ыноготактным микропрограммным уст-,ройствам управления с контролем функционирования и восстановлением прн сбоях.Известно микропрограммное устройст-5во управления с исправлением ошибок,содержащее блок памяти микропрограмм, регистры адреса и микрокоманд, регистрадреса повтора, триггер, узел контроляи элементы И 111,Недостаток указанного устройства -.низкая экономичностьфобусловленная использованием ассоциативного запоминающего устрЬйства для хранения контрольных признаков,Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту к предлагаемому 20 является микропрограммное устройство управления, которое содержит регистры адреса и микрокоманд блок памяти, блок формирования установочных сигналов и 2управляемый генератор импульсов, первыйвход которого соединен с первым выходом блока памяти, второй выход которого соединен с информационным входом регистра микрокоманд, выход и вход синхронизации которого соединены соответственно с выходом устройства и первымвыходом управляемого генератора импульсов, второй выход которого соединен спервым входом блока формирования уста-новочных сигналов, первый выход которого соединен со входом синхронизации ре-гистра адреса, информационный входкоторого соединен с входом адреса устройства Я,Недостатком известного устройстваявляется низкая достоверность функциопирования, обусловленная отсутствиемконтроля считывания микрокоманд из бпо.ка памяти и выполнения микропрограммопераций а также восстановления правильного функционирования при сбоях,Цель изобретения - повышение достоверности функционирования устройства,3 9550Поставленная цель достигается тем,что микропрограммное устройство управпения, содержащее регистр адреса и регистр микрокоманд, блок памяти, блокформирования установочных сигналов и 5управляемый генератор импульсов, первый вход которого соединен с первым выходом блока памяти, второй выход которого соединен с информационным входомрегистра команд, выход которого подюпо Очен к выходу устройства, а вход синхронизации - к первому выходу управляемого генератора импупьсов, второй выход которого соединен с первымвходом бпока формирования установочных 15сигналов первый выход которого соедиУнен с входом синхронизации регистра адреса, информационный вход которого соединен с входом адреса устройства, допопнительно содержит бпок коммутации, накаппивающий сумматор, триггер,. регистр адреса повтора, четыре блока эпементов И, два блока эпементов ИЛИ, элемент НЕ,элемент ИЛИ и дешифратор, причем информационный вход .регистра адреса повтора соединен с выходом регистра адреса и первым входом первого блока эпементов И, вход синхронизации - с вторым выходом бпока формирования установочных сигналов, выход регистра адреса повтора подкпючен к первому входу второго блока элементов И,.выход которого соединен с первым входом первого бпока элементов ИЛИ, второй вход которого соединен с выходом первого блока элементов И, выход первого блока эпементов ИЛИ подкпючен к адресному входу бпока памяти, первый, второй, третий и четвертый выходы которого соединены с соответствующими входами блока коммутации, пя.тый и шестой выходы - с первым и вто 40 . рым входами дешифратора, стробирующий вход которого подключен к первому выходу управляемого генератора импупьсов, первый и второй выходы дешифратора соединены с одноименными входами эпемен 45 та ИЛИ, выход которого соединен с пятым входом блока коммутации, шестой и седьмой входы которого подключены соответственно к третьему и четвертому выходам дешифратора, выход блока ком мутации соединен с первым входом третьего бпока элементов И, второй вход ко. торого соединен с выходом второго блока элементов ИЛИ, первый вход которого подключен к входу погических уоповий 55 устройства второй вход - через элемент НГ к третьему выходу дешифратора, второй выход которого соединен со вторым 58 4входом блока формирования установочных сигналов, третий вход которого соединен с выходом эпемента и вторым входом упрввпяемого генератора, импульсов,третий выход блока формирования установочных сигналов соединен с первымвходом четвертого блока эпементов И,четвертый выход - с нупевым входомтриггера и установочным входом накапливающего сумматора, выход которогоподключен к второму входу четвертогобпока эпементов И, выход которого соединен с единичным входом триггера, единичный выход которого соединен с четвертым входом бпока формирования входных сигналов и вторым входом второго блоке элементов И, нулевой выход триггера соединен со вторым входом первого блока элементовИи пятым входам бпокка формирования установочных сигналов.Блок коммутации содержит шифратор, выходы которого соединены с первыми входами 5 блоков элементов И, выходы которых соединены со входами соответствующих 5 элементов ИЛИ, вторые входы ,5 блоков эпементов И соединены с первым и вторым входами блока, вход дешифратора подключен к выходу (б +1)-гобпока эпементов И, первый вход которого подкпючен к первому входу (8+2)-гоблока элементов И и является четвертымвходом блока коммутации, третий входблока коммутации подключен к первомувходу (5 +3)-го блока элементов И, второй вход которого соединен с выходом(8+1)-го элемента ИЛИ, первый входкоторого соединен с пятым входом бпОка коммутации и через первый эпемент задержки с вторым входом (Я +2)-го бпо ка элементов И, выход которого подкпючен к первому входу бпока 5 элементов ИЛИ, второй вход которого подключен к выходу (5+3)-го бпока эпементов И,третий вход - к выходам 5 элементов ИЛИ, а выход бпока 5 эпементов ИЛИ является выходом блока коммутации, шестой вход блока коммутации подкшечен к второму входу (5+1)-го эпементв ИЛИ, третий вход которого через второй эпемент задержки соединен с вторым входом (5+1)-го блока элементов И и явпяется седьмым входом блока коммутации,Впок формирования установочных сигналов содержит три эпемента И и три элемента задержки, причем первый вход блока подключен к первому входу первого элемента И, второй вход которого подкшо чен к пятому входу блока и первому входу второго эпемента И, второй вход кото5 95505рого через первый элемент задержки подкшочен к второму входу блока и первомувходу третьего элемента И, второй входкоторого подключен к первому входу блока выход третьего элемента И через вто 5рой элемент задержки подключен к четвертому выходу блока, третий вход бпо-ка через третий элемент задержки подключен к третьему выходу блока, выходпервого элемента И подкпючен к первому 10выходу блока, выход второго эпемента Иподключен к второму выходу блока.На фиг, 1 изображена функционапьнаясхема устройства; на фиг, 2 - функционапьная схема бпока коммутации; на 15фиг, 3 - функциональная схема управляемого генератора; на фиг. 4 - форматывыполняемых микрокоманд,Микропрограммное устройство управпения (фиг, 1) содержит вход 1 адреса устройства, регистр 2 адреса, регистр3 адреса повтора, блоки 4 и 5 эпементов И, блок 6 элементов ИЛИ, бпок 7памяти с выходами 8-13 операционногополя, поля адреса, поля погических условий; поля числа тактов выполнения микрокоманды и полн меток, дешифратор 14,элемент ИЛИ 15 бпок 16 коммутации,вход 17 сигнапов логических условийэлемент НЕ 18, блок 19 элементов ИЛИ,регистр 20 микрокоманд, бпок 21 эпементов И, накаппиваюший сумматор 22,эпемент И 23, триггер 24, управпяемыйгенератор 25, бпок 26 формирования установочных сигнапов, эпемент И 27, элементы 28 и 29 задержки, эпемент И 30,Иэлемент 31 задержки и эпемент И 32,Блок 16 коммутации (фиг. 2) содержит блоки ЗЗ по а .эпементов И, эпементы ИЛИ 34, блок 35 элементов И, шифратор 36, элемент 37 задержки, элементИЛИ 38 блок 39 эпементов И, блок 40элементов ИЛИ, эпемент 41 задержки иблок 42 эпементов И.43Управляемый генератор 25 (фиг. 3)содержит бпок 43 эпементов И, эпемент .НЕ 44, эпемент ИЛИ 45, генератор 46тактовых импульсов формироватепь 47,элемент 48 задержки, эпемент НЕ 49,Ювычитаюший счетчик 50 эпемент И 51.Форматы микрокоманд (фиг, 4) содержит операционное попе 8 попе 9 адреса,попе 10 погических условий, попе 11чиспа тактов выпопнения микрокоманды,попе 12 и 13 меток,И Предлагаемое устройство работает следующим образом. 8 6В исходном состоянии регистры, бпоки, сумматор и триггер находятся в нупевом состоянии.Устройство имеет два режима работы;нормапьное функционирование с контропем, а также восстановпение при обна-.ружении сбоев.В режиме нормапьного функционирования выпопнение микропрограмм осуществляется спедуюшим образом.На вход эпемента И 30 поступаютединичные сигналы и его единичный выходной сигнап разрешает запись адресасо входа 1 в регистр адреса. По этомуадресу, поступающему через бпоки 4 и 6элементов И и ИЛИ на адресный входблока 7 памяти считывается микрокоманда на выходы 8-13, Операционная частьмикрокоманды записывается с выхода 8в регистр 20 микрокоманд и поступаетна выход устройства, Запись осушествпяется по единичному сигнапу с выхода управляемого генератора. Одновременно дешифратором 14 осуществпяется дешифрование кода меток 12 и 13. Выходные импульсы дешифратора определяют форматсчитанной микрокоманды. Если считанамикрокоманда формата ф 4 и триггер 24сохраняет нупевое состояние, то единичный сигнал с выхода эпемента И 32 раз-,решает запись в регистр 3 адреса повтора, с которого можно будет начать восстановление при,сбоях в поспедуюших микрокомандах. Еспи на выходе эпементаИЛИ 15 появляется единичный сигнап(форматы ФЗ и ф 4), то управпяемый ге"нератор 25 настраивается на выпопнениемикрокоманды в течение чиспа тактов,заданных кодом на выходе 11 бпока памяти 7, В противном спучае управпяемыйгенератор настраивается на выпопнениеоднотактной микрокоманды. После этогосигнап, поступающий на вход эпемента Ис выхода управпяемого генератора 25,становится равным нупю и начинается вы-полнение микрокоманды. По истечении заданного чиспа тактов на указанном выхо.де управпяемого генератора вновь появпяется единичный сигнап и повторяютсяописанные, действия, начиная с моментаприема в регистр 2 адреса спедующеймикрокоманды,В устройстве осушествпяется контропьсчитывания микрокоманд и выполнениеучастков микропрограмм в каждом тактесчитывания многотактных микрокомандформатов ФЗ и ф 4. С этой цепью с цомошью блока 16 коммутации и накаппивающего сумматора 22 в каждом тактеформируется контдопьное соотношение, которое при правильном функционировании вконтропьных точках должнобыть равно нулю. формирование контрольного соотгношения осуществляется спедующим образом. Если. считывается микрокомандаформата ф 1, то единичный ампупьс второго выхода дешифратора 14 вызывает подачу на выход бпокв коммутации одну изкомбинаций разрядов выходов 8 и 9, зада 10ваемую кодом на выходе 11, и с некото-рой задержкой - контропьный код выхода10 бпока 7 памяти. Эти коды проходятбез изменения через бпок 21 эпементовИ и суммируются сумматором 22 На 15выходах всех эпементов ИЛИ блока 19 вэтом такте находятся единичные сигнапы,определяемые единичным выходным сигнапом эпемента НЕ 18.Еспи считывается микрокоманда вез 20вления (формат ф 2), то соответствующимвыходным импупьсом дешифратора 14 навходе блока 16 коммутации обеспечивается подача кода проверяемых логическихусповий с выхода 10 на выход эпемента 25НЕ 18, При этом нулевой сигнап и сигнапы логических усповий через бпок 1 9элементов ИЛИ поступают на вход блока21 элементов И. Таким образом, на входсумматора 22 в этом такте поступаеткод проверяемых погических условий, модифицированный сигнапами погическихусловий со входа 17, Это поэвопяет об, наруживать ошибки при ветвпениях,При считывании многотактных микрокоманд форматов ф 3 и ф 4 на выходе эпемента ИЛИ 15 возникает импульс, вызывающий подачу на выход бпока 16 коммутации контрольного кода с выхода 10бпока 7 памяти и с некоторой задержкойкода с выхода 11. Эти коды беэ изменений проходят через бпок 2 1 элементовИ на вход сумматора 22 и суммируютсяс его содержимым. Затем на вход эпемента И 23 с выхода элемента ИЛИ 15поступает импульс опроса состояния сумматора 22, задержанный эпементом 29задержки блока 26 формирования установочных сигналов, Еспи состояние сумма-.тора 22 нулевое, что соответствует от 50сутствию сбоев, то триггер 24 остаетсяв цупевом состоянии и устройство продопжает нормапьно функционировать, Если же при опросе состояние сумматора22 не нулевое, что свидетепьствует опроисшедшем сбое с момента предыдуше 55го контропя, то триггер 24 устанавливается в единичное состояние и устройствопереходит в режим восстановпения. Нулевой сигнал на нулевом выходе триггера 24, поступающий на входы эпементов И 30 и.32, не разрешает запись адреса спедуюшей микрокоманды врегистр 2, а при считывании микрокоманды формата Ф 4 новый адрес повтора врегистр 3 из регистра 2 также не пере- записывается, Адресный вход блока 7 памяти через блоки 5 и 6 эпементов И и ИЛИ соединяется с выходом регистра 3 адреса повтора. Осушествпяется считывание микрокоманды формата ф 4 по адресу иэ регистра 3, Так как триггер 24 находится в единичном состоянии, то единичный. импульс с выхода 3 дешифратора 14 вызывает появление импульса на выходе элемента И 27. Элемент 28 задержки задерживает этот. импупьс до моментаокончания процессов уствновпения и опроса состояния сумматора 22 и затем уста-. навпивает его и триггер 24 в нупевое состояние, Адресный вход. блока 7 памяти при этом снова подключается к выходу регистра 2 через открытые эпементы И . бпока 4 и блока 6 эпементов ИЛИ. Тем самым осуществляется восстановпение исходного состояния средств контропя и осушествпяется выполнение участка микропрограммы, на котором произощеп сбой, Поспе заданного числа попыток восстановпения фиксируется отказ с помощью схем (не показаны).Потвктовое формирование контропьного соотношения, позвопяет контропировать считывание микрокоманд иэ блока памя-; ти, обнаруживать ошибки при ветвпениях, а также пропуски ипи выпопнение лишних микрокоманд на всех участках микропрограмм, Это позвопяет существенно повы:ить достоверность функционирования устройства.ф орму па изобретения1, Микропрограммное устройство управпения, содержащее регистр адреса и регистр микрокоманд, бпок памяти, бпок формирования установочных сигнапов иуправпяемый генератор импупьсов, первыйвход которого соединен с первым выходом блока памяти, второй выход которого соединен с информационным. входом регистра микрокоманд, выход которого подкпючен к выходу устройства, а вход синхронизации - к первому выходу управпяемого генератора импульсов, второй выход которого соединен с первым входом бпокв формирования установочных сигнапов, первый955058 выход которого соединен с входом синхронизации регистра адреса, информационный вход которого соединен с входом адреса устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверностифункционирования устройства, оно допопнитепьно содержит бпок коммутации, накаппиввющий сумматор, триггер, регистр адреса повтора, четыре блока эпементов И, два бпока эпементов ИЛИ, эпемент ф НЕ, элемент ИЛИ и дешифратор причем информационный вход регистра адреса повтора соединен с выходом регистра ад-. реса и первым входом первого бпока эпементов И, вход синхронизации - с вторым 1 выходом блока формирования установочных сигналов, выход регистра адреса повтора подключен к,первыу входу второго блока эпементов И, выход которого соединен с первым входом первого блока эпе.ментов ИЛИ, второй вход которого соединен с выходом первого бпока эпементов И, выход первого блока эпементов ИЛИ подкпючен к адресному входу бпока памяти, первый, второй, третий и четвер- д тый выходы которого соединены с соответствующими входами блока коммутации, пятый и шестой выходы - с первым и вто. рым входами дешифратора, стробируюший вход которого подкпючен к первому вы- й ходу управпяемого генератора импупьсов, первый и второй выходы дешифратора соединены с одноименными входами эпемента ИЛИ, выход которого соединен с пятым входом бпока коммутации, шестой и3 седьмой входы которого подкшочены соответственно к третьему и четвертому выходам дещифратора, выход бпока коммутации соединен с первым входом третьего блока элементов И, второй вход которого соединен с выходом второго бпокв эпементов ИЛИ, первый вход которого подключен к входу логических условий устройства, второй вход через эпемент НЕ- к третьему выходу дешифратора, второй. 4 выход которого соединен с вторым входом блока формирования установочных сигна,:лов, третий вход которого соединен с вы.ходом эпемента ИЛИ и вторым входом управляемого генератора импупьсов, третий выход бпока формирования установочных сигналов соединен с первым входом четвертого блока элементов И, четвертый выход - с нулевым входом триггера .и установочным входом наквппивающего сумматора, выход которого подключен к вто-рому входу четвертого блока эпементов И, выход которого соединен с единичным входом триггера, единичный выход которо 1 Ого соединен с четвертым входом бпокаформирования входных сигналов и вторымвходом второго бпока эпементов И, нупевой выход триггера соединен с вторымвходом первого блока элементов И и пятым входом блока формирования устано-.вочных сигналов,2, Устройство по и. 1, о т п и ч аю ш е е с я тем, что блок коммутациисодержит шифратор, выходы которогосоединены с первыми входами 5 бпоковэлементов И, выходы которых соединеныс входами соответствующих эпементовИЛИ, вторые входи б бпоков эпементовИ соединены с первыми и вторым входами блока, вход шифратора подкпючен квыходу (8+1)-го блока эпементов И,первый вход которого подкпючен к первому входу (5+2)-го блока элементов И и явпяется четвертым входом бпока коммутации, третий вход бпока коммутации подключен к первому входу (5+3)-го блока элементов И, второй вход которого соединен с выходом (5+1)-го эпементв ИЛИ, первый вход которого соединен с пятым входом бпока коммутации и через первый эпемент задержки с вторым .входом (5+2)-го бцока эпементов И., выход, которого подключен к первому входу блока б элементов ИЛИ, второй вход когорого подключен к выходу (5+3)-го бпо ка элементов И, третий вход - к выхо дам 5 эпементов ИЛИ, а выход бпока элементов ИЛИ явпяется выходом бпока коммутации, шестой вход бпока коммутации подкшочен к второму входу (5+1)-го элемента ИЛИ, третий вход которого через второй эпемент задержки соединен с вторым входом (5+1) го бпока эпементов И и является седьмым входом бпока коммутации.3. Устройство по и. 1, о т п и ч аю щ е е с я тем, что бпок формирования установочных сигнапов содержит три эпемента И и три эпемента задержки, причем первый вход бпока подключен к первому входу первого эпемента И, второй вход которого подкнючен к пятому входу блока и первому входу второго эпемента И, второй вход которого через первый эпемент задержки подкпючен квторому входу блока и первому входу третьего эпемента И, второй вход которого подкпючен к первому входу блока, выход третьего эпемента И через второй эпемент задержки подкпючен к четвертому входу блока, третий вход блока через третий элемент задержки подкпючен к третьему выходу бпока, выход первого11 958088 12элемента И подключен к первому выходу 1, Авторское свидетельство СССРблока, выход второго элемента И по- М 741267, кл, С 06 Г 9/22, 1980.ключен к второму выходу бпока. 2. Авторское свидетепьство СССРИсточники информации % 616629, кп. С 06 Г 9/22, 1978принятые во внимание при экспертизе 5 (прототип).955058 Логач Составите пь ова, Пчепинская Техред А, Ач. Корректор Е, Рош Подписноео комитета СССРи открытийаушская наб., д, 4/5 38/53 Тираж 731 ВНИИПИ Государственно по депам изобретений 113035, Москва, Ж, Р

СмотретьЗаявка

3231794, 18.11.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/9-955058-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Главный тормозной цилиндр