Мультимикропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

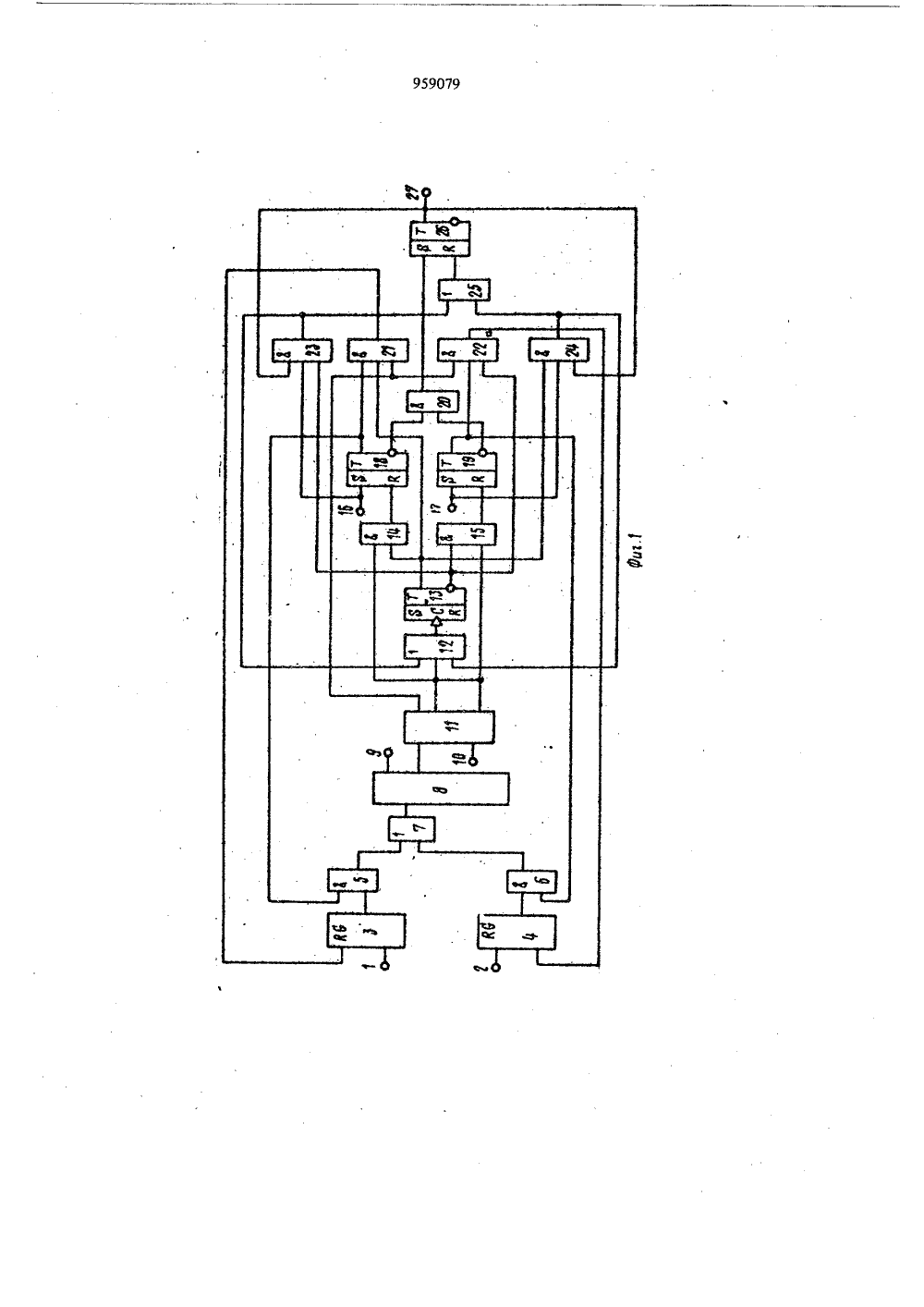

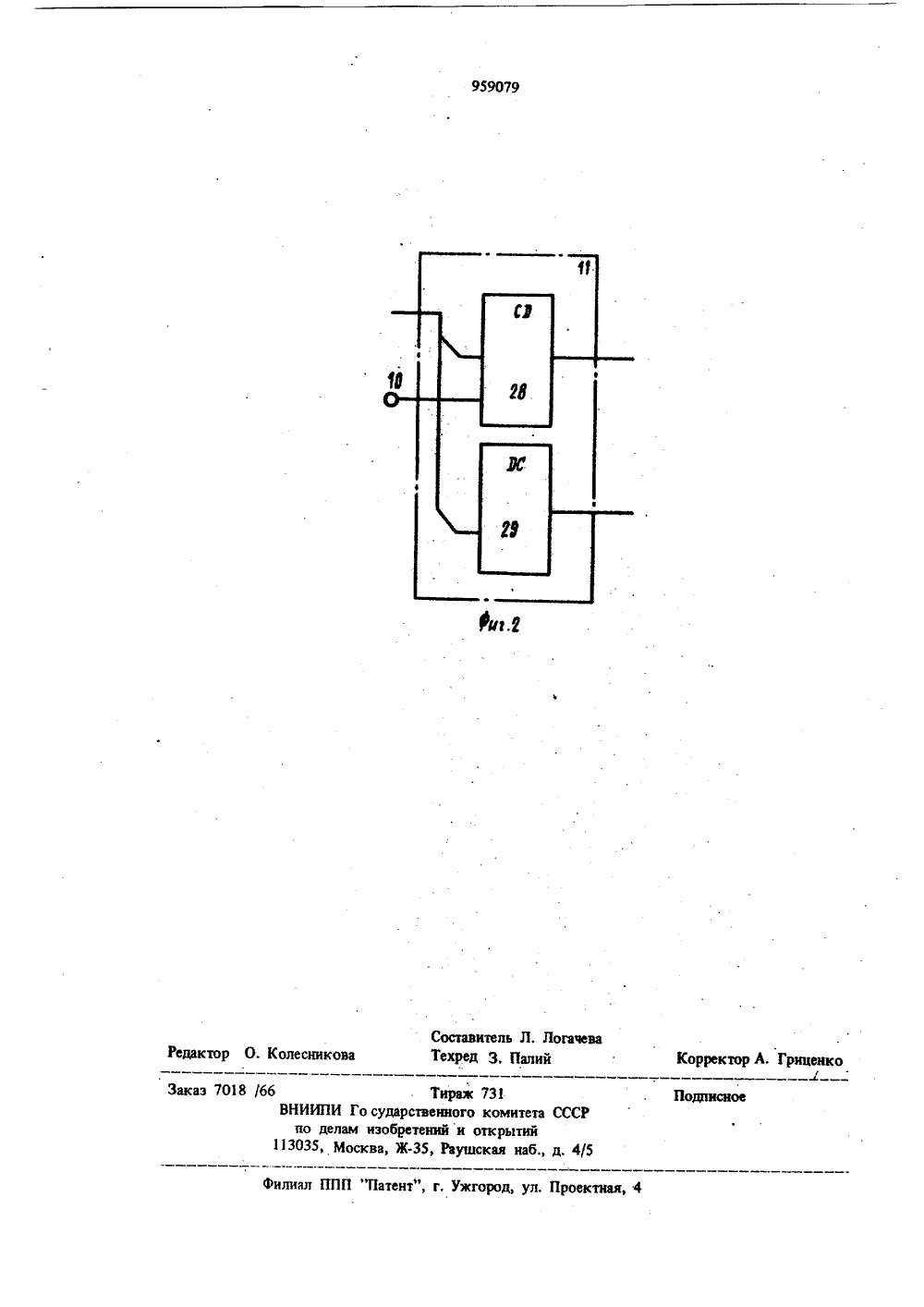

Союз Советских Социалистических нубии АВТОРСКОМ ИДЕТЕ ЛЬСТВУ) Дополнительное к авт, свид-ву2) Заявлено 26.01,81 (21) 3239213/18 - 2 присоединением заявки М 2 ударстеееые кеиитет СССР аелаи изобретений и етхрытек(23) П риоритет публиковано 15.09.82,тень М 34 681,325088,8) ата опубликования описания 2) Авторы изобретен Н. Ткаченко, В, С, Харченко, Г. Н. Тимонькин,А, П. Плахтеев, А, Д. Розанов и С, В, Чепель1;,Я) Заявител 54) МУЛЬТИМИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ перв И,Изобретение относится к вычислительной технике и может быть использовано при постро енин высокопроизводительных микропрограммных устройств.Известно микропрограммное устройство управления, содержащее блок памяти, блок проверки условий, триггер управления, элемент И и два регистра адреса 1.Недостатком данного устройства является низкая производительность, обусловленная недостаточно полным использованием возможнос. тей мультипрограммирования.Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является устройство управления с параллельным выполнением микропрограмм, Устройство содержит шесть элементов И, два элемента ИЛИ, первый триггер управления, два регистра адреса и блок памяти, первый выход которого соединен с первым выходом устройства, а второй - с первым входом блока проверки условий. второй вход которого подключен кпервому входу устройства, а выход - к вым входам дурного и второго элементо выходы которых подключены соответственнок первым входам первого и второго регистровадреса, входы которых соединены со вторым итретьим входами устройства соответственно, выход первого регистра адреса подключен к первому входу третьего элемента И, а второй входпервого элемента И соединен с етвтничйымвыходом первого триггера управления, единичныйвход которого подключен к четвертому входуустройства 121,Недостатком данного устройства являетсянизкая производительность.Цель изобретения - повышение производительности устройства,Поставленная цель достигается тем, чтов мультимикропрограммное устройство управления, содержацтее блок памяти, первый выход которого является информационным выходом устройства, второй выход соединен спервым информационным входом блока провер.ки условий, второй информайионный входкоторого подключен к входу логических условий устройства, информационный выход блокапроверки условий подключен в первым вхопэм3 95907первого и второго блоков элементов И, выхо- фды которых подключены соответственно к пер.вым информационным входам первого и второ.го регистров адреса, вторые информационныевходы которых соединены соответственно спервым и вторым информационным входамиустройства, выход первого регистра адреса соединен с первым входом третьего. блока эле.ментов И, второй вход которого соединен сединичньдк выходом первого триггера управле фиия, единичный вход которого подключен к иервому входу конца ожиданий устройства, два элемента И, два элемента ИЛИ, введены второй триггер управления, четвертый блок элементов И, триггер режима, триггер фиксации простоя, блок элементов ИЛИ, три элемента И, причем выход первого элемента ИЛИ подключен к нулевому входу триггера фиксации простоя, единичный выход которого подключен к управляющему выходу устройства и первым входам первого и второго элементов И, выходы которых подключены к первым и вторым входам первого и второго элементов ИЛИ, третий вход второго элемента ИЛИ соединен с управляющим выходом блока проверки условий и первыми входами третьего и четвертого элементов И, а выход подключен к счетному входу три 3 тера режима, единичный и нулевой выходы которого подключены соответственно к вторым входам третьего и четвертого элементов И и соответственно к вторым входам первого и вто рого блоков элементов И, а также к вторым входам второго и первого элементов И соответственно, выходы третьего и четвертого элементов И подключены к нулевым входам первого и второго триггеров управления соответ. З ственно, единичный .вход второго триггера управления подкаочеи к второму входу кон. ца ожиданий устройства и к третьему входу второго элементе И, третий вход первого эле. мента И подкаочен к первому входу конца ф ожиданий устройства, нулевые выходы первого и второго триггеров,управления соединены с первым и вторым входами пятого элемента И, выход которого подтсдючен кедащчному вхо- . ду триггера фиксации простоя, единичный выход 43 первого трипера управления подключен к третьему входу первого блока элементов И, единичный выход второго триттера управления соединен с третьим входом второго блока элементов И и с первым входом четвертого ЗО блока элементов И, второй вход которого сое. динен с выходом второго регистра адреса, второй информационный вход которого подключен к выходу второго блока элементов И, выходы третьего и четвертого блоков элементов И сое. чч динены с первым и вторым входами блока элементов ИЛИ, выход которого подключен к адресному входу блока памяти. 9 4На фиг. 1 приведена функциональная схемаустройства; на фиг, 2 - функциональная схемаблока проверки условий,Устройство содержит первый информационныйвход 1 устройства, второй информационныйвход 2 устройства, первый и второй регистры,3, 4 адреса,блоки 5, 6 элементов И, блок 7элементов ИЛИ, блок 8 памяти, информационный выход 9 устройства, вход 10 логическихусловий устройства, блок 11 проверки условий,элемент ИЛИ 12, триггер 13 режима, элементыИ 14, 15, входы 16, 17 конца ожиданий устройства, первый и второй триггеры 18, 19 уп- .равления, элемент И 20, блоки 21, 22 элементовИ, элементы И 23, 24, элемент ИЛИ 25, триггер26 фиксации простоя, управляющий выход 27устройства. Блок проверки условий содержитшифратор 28, дешифратор 29.Устройство работает в режиме мультиплексирования (разделения времени). двух микропрограмм. Адрес очередной микрокомандыпервой . (второй) параллельной микропрограммыв каждом рабочем такте записан в первомрегистре 3 адреса. Если в рассматриваемом рабочем такте функционирует первая (вторая)микропрограмма, то трипер 13 установлен внулевое (единичное) состояйие, триггер 18(19)в единичном состоянии, а триггер 19 (18) мо.жег быть как в единичном, если вторая (первая) параллельная микропрограмма не находитсяв режиме ожидания, так и в нулевом состоя.нии, если вторая (первая) параллельная микро.программа находится в режиме ожидания,В данном случае адрес очередной микроко.манды первой (второй) микропрограммы черезблок 21 (22) поступает в регистр З(4) и длее через блок 5 (6) и блок 7. в блок 8 памяти, с которого считывается очередная микро.команда и выполняется аналогично описанному.Если первая (вторая) микропрограмма, выполняющаяся в данном такте, должна перейтив режим ожидания, то в коде очередной микрокоманды содержится признак начала ожидания,который индентифицируется блоком 11 провер.ки условий и через элемент ИЛИ 12 устанавливает трипер 13 в нулевое (единичное) состояние, При этом открывается элемент И 15, выходным сигналом которого триттер 18(19)устанавливается в нулевое состояние и закрывает блок 5 (6) для передачи адреса очередноймикрокоманды на вход блока памяти 8,В этом случае, если трипер 19(18) нахо.дится в единичном состоянии, разрешается пе.редача с регистра 4(3) через блок 6(5) адресаочередной микрокоманды второй (первой)микропрограммы, которая функционируетаналогично первой(второй).Если же триггер 19(18) находится в нулевом состоявщ, вторая (первая) микропрограм5 ) 959079ма также в режиме ожидания, то срабатываетэлемент И 20,. который устанавливает тригГер2 б в единичное состояние. Триггер 26 выдает навыход 27 устройства признак обоюдного ожидания, по которому операционная система ЭВМпроизводит анализ ситуации на наличие тупика,В случае возникновения последнего реализуетсяпрограмма восстановления работоспособностисистемы, а в случае отсутствия устройство находится в режиме ожидания до окончания 1 Оожидания одной из мйкропрограмм,Если первой перешла в режнм ожиданияпервая (вторая) микропрограмма, то триггер13 находится в нулевом (единичном) состоянии,а триггеры 18 и 19 - в нулевом. Тогда по 1окончании ожидания первой (второй) микропрограмм по сигналу со входа 16(17) триггер18(19) переходит в единичное состояние и ини.циируется продолжение первой (второй) мик.ропрограммы, которая выполняется аналогично 20описанному,В случае же окончания ожидания не первой(второй), а второй (первой) микропрограммыпо сигналу со входа 17(16) триггер 19(18)устанавливается в единичное состояние и разрешает считывание адреса с регистра 4(3). Одновременно срабатывает элемент И 24(23), который устанавливает триггер 13 в нулевое (еди.нично состояние, который открывает блок22(21), разрешающий передачу адреса следую рщей микрокоманды в регистр 4(3), а такжечерез элемент ИЛИ 25 устанавливает трипер26 в нулевое состояние. Данное устройствореализует вторую (первую) параллельную мик.ропрограмму аналогично описанному,3Произвопительность устройства увеличиваетсяза счет оперативного обнаружения режима простоя устройства, причиной которого можетбыть тупиковая ситуация.Формула изобретенияМультимикропрограммное устройство управления, содержащее блок памяти, первый выходкоторого является информационным выходомустройства, второй выход соединен с первыминформационным входом блока проверки условий, второй информационный вход которогоподключен к входу логических условий устройства, информационный выход блока проверки условий подключен к первым входам пер.вого и второго блоков элементов И, выходы 6.которых подключены соответственно к первыминформационным входам первого и второгорегистров адреса, вторые информационные входы которых соединены соответственно с первыми вторым информационными входами устройст.ва, выход первого регистра адреса соединен с.первым входом третьего блока элементов И,второй вход которого соединен с единичным выходом первого триггера управления, единжный вход которого подключен к первому вхо.ду конца ожиданий улройства, два элементаИ, два элемента ИЛИ, о т л и ч а ю щ е ес я темчто, с целью повышения производительности устройства, оно дополнительно содержит четвертый блок элементов И, второй триггер управления, триттер режима, триггер фиксации простоя, блок элементов ИЛИ, три элемента И, причем выход первого элемента ИЛИподключен к нулевому входу триггера фиксации простоя, единичный выход которого подклю;чен к управляющему выходу устройства и пер. "вым входам первого и второго элементов И,выходы которых подключены к первым ивторым входам первого и второго элементовИЛИ, третий вход второгоэлемента ИЛИ сое.динен с управляющим выходом блока проверки условий и первыми входами третьего ичетвертого элементов И, а выход подключен ксчетному входу триггера режима, единичный инулевой выходы которого подключены соот.ветственно к вторым входам третьего и четвертого элементов И и соответственно к вторым входам первого и второго блоков элемен,тов И, а также к вторым входам второго и .первого элементов И, соответственно, выходытретьего и четвертого элементов И подключенык нулевым входам первого и второго тригге.ров управления соответственно, единичньщвход второго триггера управления подключенк второму входу конца ожиданий устройстваи к уретьему входу второго элемента И,третий вход первого элемента И подключенк первому входу конца ожиданий устройства,нулевые выходы первого и второго триггеровуправления соединены с первым и вторым входами пятого элемента И, выход которого под.ключен к единичному входу трипера фиксьции простоя, единичный выход первого триггера управления подключен к третьему входупервого блока элементов И, единичный выходвторого триггера управления соединен с третьимвходом второго блока элементов И и с первымвходом четвертого блока элементов И, второйвход которого соединен с выходом второгорегистра адреса, второй информационный входкоторого подключен.к выходу второго блока: блоков элементов И соешщеиы с первым и вто.рым входами блока элементов ИЛИ, выходкоторого подключен к адресному входу блокапамяти. Источники информации,принятые во внимание при экспертизе 1. Автоуское свидетельство СССР Иф 643874,кл, 6 06 Р 9/22, 1976. 2. Авторское свидетельство СССР по зйявке У 2881426, кл. 6 06 Р 9/22, 1979 (прототип).( едактор О, Колесникова Тираж твенного еиий и о Заказ 7018 /6 31комитета СС НИИПИ Го сударс по делам изобрет3035, Москва, Жткрытиикая наб д, 4 5, Раув илизл ППП "Патент", г, Ужгород, ул, Проектная, 4

СмотретьЗаявка

3239213, 26.01.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, РОЗАНОВ АНДРЕЙ ДМИТРИЕВИЧ, ЧЕПЕЛЬ СЕРГЕЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: мультимикропрограммное

Опубликовано: 15.09.1982

Код ссылки

<a href="https://patents.su/5-959079-multimikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Мультимикропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для герметизации секций конденсаторов