Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 959080

Авторы: Кондратьев, Тимонькин, Ткаченко, Харченко

Текст

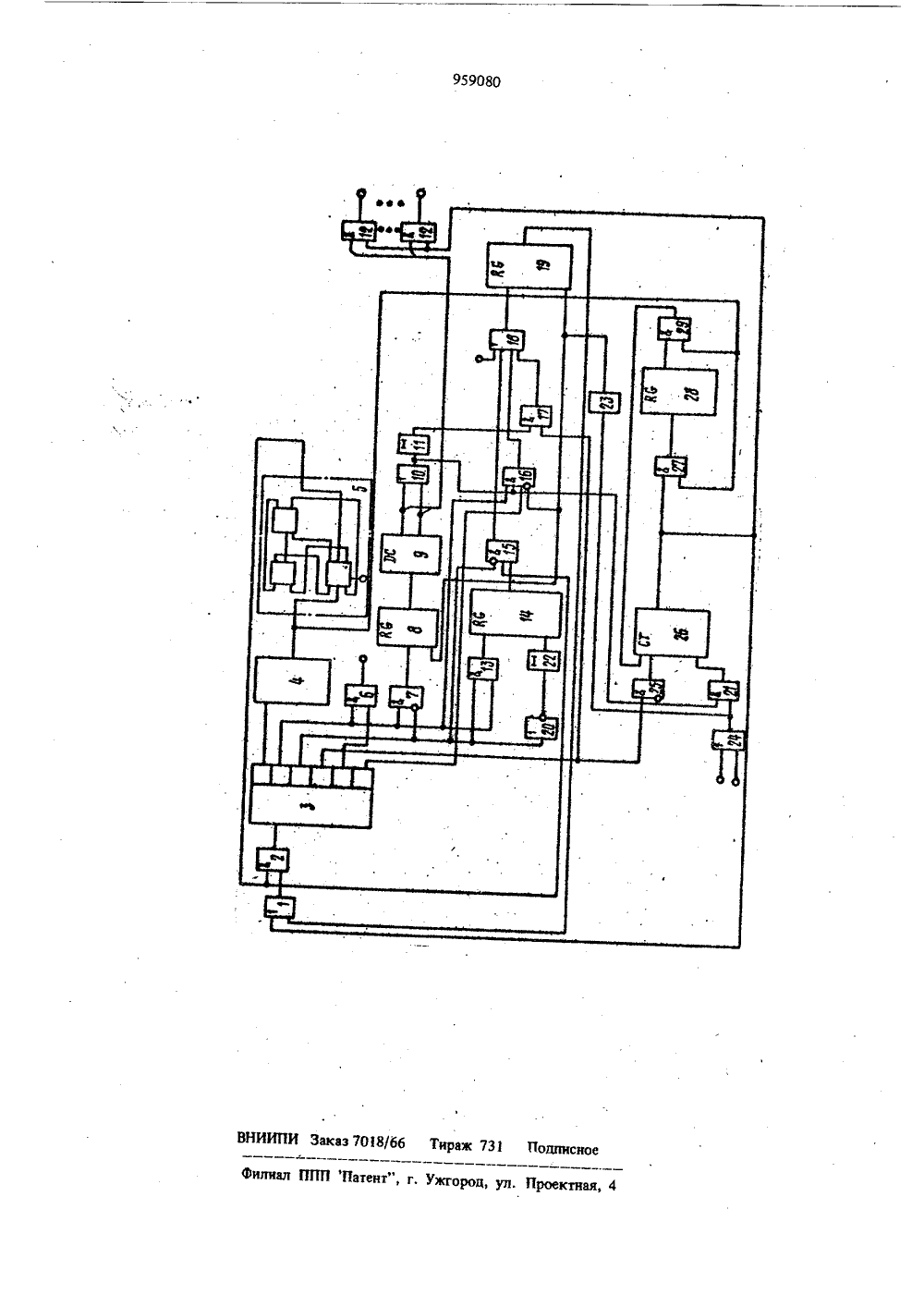

Союз СоветскихСоцкалксткческкхРеспублик АВТОРСКОМУ СВЫДЕТЕЛЬСТВУ 1) Дополнительное видКл,3(22) Заявлено 08.12,8 19 - 2 3 9/22 дииеикем заявки М уаарстааивй квинтет ИСР 23) Приоритет Опубликовано 15 09 82 Бюллетень ДК 681.3 алак изабретеии и открытий та опубликования описания 15,09.82 В. С. Харченко, Г. Н, Тимонькин, С. Н, Ткаченк и И, Е. Кондратьев(71) Заявитель ИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ БИС. 5Известно микропрограммное устройствоуправления, содержащее арифметический блок,блоки памяти адресов и микроопераций,счетчик команд, регистры, дешифратор, логи.ческие элементы И и ИЛИ 111,Недостатком указанного устройства являются низкие функциональные возможности, обус.ловленные тем, что структура устройства непозволяет увеличивать объем реализуемых программ путем введения дополнительных однотип 1ных устройств.Из известных микропрограммных устройствуправления наиболее близким по техническойсущности и достигаемому положительному ффекту является устройство, содержащее арифметический блок, выход которого соединен спервым входом первого блока элементов И,вьцдд которого соединен со входом блока Изобретение относится к области вычислительной техники н может быть использовано при построении микропрограммных устройств управления многопроцессорных вычислительных систем н ЦВМ, проектируемых на однотипных 4, памяти адресов, первый выход которого соединенсо входом блока памяти микроопераций, выход которого соединен со входом арифметического блока и первыми входами второго итретьего блока элементов И, выход второгоблока элементов И через регистр адреса возврата соединен со вторым входом третьегоблока элементов И, выход которого соединенс первым входом счетчика команд, выход кото;0рого соединен со вторым входом второго блока элементов И и первыми входами группыблоков элементов И,.выходы которой являются ; первыми выходами устройства, а вторые входысоединены с выходами,дешифратора, вход которого соединен с выходом регистра адреса переда.чи управления и со входом первого элементаИЛИ, выход которого соецинен с инверснымвходом четвертого блока элементов И, прямойвход которого соединен со вторым выходом , блока памяти адресов, а выход - со вторым .входом счетчика команд, трейщ вход которого . соединен с выходом пятого блока элементов И,первый вход которого соединен с выходом , первого элемента ИЛИ, а второй вход - с выо 4дешифратора соединен с выходом регистра адреса передачи управления, выходы дешифратора подключены к входам первого элементаИЛИ, выход которого соединен с инверснымвходом четвертого блока элементов И, прямойвход которого соединен со вторым выходомблока памяти адресов, а выход четвертого бло.ка элементов И подключен к второму инфор- .мационному входу счетчика команд, третийинформационный вход которого соединен с выходом пятого блока элементов И, первый входкоторого соединен с выходом первого элементаИЛф второй вход - с выходом первого блокаэлементов ИЛИ, входы которого подключенык первым адресным входам устройства, дополнительно введены второй и третий блоки эле.ментов ИЛИ, регистр автономных микропрог-рамм, буферный регистр, шесть блоков элементов И, второй элемент ИЛИ, два элемента задержки, элемент НЕ, причем выход второгоблока элементов ИЛИ соединен с вторым входом первого блока элементов И, первый входвторого блока элементов ИЛИ соединен с выходом счетчика команд, второй вход - с выходом регистра автономных микропрограмм,установочный вход которого соединен с уста.новочным входом регистра адреса передачиуправления, инверсным входом шестого блокаэлементов И и выходом второго элемента ИЛИ,вход которого соединен с выходом первогоблока элементов ИЛИ, выход шестого блокаэлементов И соединен с первым входом третье.го блокз элементов ИЛИ, второй вход которогоподключен к выходу седьмого блока элементов И, третий вход - к второму адресному вховходу устройства, четвертый вход - к выходувосьмого блока элементов И, выход третьегоблока элементов ИЛИ соединен с информационвым входом регистра автономных микропрогрзмм, третий выход блока пзмяти адресовсоединен с первыми входами девятого, десятого иодиннадцатого и вторым входом шестого блоковэлементов И, третий вход последнего соединенс выходом первого элемента ИЛИ, четвертыйвход шестого блока элементов И соединен счетвертым выходом блока памяти адресов, пятый выход которого соединен с инверснымвходом десятого блока элементов И, с первымвходом восьмого блока элементов И, с вторымвходом одиннадцатого блока элементов И ичерез последовательно соединенные элемент НЕи первый элемент задержки - с установочным входом буферного регистра, информационкьщ вход которого подключен к выходуодиннадцатого блока элементов И, выход буферного регистра соединен с вторым входомвосьмого блока элементов И, третий вход которого подключен к выходу арифметическогоблока, шестой выход блока памяти адресов 3 95908 ходом первого блока элементов ИЛИ, выходы которого являются первыми входами устройства 123.Недостатком данного устройства является низкое быстродействие. Многопроцессорная система, в которую вхоют устройство, состоит из однотипных микропрограммных устройств управления, что позволяет более гибко увеличивать вычислительные мощности системы. За счет подключения микропрограммных устройств управления 16 можно наращивать математическое обеспечение, т. е. увеличивать число хранимых микропрог. рамм и программ. Низкое быстродействие многопроцессорной системы обусловлено тем, что нерационально йсполвзуется каждое микропрограммное устройство управления. Структура микропрограммного устройства такова, что выполняются все микропрограммы, в том числе и автономные, Автономными будем называть такие микропрограммы, результаты которых не ззвисят от результатов решений выполнений друтих микропрограмм. После выполнения всех микропрограмм управление передается на аналогичное устройство, а данное микронрогрзммное устройство управления не функционирует. При реали.зацик программы работзет только одно устрой. ство, остзльные микропрограммные устройства управлейия простаивают. При выполнении микро. . прогрзмм в данном устройстве, другие микро программные устройства управления не реали. зуют автономные микропрограммы, и данное устройство не передает на другие микропрогрзм; мные устройства управления адреса автономных микропрограмм для их реализации. Этим обуславливается болыпое время простоя устройства и многопроцессорной системы в целом. ЗЗЦель изобретения . - повышение быстродей. ствия устройства.Поставленная цель достигаетс тем, что в микропрограммное устройство управления, содержащее арифметический блок, выход кото зф рого соединен с первым входом первого блокаэлементов И, выход которого соединен с адресным входом блока памяти адресов, первый выход которого соединен с адресным входом блока памяти микроопераций, выход которого. 4 соединен со входом арифметического блока и первыми входзми второго и третьего блоковэлементов И, выход второго блока элементовИ через регистр адреса возврата соединен совторым входом третьего блока элементов И, бевыход которого соединен с информационным входом счетчика команд, выход которого соединен со вторым входом второго блока элементов И и первыми входами блоков элемен-тов И группы, вторые входы которых подклю.чены к выходам дешифратора соответственно, выходы блоков элементов И группы являются информационными выходамк устройства, вход, 959080 Вподключен к второму входу девятого блока элементов И, выход которого является адресным выходом устройства, выход десятого блока элементов И соединен с информационным входом регистра адреса передачи управления, выход первого элемента ИЛИ через второй элемент задержки подключен к первому вхо ду седьмого элемента И, второй вход которого соединен с вторым выходом блока памяти адресов. 1 ОСущность изобретения состоит в повышении быстродействия и производительности за счет гибкого распределения выполнения автономных микропрограмм между микропрограммными устройствами управления путем выполнения ав. 1 З тономных микропрограмм при передаче управления на другие микропрограммные устройствауправления, а также использования результатов: выполнения автономных микропрограмм другими устройствами.20 На чертеже изображена функциональная схема микропрограммного устройства управления.Устройство содержит блок 1 элементов ИЛИ,блок 2 элементов И, блок 3 памяти адресов свыходами, блок 4 памяти микроопераций, арифметический блок 5, состоящий из преобразовате.ля кода, сумматора, блока регистров, блок 6элементов И, блок 7 элементов И; регистр 8адреса передачи управлениядешифратор 9, элемент ИЛИ 10, эдемент 11 задержки, группа12 блоков элементов И, блок 13 элементов И,буферный регистр 14, блок 15 элементов И,блок 1 б элементов И, блок 17 элементов И,блок 18 элементов ИЛИ, регистр 19 автономныхмикропрограмм, элемент НЕ 29, блок 21 . Зээлементов И, элемент 22 задержки, элементИЛИ 23, блок 24 элементов ИЛИ, блок 25элементов И, счетчик 26 команд, блок 27 эле., ментов И, регистр 28 адреса возврата, блок29 элементов И,Устройство работает в трех режимах:режиме выполнения микропрограммы Щ;режиме выполнения автономной микропрограммы (11); режиме передачи адреса автономноймикропрограммы на другое микропрограммное ффустройство управления (П 1) .Т режим, Счетчик 26 команд своим кодом .выбирает через блок Т элементов ИЛИ и блок2 элементов И определенные горизонтальныешины блокаЗ памяти адресов. Выбранная шина.30блока 3 памяти адресов выдает микрокоманду.Эта микрокоманда разбита на 6 частей; адресоперационной микрокоманды поступает в блок4 памяти микроопераций; адрес следующеймикрокоманды поступает на счетчик 26 команд Идля выбора следующей микрокоманды; код выбора поступает в регистр 8 адреса передачи управления; 4Метки последней микрокоманды перед переходом к,другому устройству управления, перехода к другому устройству управЛения, окончания автономной микропрограммы управляют работой во втором и третьем режимах. Опера. ционные микрокоманды поступают из блока 4 памяти микроопераций в арифметический блок 5.В арифметическом блоке обрабатываетсяи анализируется вся информация. Условия анализа передаются через блок 2 элементов И в блок 3 памяти адресов. По условию анализа осуществляется условный переход счетчика 26команд на новый адрес, В другом случае осу. ществляется безусловный переход по адресу. Условные переходы в микропрограммном устройстве управления осуществляются с помощью анализа информации, которая преобразуется в арифметическом блоке 5. Эти условия передают:- ся в блок 3 памяти адресов, из которого выбирается новый адрес в счетчике 26.команд через блок 25 элементов И, если код регистра 8 адре.са передачи управления содержит нули, Этот код воздействует на блок 25 элементов И через злемент ИЛИ 10, Безусловные переходы в уст.ройстве управления осуществляются аналогично за исключением того, что условия анализа не передаютсяв блок 3 памяти адресов и не влия.ют на выбор адреса. Для выхода на микропрограмму в микропрограммном устройстве, управления используется регистр 28 адреса возврата, в который записываются адреса со счетчика 26 команд через блок 27 элементов И и там хранятся, пока не будет выполнен возврат их микропрограмм, Этот адрес с вегистра 28 адреса возврата пересылается. через блок 29 элементов И в счетчик 26 команд для продолжения выполнения основнои микропрограммы, Если весь объем блока 3 памяти адресов по количеству микрокоманд задействован, а нужно расширить набор выполняемых программ или микропрог.рамм т, е, нарастить математическое обеспече.йие)то в блоке 3 памяти адресов в определенных шинах прошивается.код выбора микропрограммного устройства управления, который по. дается в регистр 8 адреса передачи управления. По этому коду осуществляется переход,к аналогичному устройству многопроцессорной сис. темы. Если содержимое. регистра 8 равно нулю, то продолжает работать данное устройство управ. ления в соответствии с описанным алгоритмом.При считывании из блока 3 памяти адресов микрокоманды, предшествующей последней, на третьем выходе блока 3 памяти адресов появляет. ся сигнал, который разрешает запись косвенного адреса автономной микропрограммы через блок 13 элементов И в,буферный регистр 14, При считывании последней ьаикрокоманды косвенный , адрес автономной микропрограммы переписыва-.микропрограммные устройства управления аналогичны предлагаемому устройству. Посредствомсвязей этих устройств через группу блоков 12элементов И и блок 24 элементов ИЛИ можноувеличивать количество и объем программ имикропрограмм. Формула изобретения Микропрограммное устройство управления, содержащее арифметический блок, выход кото. рого, соединен с первым входом первого блока элементов И, выход которого соединен с адресным входом блока памяти адресов первый выход которого соединен с адресным входом блока памяти микроопераций, выход которогосоединен с входом арифметического блока и первыми входами второго и третьего блоков элементов И выход второго блока элементов И через регистр адреса возврата соединен со вторым входом третьего блока элементовИ, выход которого соединен с первым информационным входом счетчика команд, выходкоторого соединен со вторым входом второгоблока элементов И и первыми входами блоковэлементов И группы, вторые входы которыхподключены к выходам дешифратора соответственно, выходы блоков элементов И группыявляются информационными выходами устройства, вход дешифратора соединен с выходомрегистра адреса передачи управле;ия, выходы дешифратора подключены к входам первогоэлемента ИЛИ, выход которого соединен с инверсным входом четвертого блока элементовИ, прямой вход которого соединен со вторым выходом блока памяти адресов, а выход четвертого блока элементов И подключен к вто рому информационному входу счетчика команд, третий информационный вход которого соединен с выходом пятого блока элементов И, первыйвход которого соединен с выходом первого элемента ИЛИ, второй вход - с выходом wервого блока элементов ИЛИ, входы которого подключены к первым адресным входам устройства, о т л, и ч а ю щ е е с я тем, что,с целью повышения быстродействия, устройство дополнительно содержит второй и третийблоки элементов ИЛИ, регистр автономныхмикропрограмм, буферный регистр, шесть блоков элементов И, второй элемент ИЛИ, два элемента задержки, элемент НЕ, причем выход второго блока элементов ИЛИ соединен с вторым входом первого блока элементов И, первый вход второго блока элементов ИЛИ соединен с выходом счетчика команд, второйвход - с выходом регистра автономных микропрограмм, установочный вход которого соединен с установочньгм входом регистра адреса 7 959080 8ется с буферного регистра 14 через блок 15элементов И и блок 18 элементов ИЛИ в ре.гистр 19 автономных, микропрограмм. Код выбора с четвертого выхода блока 3 памяти адресов через блок 7 элементов И записываетсяв Регистр 8 адреса передачи управления О, приэтом через элемент НЕ 20, элемент 22 задержкиустанавливается в нуль буферный регистр 14,Код выбора далее поступает в дешифратор 9,где преобразуется в сигнал выбора конкретного 16устройства управления. Сигнал с дешифратора 9поступает на соответствующий вход группы блоков 12 элементов И и через выбранный блокэлементов И адрес со счетчика 26 команд данногомикропрограммного устройства управления пере 1%дается в счетчик команд аналогичного устройствауправления. В дальнейшем работает выбранноеустройство управления, которое передаетна другие аналогичные микропрограммные устройствауправления или на данное устройство управлениямиадрес через блок 24 элементов ИЛИ и блок 21элементов И.Сигнал с выхода элемента ИЛИ 10 поступаетна блок 25 элементов И, запрещая установкусче 1 чика 26 команд в новое состояние и на щблок 21 элементов И, разрешая запись адресав счетчик 26 команд с любого другого устрой.ства управления через блок 24 элементов ИЛИ.При этом устройство переходит в режим выполнения автономных микропрограмм. ИП режим. Адрес автономнсй микропрограм.мы с регистра 19 автономных микропрограммпередается в блок З.памяти адресов и далеевыполняется как описано, но функций счетчика26 команд выполняет Регистр 19 автономныхмикропрограмм, блок 25 элементов И, блок 17элементов И. При поступлении последней микрокоманды автономной микропрограммы сигналс шестого выхода блока 3 памяти адресов раз-;решает запись адреса новой автономной микропрограммы через блок 16 элементов И и блок18 элементов ИЛИ в регистр 19 с, четвертоговыхода блока 3 памяти адресов, если нет сигнала на выходах блока 24 элементов ИЛИ.Если такой сигнал есть, то через элемент ИЛИ23поступает импульс, который устанавливаетРегистр;8 адреса передачи управления и регистр19 в нуль. При этом прекращается выполнениеавтономных микропрограмм и решаются основы микропрограммы,1 И режим, При передаче функций по реше-афнию автономных микропрограмм на другиемикропрограммные устройства управления сигнал на пятом выходе блока 3 памяти адресовразрешает передачу косвенного адреса автономной микропрограммы через блок 6 элементов И Иданного устройства управления, блок, 18 элементов ИЛИ в регистр автономных микропрограммдругого устройства управления. Подключенные10элемент НЕ и первый элемент задержки с установочным входом буферного регистра, информационный вход которого подключен к выходуодиннадцатого блока элементов И, выход буферного регистра соединен с вторым входом восьмого блока элементов И, третий вход которогоподключен к выходу арифметического блока,шестой выход блока памяти адресов подключенк второму входу девятого блока. элементов И,.выход которого является адресным выходомустройства, выход десятого блока элементов Исоединен с информационным входом регистраадреса передачи управления, выход первого эле "мента ИЛИ через второй элемент задержки подключен к первому входу седьмого блока элементов И, второй вход которого соединен свторым выходом блока памяти адресов.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР У 474806,кл. 6 06 Е 15/02, 1974.2, Авторское свидетельство СССР У 596947,кл, 6 08 Р 9/22, 1978 (прототип). 959080 передачи управления,инверсным входом шест- того блока элементов И и выходом второго элемента ИЛИ, вход которого соединен с выходом первого блока элементов ИЛИ, выход Ьестого блока элементов И соединен с первым входом третьего блока элементов ИЛИ, второй вход которого подключен к выходу седьмого блока элементов И, третий вход - к второму адресному входу устройства, четвертый вход - к выходу восьмого блока элементов И, выход 1 р третьего блока элементов ИЛИ соединен с информационным входом регистра автономных микропрограмм, третий выход блока памяти адресов соединен с первыми входами. девятого, десятого, одиннадцатого и вторым входом шес 1 а того блоков элементов И, третий вход послед- нега соединен с выходом первого элемента ИЛИ, четвертый вход шестого блока элементов И соединен с четвертым выходом блока памяти адресов, пятый выход которого соединен с нн- З версным входом десятого блока элементов И, с первым входом восьмого блока элементов И, с вторым входом одиннадцатого блока злемен. тов И и через последовательно соединенные

СмотретьЗаявка

3240695, 08.12.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КОНДРАТЬЕВ ИГОРЬ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.09.1982

Код ссылки

<a href="https://patents.su/6-959080-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Мультимикропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Состав контейнеров для трубопроводного пневмотранспорта грузов