Преобразователь двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

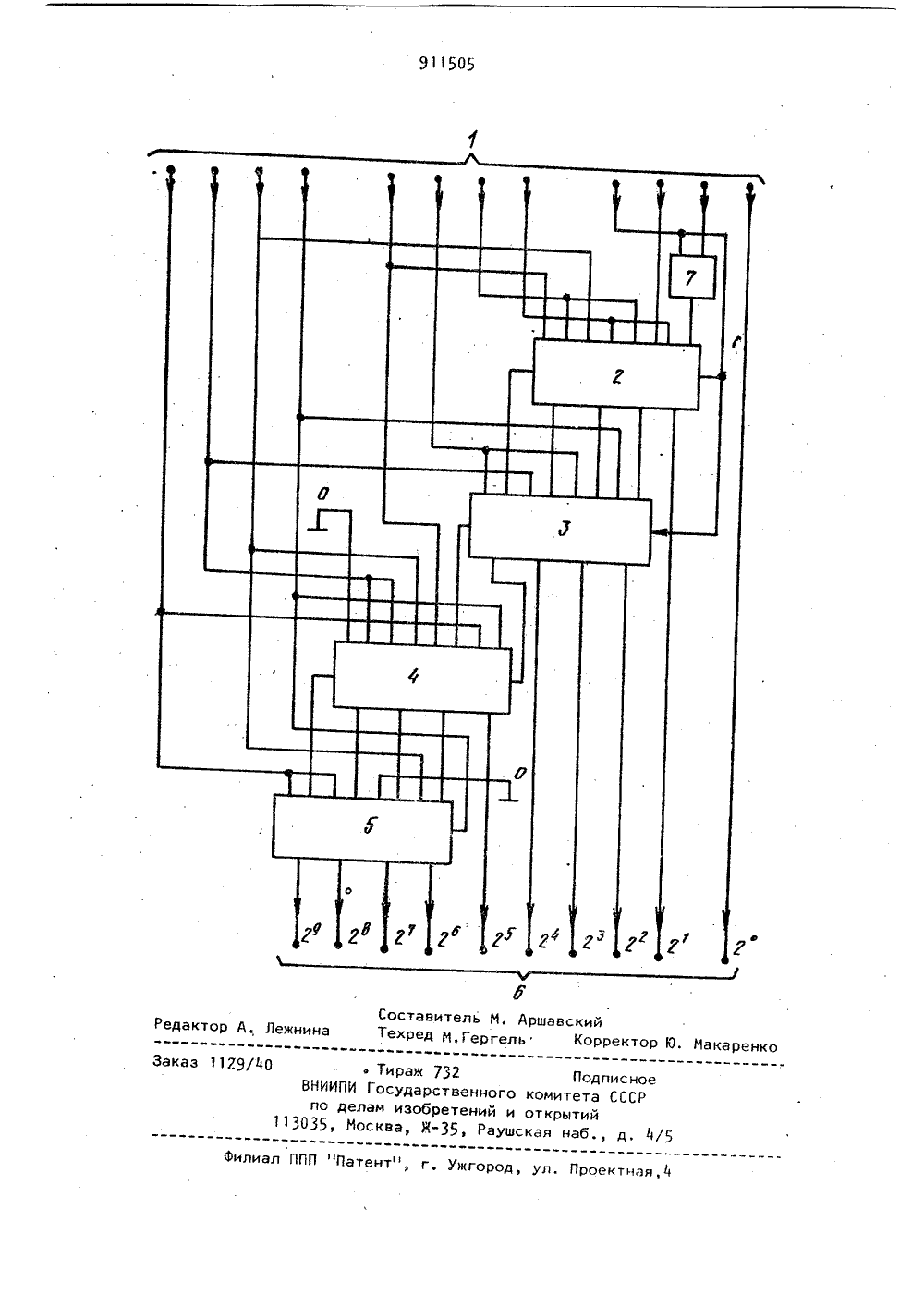

(51)М. Кл,с присоединением заявки М 6 06 Е 5/02 Рвудерстюый кемитет СССР аф юам эебратвиийетхвытй(23)приоритет Опубликовано 07.03,82. Бюллетень9. Дата опубликования описания 07.03.82ерИзобретение относится к автоматике и цифровой вычислительной техникеи может быть использовано при построении двоично-десятичных преобразова-,телей.Известен преобразователь двоичнодесятичноых чисел в двоичные, соджащий группу комбинационных суммаров, входы сумматора одного ярусасоединены с выходами сумматоров соседнего младшего яруса, входы сумматора первого яруса соединены с входами преобразователя, а выходы сумматора старшего яруса соединены с выходами преобразователяНедостаток этого преобразователясостоит в относительно большом количестве сумматоров, что увеличиваетсложность преобразователя и времяего работы,Наиболее близким к предлагаемомупо технической сущности являетсяпреобразователь двоично-десятичныхчисел в двоичные, содержащий сумматоры, выходы младших разрядов которых.соединены соответственно со вторым,третьим, шестым и седьмым разрядамигруппы выходов преобразователя, входмладшего разряда группы входов преобразователя соединен с первым разрядом группы выходов преобразователя,вход первого слагаемого второго разряда первого сумматора соединен свходом третьего разряда первой тетрады группы входов преобразователя,входы первого и второго разрядов второй тетрады группы входов преобразователя соответственно соединеныс входами первого слагаемого первого и третьего разрядов и вхо 1 амивторого слагаемого второго и четвер"того разрядов первого сумматора,вход третьего разряда второй тетрадыгруппы входов преобразователя соединен с входами первого слагаемого второго и четвертого разрядов второгосумматора, вход четвертого разрядавторой тетрады группы входов пре-.15054 Поставленная цель достигается тем, что в преобразователь двоично-десятичных чисел в двоичные, содержащий сумматоры, выходы младших разрядов которых соединены соответственно с вторым, третьим, шестым и седьмым разрядами группы выходов преобразователя, вход младшего разряда группы входов преобразователя соединен непосредственно с первым разрядом группы выходов преобразователя, вход первого слагаемого второго разряда первого сумматора соединен с входом третьего разряда первой тетрады группы входов преобразователя, входы первого и второго разрядов второй тетрады группы входов преобразователя соединены соответственно с входами первого слагаемого первого и третьего разрядов и входами второго слагаемого второго и четвертого разрядов первого сумматора, вход третьего разряда второй тетрады группы входов преобразователя соединен с входами первого слагаемого второго и четвертого разрядов второго суммато. ра, вход четвертого разряда второй тетрады группы входов преобразователя соединен с входом первого слагаемого четвертого разряда первого 4 о 45 50 55 3 91 обраэователя соединен со входом первого слагаемого четвертого разряда первого сумматора, входы третьего и четвертого разрядов третьей тетрады группы входов преобразователя соответственно соединены с входами первого слагаемоготретьего и четвертого разрядов третьего и четвертого сумматоров, выходы четвертого сумматора соединены со старшими разрядами группы выходов преобразователя, выходы старших разрядов и выход переноса первого и третьего сумматоров соединены с входами вторых слагаемых третьего и четвертого разрядов второго и четвертого сумматоров соответственно, вход третьего разряда третьей тетрады группы входов преобразователя соединен с входом первого слагаемого второго разряда второго сумматора 2.Недостаток данного преобразователя также состоит в большом количестве сумматоров и относительно невы" соком быстродействии.Цель изобретения - упрощение преобразователя, и повышение его быстродействия. 5 о 15 2 о и зо 35 сумматора, входы третьего и четвер,того разрядов третьей тетрады группы входов преобразователя соответственно соединены с входами первогослагаемого третьего и четвертого разрядов третьего и четвертого сумматоров,. выходы четвертого сумматорасоединены со старшими разрядами группы выходов преобразователя, выходыстарших разрядов и выход переносапервого и третьего сумматоров соединены с входами вторых слагаемыхтретьего и четвертого разрядов второго и четвертого сумматоров соответственно, вход третьего разрядатретьей тетрады группы входов преобразователя соединен с входом первого слагаемого второго разрядавторого сумматора, введен элемент ИЛИ, первый вход которогосоединен с входом четвертого разрядапервой тетрады группы входов преобразователя и с входами переноса первого и второго сумматоров, второйвход элемента ИЛИ соединен с входомвторого разряда первой тетрады группы входов преобразователя, а выходэлемента ИЛИ подключен к входу второго слагаемого первого разряда первого сумматора, вход второго разрядатретьей тетрады группы входов преобразователя соединен с входами второгослагаемого третьего разряда первогосумматора, третьего разряда третьегосумматора и входом первого слагаемого первого разряда четвертого сумматора, выходы второго и третьего разрядов второго сумматора соединеныс четвертым и пятым разрядами группывыходов преобразователя, выход четвертого разряда и выход переносавторого сумматора соединены с входомпереноса и входом первого слагаемоговторого разряда третьего сумматорасоответственно, вход четвертого разряда второй тетрады группы входовпреобразователя соединен с входомвторого слагаемого второго разрядатретьего сумматора, вход первого разряда третьей тетрады группы входовпреобразователя соединен с входамипервого слагаемого первых разрядоввторого и третьего сумматоров ивходом переноса четвертого сумматора, входы второго слагаемого четвертого разряда третьего сумматора и первого слагаемого второго разрядачетвертого сумматора соединены свходьи тождественного нуля.где- задержка распространения по цепи переноса; Сс - задержка распространения по цепи суммы. Для схемы прототипа эта величина равна сумме 1, = .31+ 4 ФС, 5 9115 ОНа чертеже приведена блок-схемапредлагаемого преобразователя.Преобразователь содержит тетрады Преобразователь двоично-десятичных1 группы входов преобразогателя, сум-. чисел в двоичные, содержащий сумматоматоры 2-5, выходы б преобразователяры, выходы младших разрядов которыхи элемент ИЛИ 7. соединены соответственно с вторым,Предлагаемый преобразователь осу- третьим, шес-ым.и седьмым разрядамиществляет параллельное преобраэова- группы выходов преобразователя, входние кода, поступающего на входные младшего разряда группы входов преобшины, и по принципу работы является О разователя соединен непосредственноустройсТвом комбинационного типа. с первым разрядом группы выходов преПоэтому при подаче на вход устройст- образователя, вход первого слагаемова двоично"десятичного кода числа го второго разряда первого сумматона его выходе немедленно вырабатыва- ра соединен с входом третьего разряется двоичный код этого числа, Время И да первой тетрады группы входов преэадержки установления выходного кода образоватепя, входы первого и второопределяется количеством операций го разрядов в,орой тетрады группы,суммирования, выполняемых при преоб- входов преобразователя соответственРазовании кодов. Для предлагаемого но соединены с входами первого слапреобразователя количество операций щ гаемого первого и третьего разрядовсуммирования по пятому, шестому и и входами второго слагаемого втоседьмому разрядам выходного кода рого и четвертого разрядов перуменьшено в два раза по сравнению вого сумматора, вход третьегос прототипом эа счет сокращения разряда второй тетрады группыобщего количества четырехразрядных 25 входов преобразователя соединенсумматоров. Это, в свою очередь, до- с входами первого слагаемого втостигнуто за счет введения. элемента рого и четвертого разрядов второИЛИ, представления четвертого раэря-. го сумматора, вход четвертого раэря"да кода младшей тетрады ввиде суммы да второй тетрады группы входов преоб.двоичных чисел - 2 ; 2. и 2 и ис- зв разователя соединен с входом первого1,пользования входов переноса суммато- ,слагаемого четвертого Разряда перворов. го сумматора, входы третьего и четвертого разрядов третьей тетрады груп.В результате например время - пы входов преобразователя соеответФдержки установления пятого разряд 3 ственно соединены с входами первоговыходного кода. й для.предлагаемо слагаемого третьего и четвертого раэустройства равно " . рядов третьего и четвертого суммау для.предлагаемого;торов, выходы четвертого сумматорасоединены с старшими Разрядами груп"пы выходов преобразователя, выходыИ+ Сстарших разрядов и выход переносапервого и третьего сумматоров соединены с входами вторых слагаемыхтретьего и четвертого разрядов вто 45рого и четвертого сумматсров соответ-,ственно, вход третьего разряда третьей тетрады группы входов преобразователя соединен с входом первогоЕсли заДержка по цепи пеРеноса слагаемого второго разряда второгоприблизительно равна задержке по цепи суммы, то предлагаемое устройство тем, что, с целью упрощения и повы 50имеет быстродействие в 1,4 раза выше, шения быстродействия,. в него введенчем у прототипа. элемент. ИЛИ, первый вход которогосоединен с входом четвертого разВ предлагаемом преобразователе ко- ряда первой тетрады группы входовличество сумматоров, необходимых дляпреобразователя и с входами переносаего реализации схемы, сокращаетая первого и второго сумматоров, второйна одну тРеть при одновременном повы- вход элемента ИЛИ соединен с входомшении быстродействия второго разряда первой тетрадыгруппы входов преобразователя, а выход элемента ИЛИ подключен к входу второго слагаемого первого разряда первого сумматора, вход второгоразряда третьей тетрады группы входов преобразователя соединен с. входами второго слагаемого третьегоразряда первого сумматора, третьегоразряда третьего сумматора и входомпервого слагаемого первого разрядачетвертого сумматора, выходы второго и третьего разрядов второго сумматора соединены с четвертым и пятым разрядами группы выходов преобразователя, выход четвертого разряда и выход переноса второго сумматора соединены с входом переносаи входом первого слагаемого второгоразряда. третьего сумматора соответственно, вход четвертого разряда 11505 8второй тетрады группы входов преобразователя соединен с входом второгослагаемого второго разряда третьегосумматора, вход первого разрядаЗ третьей тетрады группы входов преобразователя соединен с входами первого слагаемого первых разрядов второго и третьего сумматоров и входомпереноса четвертого сумматора, входы10 второго слагаемого четвертого разряда третьего сумматора и первогослагаемого второго разряда четвертого сумматора соединены с входом тождественного нуля.13 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 451981, кл. С 06 Е 5/02, 1974.2. йатент США Г 3705299,зо кл. 235"155, 972 (прототип).. Тираж 732 ВНИИПИ Государственного к по делам изобретений и о 13035, Москва, Н, РаущскПодписноитета СССР рыт я на Филиал ППП "Патент", г, Ужгород, ул. Проектная,4

СмотретьЗаявка

2728547, 23.02.1979

ПРЕДПРИЯТИЕ ПЯ А-3559

ГРИНБЕРГ БОРИС ИОСИФОВИЧ, ЖУРАВЛЕВ МАРК ИВАНОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичных, двоичные, чисел

Опубликовано: 07.03.1982

Код ссылки

<a href="https://patents.su/5-911505-preobrazovatel-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в двоичные</a>

Предыдущий патент: Устройство для отображения информации на экране электронно лучевой трубки

Следующий патент: Устройство для упорядочения данных

Случайный патент: Хирургический мостик для закрепления шва