Преобразователь последовательного биполярного кода в параллельный униполярный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 2001522

Автор: Чистов

Текст

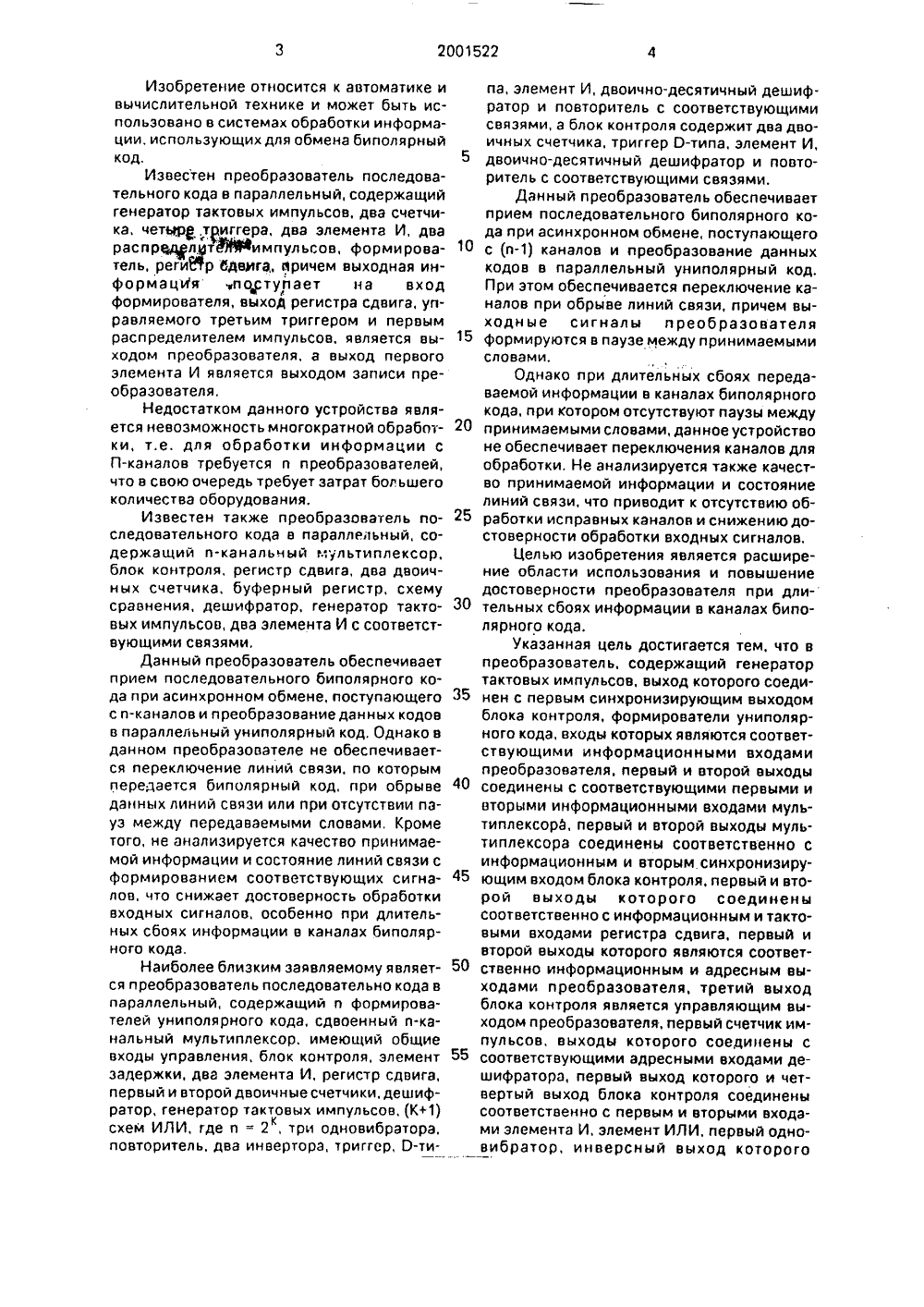

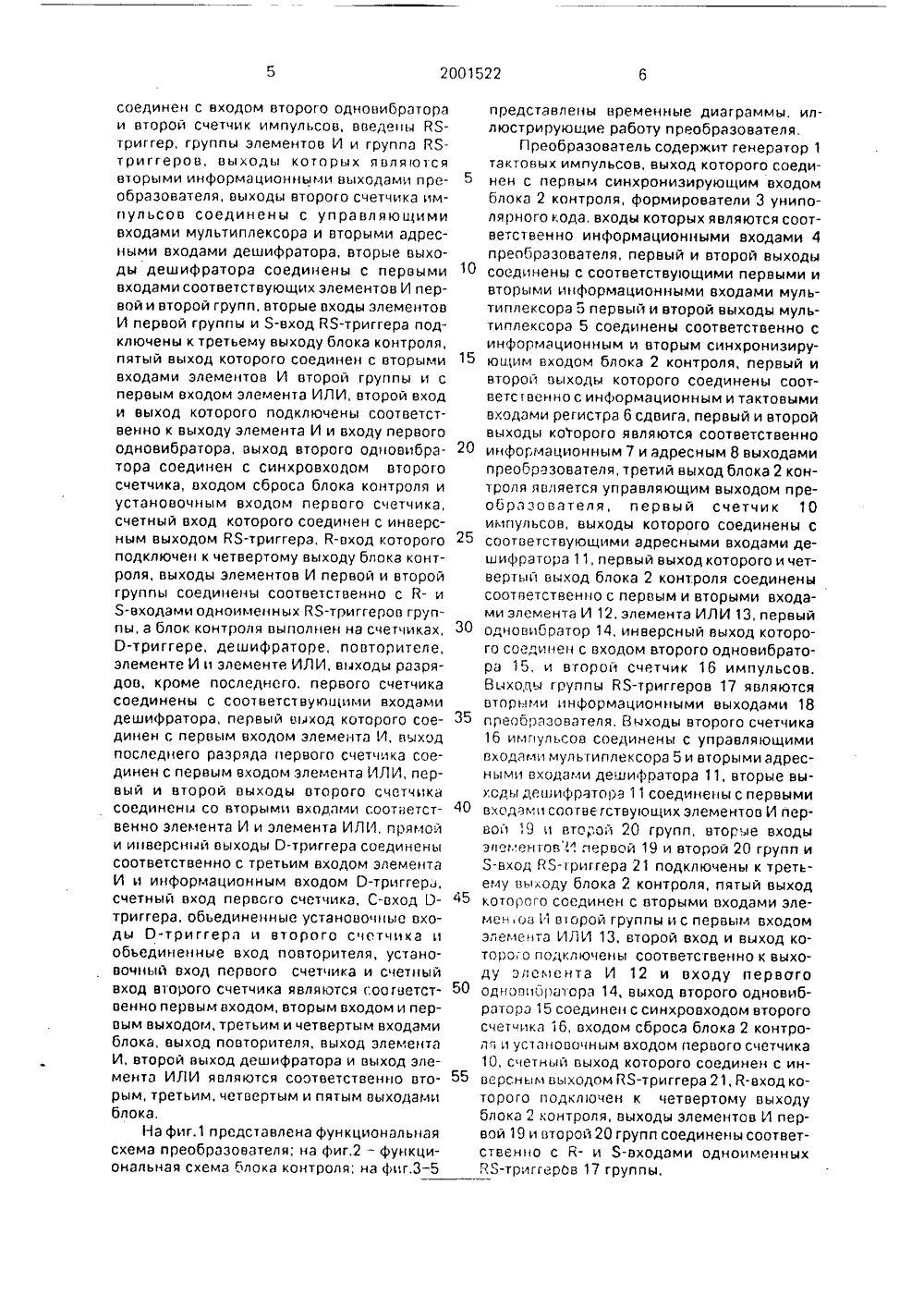

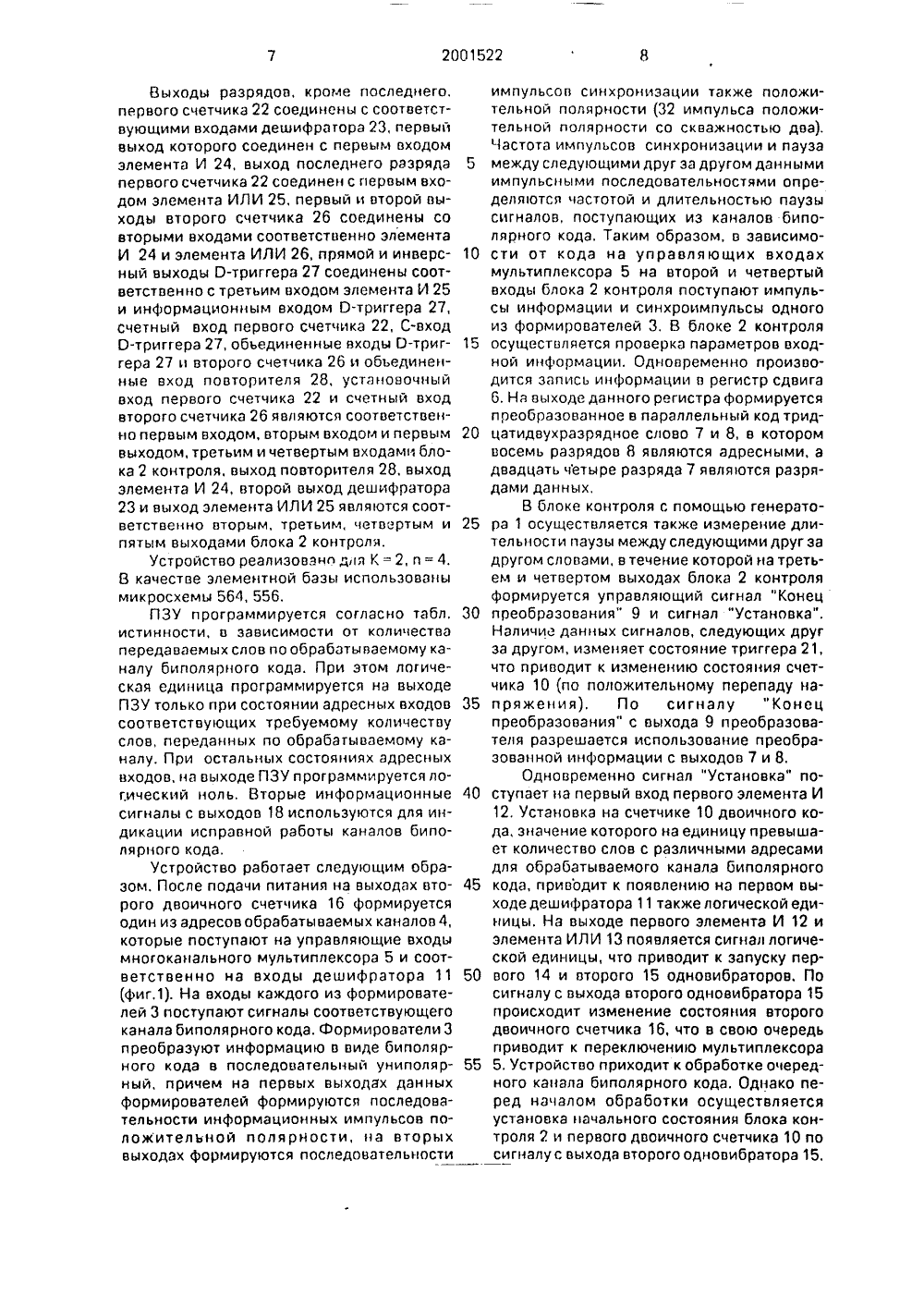

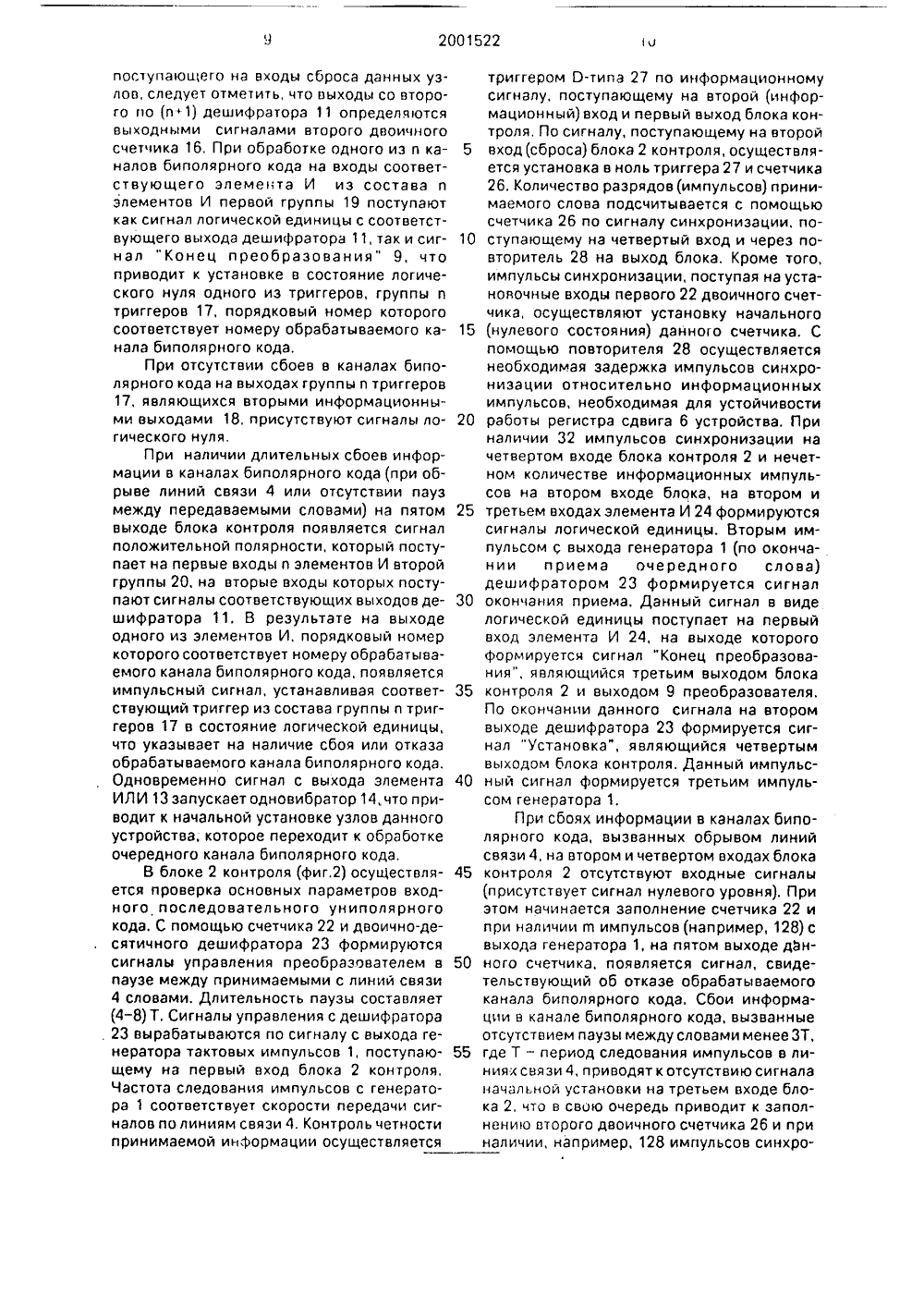

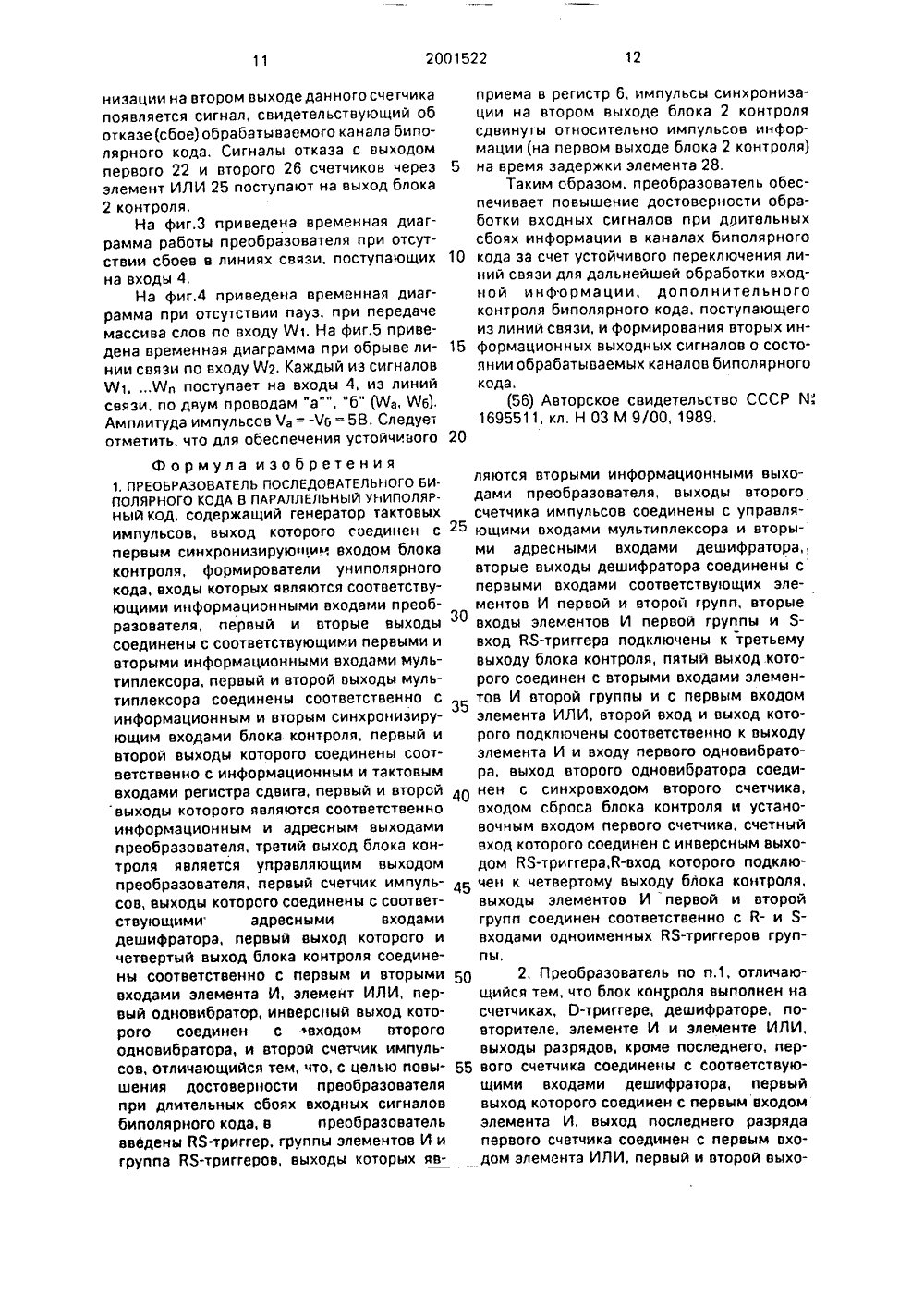

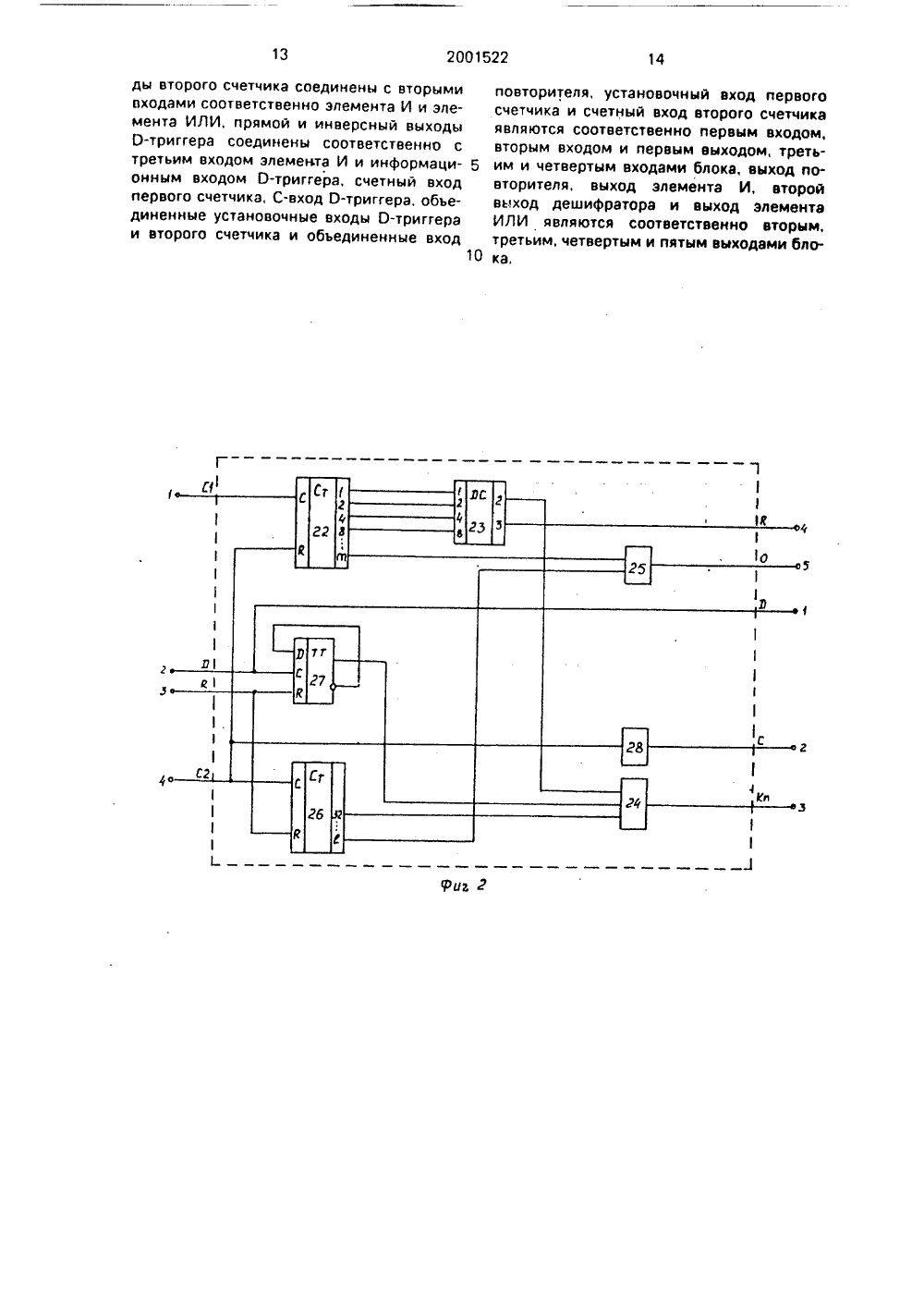

ОПИСАНИЕ ИЗОБРЕТЕНИ 1( ПАТЕНТУ Комитет Российской Федерации по патентам и топарным знакам(71) Московское приборостроительное конструкторское бюро "Восход"(73) Чистов Борис Алексеевич(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО БИПОЛЯРНОГО КОДА В ПАРАЛЛЕЛЬНЫй ЮНИПОЛЯ РНЫй КОД(57) Использование изобретение может быть использовано в системах обработки информации, использующих дпя обмена биполярный код Суцность: преобразование последовательного биполярного кода линий связи 4 в последовательныйуниполярный код осуществляется с помощью иформирователей 3 с выделением информационнойимпульсной последовательности и импульсов синхронизации, которые через мультиплексор 5 поступают в блок 2 контроля, где осуществляетсп контроль параметров обрабатываемого каналд и фор(и) ИЗ (и) 2001522 С 1(э 1) 5 НОЗМ 9 00 мируются сигналы управления преобразователем лри сбоях каналов биполярного кода В паузе между принимаемыми словами блок 2 контроля выдает упрдзчяющий сигнал "Конец преобразования" 9, рдзрешд ощий использование информации с выхо - да сдтгового регистрд б. С помощью первого счетчика 10, дешифратора 11, элемента И 12, триггера 21, элемента ИЛИ 13, а также первого 14, второго 15 адновибраторов и второго счетчика 16 осрцествляется подсчет количества принимаемых слов ло обрабатываемому каналу и формирование сигналов управления преобразователем При длительных сбоях информации в каналах 4 биполярного кода, формировании сигналов управления преобразователем осуществляется по сигналу с пятого выхода блока 2 контроля с помощью элемента ИЛИ 13, одновибраторов 14 и 15 и второго счетчика 16 С помощью элементов И второй группы 20 и группы и-триггеров 17 осуществляется формирование сигналов 18 отказа обрабатываемых каналов 4 биполярногоо кода. 1 з п ф-лы, 5 ипИзобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации. использующих для обмена биполярный код.Известен преобразователь последовательного кода в параллельный, содержащий генератор тактовых импульсов, два счетчика. четцре,триггера, два элемента И, два распрЮдулутВЙфимпульсов, формирователь, регистр бдвигааричем выходная информацИя,п(рту,пает на вход формирователя, выхоД регистра сдвига, управляемого третьим триггером и первым распределителем импульсов, является выходом преобразователя, а выход первого элемента И является выходом записи преобразователя.Недостатком данного устройства является невозможность многократной обработки, т.е. для обработки информации с П-каналов требуется п преобразователей, что в свою очередь требует затрат большего количества оборудования.Известен также преобразователь последовательного кода в параллельный, содержащий и-канальный мультиплексор, блок контроля, регистр сдвига, два двоичных счетчика, буферный регистр, схему сравнения, дешифратор, генератор тактовых импульсов, два элемента И с соответствующими связями,Данный преобразователь обеспечивает прием последовательного биполярного кода при асинхронном обмене, поступающего с и-каналов и преобразование данных кодов в параллельный униполярный код, Однако в данном преобразователе не обеспечивается переключение линий связи, по которым передается биполярный код, при обрыве данных линий связи или при отсутствии пауз между передаваемыми словами, Кроме того, не анализируется качество принимаемой информации и состояние линий связи с формированием соответствующих сигналов, что снижает достоверность обработки входных сигналов, особенно при длительных сбоях информации в каналах биполярного кода.Наиболее близким заявляемому является преобразователь последовательно кода в параллельный, содержащий и формирователей униполярного кода, сдвоенный и-канальный мультиплексор, имеющий общие входы управления, блок контроля, элемент задержки, два элемента И, регистр сдвига, первый и второй двоичные счетчики, дешифратор, генератор тактовых импульсов, (К+1) схем ИЛИ, где и = 2, три одновибратора,Кповторитель, два инвертора, триггер, О-типа, элемент И, двоично-десятичный дешифратор и повторитель с соответствующимисвязями, а блок контроля содержит два двоичных счетчика, триггер О-типа. элемент И,5 двоична-десятичный дешифратор и повторитель с соответствующими связями,Данный преобразователь обеспечиваетприем последовательного биполярного кода при асинхронном обмене, поступающего10 с (и) каналов и преобразование данныхкодов в параллельный униполярный код.При этом обеспечивается переключение каналов при обрыве линий связи, причем выходные сигналы преобразователя15 формируются в паузе между принимаемымисловами.Однако при длительных сбоях передаваемой информации в каналах биполярногокода, при котором отсутствуют паузы между20 принимаемыми словами, данное устройствоне обеспечивает переключения каналов дляобработки. Не анализируется также качество принимаемой информации и состояниелиний связи, что приводит к отсутствию об 25 работки исправных каналов и снижению достоверности обработки входных сигналов.Целью изобретения является расширение области использования и повышениедостоверности преобразователя при длиЗ 0 тельных сбоях информации в каналах биполярного кода,Указанная цель достигается тем, что впреобразователь, содержащий генератортактовых импульсов, выход которого соедиЗ 5 нен с первым синхронизирующим выходомблока контроля, формирователи униполярного кода, входы которых являются соответствующими информационными входамипреобразователя, первый и второй выходы40 соединены с соответствующими первыми ивторыми информационными входами мультиплексора, первый и второй выходы мультиплексора соединены соответственно синформационным и вторым. синхронизиру 45 ющим входом блока контроля, первый и второй выходы которого соединенысоответственно с информационным и тактовыми входами регистра сдвига, первый ивторой выходы которого являются соответ 50 ственно информационным и адресным выходами преобразователя, третий выходблока контроля является управляющим выходом преобразователя, первый счетчик импульсов, выходы которого соединены с55 соответствующими адресными входами дешифратора, первый выход которого и четвертый выход блока контроля соединенысоответственно с первым и вторыми входами элемента И, элемент ИЛИ, первый одновибратор, инверсный выход которогосоединен с входом второго одновибратора и второй счетчик импульсов, введены ВЗ- триггер, группы элементов И и группа ВЯ- триггеров, выходы которых являются вторыми информационными выходами преобразователя, выходы второго счетчика импульсов соединены с управляющими входами мультиплексора и вторыми адресными входами дешифратора, вторые выходы дешифратора соединены с первыми входами соответствующих элементов И первой и второй групп. вторые входы элементов И первой группы и Я-вход ВБ-триггера подключены к третьему выходу блока контроля, пятый выход которого соединен с вторыми входами элементов И второй группы и с первым входом элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу элемента И и входу первого одновибратора, выход второго одновибратора соединен с синхровходом второго счетчика, входом сброса блока контроля и установочным входом первого счетчика, счетный вход которого соединен с инверсным выходом ВЯ-триггера, В-вход которого подключен к четвертому выходу блока контроля, выходы элементов И первой и второй группы соединены соответственно с В- и Я-входами одноименных ВЗ-триггеров группы, а блок контроля выполнен на счетчиках, О-триггере, дешифраторе, повторителе, элементе И и элементе ИЛИ, выходы разрядов, кроме последнего, первого счетчика соединены с соответствующими входами дешифратора, первый выход которого соединен с первым входом элемента И, выход последнего разряда первого счетчика соединен с первым входом элемента ИЛИ, первый и второй выходы второго счетчика соединены со вторыми входами соответственно элемента И и элемента ИЛИ, прямой и инверсный выходы О-триггера соединены соответственно с третьим входом элемента И и информационным входом О-триггера, счетный вход первого счетчика, С-вход О- триггера. обьединенные установочные входы О-триггера и второго счетчика и объединенные вход повторителя, установочный вход первого счетчика и счетный вход второго счетчика являются соогветственно первым входом, вторым входом и первым выходом, третьим и четвертым входали блока, выход повторителя, выход элемента И, второй выход дешифратора и выход элемента ИЛИ являются соответственно вторым, третьим, четвертым и пятым выходами блока.На фиг,1 представлена функциональная схема преобразователя; на Фиг.2 - функциональная схема блока контроля; на Фиг,3-55 10 15 20 25 30 35 40 45 50 55 торого подключен к четвертол 1 у выходу блока 2 контроля, выходы элементов И первой 19 и второй 20 групп соединены соответственно с В- и 3-входами одноименных ВЯ-триггерОв 17 группы. представлены временные диаграммы, иллюстрирующие работу преобразователя.Преобразователь содержит генератор 1 тактовых импульсов, выход которого соединен с первым синхронизирующим входом блока 2 контроля, формирователи 3 униполярного кода, входы которых являются соответственно информационными входами 4 преобразователя, первый и второй выходы соединены с соответствующими первыми и вторыл 1 и информационными входами мультиплексора 5 первый и второй выходы мультиплексора 5 соединены соответственно с информационным и вторым синхронизирующим входом блока 2 контроля, первый и второй выходы которого соединены соответс твенно с информационным и тактовыми входами регистра 6 сдвига, первый и второй выходы когорого являются соответственно информационным 7 и адресным 8 выходами преобразователя, третий выход блока 2 контроля является управляющим выходом преобразователя, первый счетчик 1 О импульсов, выходы которого соединены с соответствующими адресными входами дешифратора 11, первый выход которого и четвертый выход блока 2 контроля соединены соответственно с первым и вторыми входами элемента И 12, элемента ИЛИ 13, первый одновибратор 14, инверсный выход которого соединен с входом второго одновибратора 15, и вгорой счетчик 16 импульсов, Выходы группы ВБ-триггеров 17 являются вторыми информационными выходами 18 преобразователя. Выходы второго счетчика 16 импульсов соединены с управляющими входами мулы гиплексора 5 и вторыми адресными входами дешифратора 11, вторые выходы дешифратора 11 соединены с первыми входами соотвегствующих элементов И первой 19 и второй 20 групп, вторые входы алел ентовР первой 19 и второй 20 групп и 5-вход В 5-григгера 21 подключены к третьему выходу блока 2 контроля, пятый выход которого соединен с вторыми входами элемен ов И второй группы и с первым входом элемента ИЛИ 13. второй вход и выход которо;о подключены соответсгвенно к выходу элемента И 12 и входу первого однози.1 ратора 14, выход второго одновибратора 15 соединен с синхровходом второго счетчика 16, входом сброса блока 2 контроля и установочныл 1 входом первого счетчика 10, счетный выход которого соединен с инверсным выходом ВЯ-триггера 21, В-вход ко 2001522Выходы разрядов, кроме последнего, первого счетчика 22 соединены с соответствующими входами дешифрагора 23, первый выход которого соединен с первым входом элемента И 24, выход последнего разряда первого счетчика 22 соединен с первым входом элемента ИЛИ 25, первый и второй выходы второго счетчика 26 соединены со вторыми входами соответственно элемента И 24 и элемента ИЛИ 26, прямой и инверсный выходы О-триггера 27 соединены соответственно с третьим входом элемента И 25 и информационным входом О-триггера 27, счетный вход первого счетчика 22, С-вход О-триггера 27, объединенные входы О-триггера 27 и второго счетчика 26 и объединенные вход повторителя 28, установочный вход первого счетчика 22 и счетный вход второго счетчика 26 являются соответственно первым входом, вторым входом и первым выходом, третьим и четвертым входами блока 2 контроля, выход повторителя 28. выход элемента И 24, второй выход дешифратора 23 и выход элемента ИЛИ 25 являются соответственно вторым, третьим, четвертым и пятым выходами блока 2 контроля.Устройство реализовано для К = 2, и = 4, В качестве элементной базы использованы микросхемы 564, 556,ПЗУ программируется согласно табл, истинности, в зависимости от количества передаваемых слов по обрабатываемому каналу биполярного кода. При этом логическая единица программируется на выходе ПЗУ только при состоянии адресных входов соответствующих требуемому количеству слов, переданных по обрабатываемому каналу. При остальных состояниях адресных входов, на выходе ПЗУ программируется логический ноль, Вторые информационные сигналы с выходов 18 используются для индикации исправной работы каналов биполярного кода,Устройство работает следующим образом. После подачи питания на выходах второго двоичного счетчика 16 формируется один из адресов обрабатываемых каналов 4, которые поступают на управляющие входы многоканального мультиплексора 5 и соответственно на входы дешифратора 11 (фиг,1). На входы каждого из формирователей 3 поступают сигналы соответствующего канала биполярного кода, Формирователи 3 преобразуют информацию в виде биполярного кода в последовательный униполярный, причем на первых выходах данных формирователей формируются последовательности информационных импульсов положительной полярности, на вторых выходах формируются последовательности 10 15 20 25 30 35 40 45 50 55 импульсов синхронизации также положительной полярности (32 импульса положительной полярности со скважностью два). Частота импульсов синхронизации и пауза между следующими друг за другом данными импульсными последовательностями определяются частотой и длительностью паузы сигналов, поступающих из каналов биполярного кода. Таким образом, в зависимости от кода на управляющих входах мультиплексора 5 на второй и четвертый входы блока 2 контроля поступают импульсы информации и синхроимпульсы одного из формирователей 3, В блоке 2 контроля осуществляется проверка параметров входной информации. Одновременно производится запись информации в регистр сдвига 6, На выходе данного регистра формируется преобразованное в параллельный код тридцатидвухразрядное слово 7 и 8, в котором восемь разрядов 8 являются адресными, а двадцать четыре разряда 7 являются разрядами данных,В блоке контроля с помощью генератора 1 осуществляется также измерение длительности паузы между следующими друг за другом словами, в течение которой на третьем и четвертом выходах блока 2 контроля формируется управляющий сигнал "Конец преобразования" 9 и сигнал "Установка". Наличие данных сигналов, следующих друг за другом, изменяет состояние триггера 21, что приводит к изменению состояния счетчика 10 (по положительному перепаду напряжения). По сигналу "Конец преобразования" с выхода 9 преобразователя разрешается использование преобразованной информации с выходов 7 и 8.Одновременно сигнал "Установка" поступает на первый вход первого элемента И 12. Установка на счетчике 10 двоичного кода, значение которого на единицу превышает количество слов с различными адресами для обрабатываемого канала биполярного кода, приводит к появлению на первом выходе дешифратора 11 также логической единицы. На выходе первого элемента И 12 и элемента ИЛИ 13 появляется сигнал логической единицы, что приводит к запуску первого 14 и второго 15 одновибраторов. По сигналу с выхода второго одновибратора 15 происходит изменение состояния второго двоичного счетчика 16, что в свою очередь приводит к переключению мультиплексора 5. Устройство приходит к обработке очередного канала биполярного кода. Однако перед началом обработки осуществляется установка начального состояния блока контроля 2 и первого двоичного счетчика 10 но сигналу с выхода второго одновибратора 15, 2001522поступающего на входы сброса данных узлов, следует отметить, что выходы со второго по (п+1) дешифратора 11 определяются выходными сигналами второго двоичного счетчика 16, При обработке одного из п каналов биполярного кода на входы соответствующего элемента И из состава и элементов И первой группы 19 поступают как сигнал логической единицы с соответствующего выхода дешифратора 11, так и сигнал "Конец преобразования" 9, что приводит к установке в состояние логического нуля одного из триггеров, группы и триггеров 17, порядковый номер которого соответствует номеру обрабатываемого канала биполярного кода.При отсутствии сбоев в каналах биполярного кода на выходах группы п триггеров 17, являющихся вторыми информационными выходами 18, присутствуют сигналы логического нуля,При наличии длительных сбоев информации в каналах биполярного кода (при обрыве линий связи 4 или отсутствии пауз между передаваемыми словами) на пятом выходе блока контроля появляется сигнал положительной полярности, который поступает на первые входы и элементов И второй группы 20, на вторые входы которых поступают сигналы соответствующих выходов дешифратора 11. В результате на выходе одного из элементов И, порядковый номер которого соответствует номеру обрабатываемого канала биполярного кода, появляется импульсный сигнал, устанавливая соответствующий триггер из состава группы и триггеров 17 в состояние логической единицы, что указывает на наличие сбоя или отказа обрабатываемого канала биполярного кода. Одновременно сигнал с выхода элемента ИЛИ 13 запускает одновибратор 14 что приводит к начальной установке узлов данного устройства, которое переходит к обработке очередного канала биполярного кода.В блоке 2 контроля (фиг,2) осуществляется проверка основных параметров входного последовательного униполярного кода. С помощью счетчика 22 и двоично-десятичного дешифратора 23 формируются сигналы управления преобразователем в паузе между принимаемыми с линий связи 4 словами. Длительность паузы составляет (4 - 8) Т, Сигналы управления с дешифратора 23 вырабатываются по сигналу с выхода генератора тактовых импульсов 1, поступающему на первый вход блока 2 контроля, Частота следования импульсов с генератора 1 соответствует скорости передачи сигналов по линиям связи 4. Контроль четности принимаемой информации осуществляется 5 10 15 20 25 30 35 40 45 50 55 триггером 0-типа 27 по информационному сигналу, поступающему на второй (информационный) вход и первый выход блока контроля, По сигналу, поступающему на второй вход(сброса) блока 2 контроля, осуществляется установка в ноль триггера 27 и счетчика 26. Количество разрядов (импульсов) принимаемого слова подсчитывается с помощью счетчика 26 по сигналу синхронизации, поступающему на четвертый вход и через повторитель 28 на выход блока. Кроме того, импульсы синхронизации, поступая на установочные входы первого 22 двоичного счетчика, осуществляют установку начального (нулевого состояния) данного счетчика. С помощью повторителя 28 осуществляется необходимая задержка импульсов синхронизации относительно информационных импульсов, необходимая для устойчивости работы регистра сдвига 6 устройства. При наличии 32 импульсов синхронизации на четвертом входе блока контроля 2 и нечетном количестве информационных импульсов на втором входе блока, на втором и третьем входах элемента И 24 формируются сигналы логической единицы. Вторым импульсом с выхода генератора 1 (по окончании приема очередного слова) дешифратором 23 формируется сигнал окончания приема, Данный сигнал в виде логической единицы поступает на первый вход элемента И 24, на выходе которого формируется сигнал "Конец преобразования", являющийся третьим выходом блока контроля 2 и выходом 9 преобразователя, По окончании данного сигнала на втором выходе дешифратора 23 формируется сигнал "Установка", являющийся четвертым выходом блока контроля. Данный импульсный сигнал формируется третьим импульсом генератора 1.При сбоях информации в каналах биполярного кода, вызванных обрывом линий связи 4, на втором и четвертом входах блока контроля 2 отсутствуют входные сигналы (присутствует сигнал нулевого уровня). При этом начинается заполнение счетчика 22 и при наличии т импульсов (например, 128) с выхода генератора 1, на пятом выходе данного счетчика, появляется сигнал, свидетельствующий об отказе обрабатываемого канала биполярного кода, Сбои информации в канале биполярного кода, вызванные отсутствием паузы между словами менее ЗТ, где Т - период следования импульсов в линиях связи 4, приводят к отсутствию сигнала начальной установки на третьем входе блока 2, что в свою очередь приводит к заполнению второго двоичного счетчика 26 и при наличии, например, 128 импульсов синхро12 2001522 5 10 15 20 низации на втором выходе данного счетчика появляется сигнал, свидетельствующий об отказе(сбое) обрабатываемого канала биполярного кода. Сигналы отказа с выходом первого 22 и второго 26 счетчиков через элемент ИЛИ 25 поступают на выход блока 2 контроля.На фиг.3 приведена временная диаграмма работы преобразователя при отсутствии сбоев в линиях связи, поступающих на входы 4,На фиг.4 приведена временная диаграмма при отсутствии пауз, при передаче массива слов пс входу Ю 1, На фиг.5 приведена временная диаграмма при обрыве линии связи по входу Я 2, Каждый из сигналов Я 1, Рlп поступает на входы 4, из линий связи, по двум проводам "а, "б" (Ма, Юб), Амплитуда импул ьсов Ча = -Чб - 5 В. Следует отметить, что для обеспечения устойчивого Формула изобретения 1. ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО БИПОЛЯРНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ УНИПОЛЯР- ный код, содержащий генератор тактовых импульсов, выход которого соединен с первым синхронизируюцим входом блока контроля, формирователи униполярного кода, входы которых являются соответствующими информационными входами преобразователя, первый и вторые выходы соединены с соответствующими первыми и вторыми информационными входами мультиплексора, первый и второй выходы мультиплексора соединены соответственно с информационным и вторым синхронизирующим входами блока контроля, первый и второй выходы которого соединены соответственно с информационным и тактовым входами регистра сдвига, первый и второй выходы которого являются соответственно информационным и адресным выходами преобразователя, третий выход блока контроля является управляющим выходом преобразователя, первый счетчик импульсов, выходы которого соединены с соответствующими: адресными входами дешифратора, первый выход которого и четвертый выход блока контроля соединены соответственно с первым и вторыми входами элемента И, элемент ИЛИ, первый одновибратор, инверсный выход которого соединен с входом второго одновибратора, и второй счетчик импульсов, отличающийся тем, что, с целью повышения достоверности преобразователя при длительных сбоях входных сигналов биполярного кода, в преобразователь ввЕдены ВЗ-триггер, группы элементов И и группа ВЯ-триггеров, выходы которых явприема в регистр 6. импульсы синхронизации на втором выходе блока 2 контроля сдвинуты относительно импульсов информации (на первом выходе блока 2 контроля) на время задержки элемента 28,Таким образом. преобразователь обеспечивает повышение достоверности обработки входных сигналов при длительных сбоях информации в каналах биполярного кода за счет устойчивого переключения линий связи для дальнейшей обработки входной информации, дополнительного контроля биполярного кода, поступающего из линий связи, и формирования вторых информационных выходных сигналов о состоянии обрабатываемых каналов биполярного кода.(56) Авторское свидетельство СССР й: 1695511, кл, Н 03 М 9/00, 1989. ляются вторыми информационными выходами преобразователя, выходы второго счетчика импульсов соединены с управля ющими входами мультиплексора и вторыми адресными входами дешифратора вторые выходы дешифратора соединены с первыми входами соответствующих элементов И первой и второй групп, вторые 30 входы элементов И первой группы и Явход ВЗ-триггера подключены к третьему выходу блока контроля, пятый выход которого соединен с вторыми входами элемен тов И второй группы и с первым входомэлемента ИЛИ, второй вход и выход которого подключены соответственно к выходу элемента И и входу первого одновибратора, выход второго одновибратора соеди нен с синхровходом второго счетчика,входом сброса блока контроля и установочным входом первого счетчика, счетный вход которого соединен с инверсным выходом ВЯ-триггера,В-вход которого подклю чен к четвертому выходу блока контроля,выходы элементов И первой и второй групп соединен соответственно с В- и Я- входами одноименных ВЗ-триггеров группы.50 2. Преобразователь по п.1, отличающийся тем, что блок конроля выполнен на счетчиках, О-триггере, дешифраторе, повторителе, элементе И и элементе ИЛИ, выходы разрядов, кроме последнего, пер вого счетчика соединены с соответствующими входами де шифратора, первый выход которого соединен с первым входом элемента И, выход последнего разряда первого счетчика соединен с первым входом элемента ИЛИ, первый и второй выходы второго счетчика соединены с вторыми входами соответственно элемента И и элемента ИЛИ. прямой и инверсный выходы О-триггера соединены соответственно с третьим входом элемента И и информаци онным входом О-триггера, счетный вход первого счетчика, С-вход О-триггера, объединенные установочные входы О-триггера и второго счетчика и объединенные вход10 повторителя, установочный вход первого счетчика и счетный вход второго счетчика являются соответственно первым входом, вторым входом и первым выходом, третьим и четвертым входами блока, выход повторителя, выход элемента И, второй выход дешифратора и выход элемента ИЛИ являются соответственно вторым, третьим, четвертым и пятым выходами блока,2001522 дактор Т,Никольская орректор М,д аказ 3 Тираж Подп НПО " Поиск" Роспатента113035, Москва, Ж, Раушская наб исное Производственно-издательский комбинат "Патент", г,Ужгород, ул,Гагарина. 101 оставиехред М Б.Чистовргентал

СмотретьЗаявка

4852756, 20.07.1990

Московское приборостроительное конструкторское бюро "Восход"

Чистов Борис Алексеевич

МПК / Метки

МПК: H03M 9/00

Метки: биполярного, код, кода, параллельный, последовательного, униполярный

Опубликовано: 15.10.1993

Код ссылки

<a href="https://patents.su/9-2001522-preobrazovatel-posledovatelnogo-bipolyarnogo-koda-v-parallelnyjj-unipolyarnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного биполярного кода в параллельный униполярный код</a>

Предыдущий патент: Преобразователь номера датчика в цифровой код

Следующий патент: Устройство для передачи и приема дискретной информации с коррекцией ошибок

Случайный патент: Способ контроля процесса прессования порошковых материалов