Линейно-круговой интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

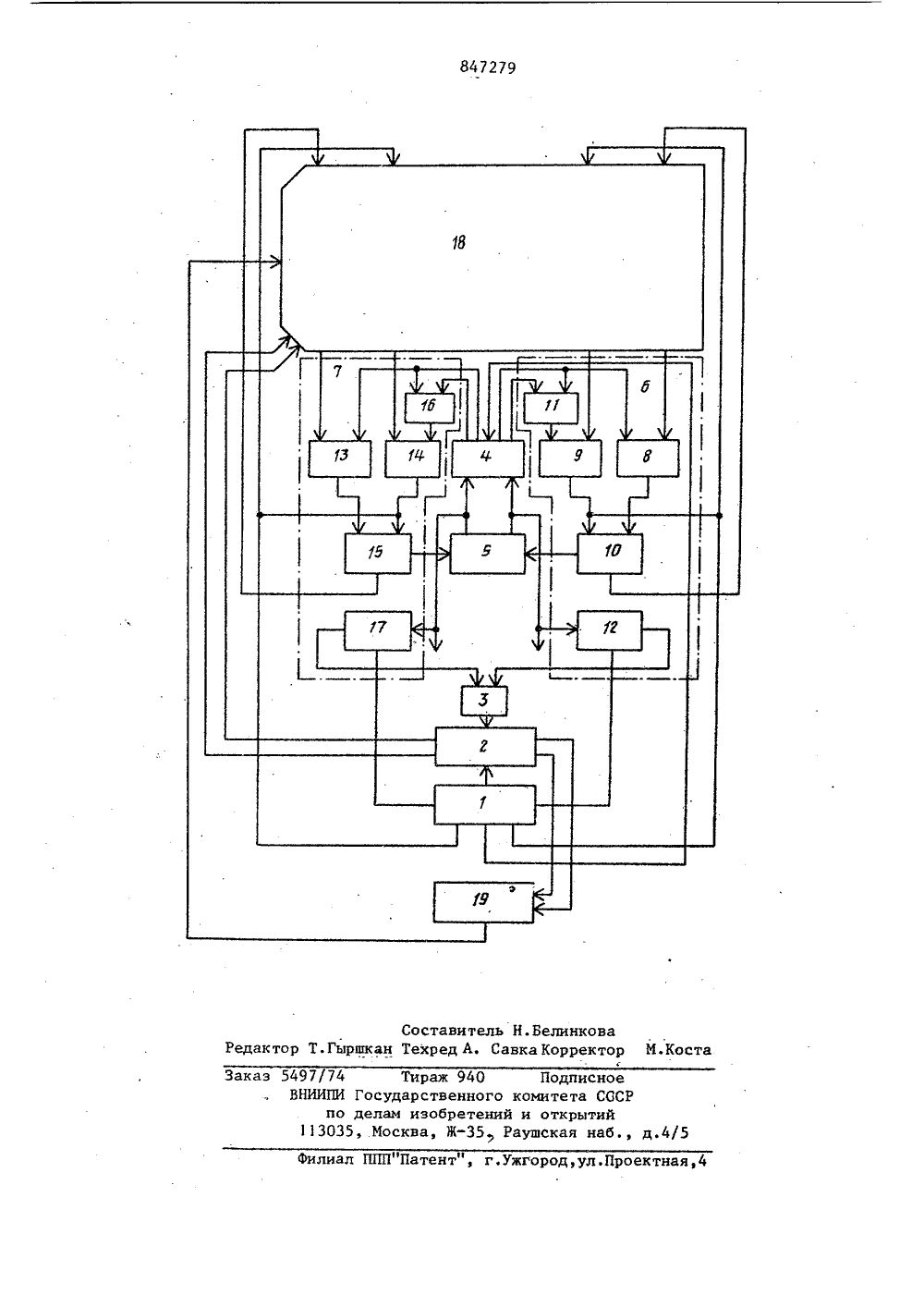

Союз СоветскихСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ в 847279(5)М. Кл. С 05 8 19/415 с присоединением заявки РЙ Государственный каиитет(23) Приоритет ссср по делам иэабретений и аткрытий(72) А вторы изобретения Ленинградский ордена Ленина электротехнический институт им, В.И,Ульянова (Ленина)(54) ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР Изобретение относится к автомати. ке и вычислительной технике и может быть использовано в системах программного управления станками.Известен линейно-круговой интерполятор, построенный на основе цифровых дифференциаль;ых анализаторов (ЦДА) параллельного действия, в котором для повышения точности интерполяции окружности за счет исключения10 погрешности интегрирования работа каждого из двух охваченных обратной связью интеграторов происходит последовательно 11.Недостатком этого устройстватэ является низкое быстродействиев два раза меньше, чем у интерполяторов с одновременно работающими интеграторами), а также сложность схем синхронизации.ИИзвестен также интерполятор с одновременно работающими интеграторами системы числового программного управления НЗЗ-М, содержащий блок задания программы, блок задания скорости, блок выделения приращений, коммутатор, два интегратора 1 21.Недостатками устройства являются болыпие затраты оборудования, низкая точность, сложность схем синхронизации.Наиболее близким по технической сущности к предлагаемому является линейно-круговой интерполятор, содержащий блок задания программы, блок задания скорости, элементы И, блок выделения приращений, коммутатор и два интегратора, каждый из которых содержит счетчик перемещения, первый и второй сдвиговые регистры, первый, второй и третий сумматоры, элемент ИЛИ причем первые входы всех сдвиговых регистров каждого интегратора соединены с вьпсодами блока задания скорости, вторые входыпервых сдвиговых регистров соединены с первыми выходами блока задания программы, их третьи входы соединены с выхо4729 Г 8дами первых сумматоров и первыми входами вторых сумматоров, выходы первыхсдвиговых регистров соединены с пер-,выми входами первых сумматоров, вто-рой выход блока задания прогоаммысоединен с первым входом коммутатора,третьи выходы блока задания программы соединены с первыми входами счетчиков перемещений, вторые входы которых соединены со вторыми входамикоммутатора, выходами блока выделения приращений и выходами линейнокругового интерполятора, выходысчетчиков перемещений соединены совходами элемента И, выход которогосвязан с первым входом блока заданияскорости, второй вход которого соединен с четвертым выходом блока задания программы, а первые выходывторых сумматоров соединены со входами блока вьделения приращений, вторыевыходы вторых сумматоров соединенысо вторыми входами вторых сдвиговыхрегистров, первые входы третьих сумматоров соединены с выходами вторыхсдвиговых регистров, вторые входытретьих сумматоров и первые входыэлементов ИЛИ соединены с первыми выходами коммутатора, вторые входы элементов ИЛИ соединены со вторыми выходами коммутатора, выходы элементовИЛИ соединены со вторыми входами первых сумматоров, а выходы третьих сумматоров - со вторыми входами вторыхсумматоров 1 31,Недостатком этого интерполятораявля отся большие затраты оборудованияи сложность схем синхронизации.Цель изобретения - сокращение обо,рудования и упрощение интерполятора.Указанная цель достигается тем,что линейно-круговой интерполятор,содержащий первый и второй вычислительные блоки, каждый из которых содержит первый, второй и третий сумматоры, элемент ИЛИ и счетчик перемещения, причем первый вход первогосумматора соединен с первым входомэлемента ИЛИ, выход которого соединенс первым входом второго сумматора,соединенного выходом с первым входомтретьего сумматора, второй вход которого подключен к выходу первогосумматора, первые выходы третьих сумматоров соединены соответственно спервым и вторым входами блока вьделения приращений, первые входы элементов ИЛИ подключены к первому и второ 10 15 20 25 30 35 40 ч 5 50 55 му выходам коммутатора, вторые входы элементов ИЛИ соединены соответственно с третьим и четвертым выходами коммутатора, первый и второй входы которого соединены соо гветственно с, первым и вторым выходом блока вьделения приращений и с первыми входами счетчиков перемещений, выходы которых соединены с первым и вторым входами элементов И, выход которого соединен с первым входом блока задания скорости, второй вход которого соединен с первым выходом блока задания программы, второй и третий выходы которого соединены со вторыми входами счетчи ков перемещений, а четвертый выход - с третьим входом коммутатора, содержит блок памяти и счетчик адреса, управляющий и установочный входы которого соединены с первым и вторым выходами блока задания. скорости соответственно, выходы счетчика адреса соединены с адресными входами блока памяти, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами блокр задания скорости, первый и третий разрядные входы блока памяти соединены со вторыми выходами соответствующих третьих сумматоров, второй и четвертый разрядные входы блока памяти соединены с выходами вторых сумматоров, а также с пятым и шестым выходами блока задания программы соответственно, первый и второй разрядные выходы блока памяти соединены со вторыми входами первых сумматоров, а третий и четвертый разрядные выходы - со вторыми входами вторых сумматоров.На чертеже представлена функциональная схема линейно-кругового интерполятораИнтерполятор содержит блок 1 задания программы, блок 2 задания скорости, элемент И 3, коммутатор 4, блок 5 выделения приращений, вычислительные блоки 5 и 7. Блок 6 содержит первый 8, второй 9 и третий 10 сумматоры, элемент ИЛИ 1, счетчик 12 перемещений, Блок 7 содержит первый 13, второй 14 и третий 15 сумматоры, элемент ИЛИ 16, счетчик 17 перемещений, Устройство содержит также блок 18 памяти и счетчик 19 адреса.Блок 18 памяти представляет собой оперативное запоминающее устройство, Сумматоры 8-10 и 13 - 15 представляют847279 5собой одноразрядные комбинационные сумматоры, счетчики 12,17 и 19- суммирующие счетчики, причем разрядность счетчиков 12 и 17 определяется максимальной разрядностью приращений координат и, а разрядность счетчика 19 - как 1 о 9 и, так как информация в блоке 18 располагается по принципу "разряд на ячейку", те. вертикальным образом. Так, например в пер вом информационном сечении (ИС) блока 18 происходит накопление подынтегральной функции, которая располагается во втором ИС (ИС 2). Совместно с блоком 6 ИС 1 и ИС 2 образуют первый 15 интегратор, а ИСЗ и ИС 4 совместно с обрабатывающим блоком 7 образуют второй интегратор. Элементы И 3, ИЛИ 11 и 16 представляют собой элементы,реали зующие логические функции И и ИЛИ 20 соответственно. Коммутатор 4 организован в виде шифратора, блок 5 осуществляет вьделение и хранение переноса со старшего значащего разряда информации, хранимой в ИС 1 и ИС 4, и включает необходимые комбинационные схемы и два триггера. Блок 2 задания скорости определяет работу устройства, управляет работой блока 18 памяти и счетчиком 19 и представляет со- Э 0 бой генератор тактовых сигналов, Блок 1 задания программы необходим для хранения программы, загрузки ИС блока 18 памяти и управления коммутатором. Он включает фотосчитывающее устройст во с необходимыми логическими схемами.Функционирование интерполятора распадается на две фазы. В фазе подготовки блок 2 по установочному входу обнуляет счетчик 19, что соответствует 40 установлению адреса нулевой ячейки. С выходов блока 1 в ИС 2 и ИСЗ записываются младшие разряды приращений координатх и Ь у при линейной интерполяции или координаты начальной точ- фб ки дуги хн, у при круговой, при этом подается сигнал "Запись" в блок 18 по выходу блока 2 задания скорости. Блок 2 увеличивает содержимое счетчика 19 на "1" и происходит запись сле- ф 0 дующих разрядов в ИС 2 и ИСЗ. После записи всех разрядов чисел в ИС 2 и ИСЗ с выходов блока 1 в счетчики 12 и 17 записываются приращение координат Ь х, ьу при линейной интерполяции 55 и хн,ун - при круговой, а счетчик 19 обнуляется, После интерполятор переходит в рабочую фазу, в которой осу 6ществляется либо линейная, либо круговая интерполяция.В режиме линейной интерполяции командой, поступившей из блока 1, коммутатор 4 блокируется, поэтому суп маторы 8 и 9, 13 и 14, а также элементы ИЛИ 11 и 16 на работу интерполн тора влияния не оказывают. Приращения ьх и у , хранимые в ИС 2 и ИСЗ после довательно суммируются с содержимым ИС 1 и ИС 4 соответственно, суммирование производится последовательно по разрядам на сумматорах 1 О и 15 при по даче сигнала "Чтение" с блока 2. После суммирования одноименных разрядов подается сигнал "запись"с блока 2, и в соответствующий разряд ИС 1 записывается сумма данных разрядов. Выделенные после сложения блоком 5 переносы поступают на выход интерполятора и на вычитающие входы счетчиков 12 и 17. При обнулении счетчиков 12 и 17 элемент И 3 вырабатывает сигнал,свидетельствующий об окончании отработки участка траектории. После этого устройство вновь переходит в фазу подготовки и процесс повторяется. В режиме круговой интерполяции в зависимости от команды, поступившей из блока 1 и определяющей четверть окружности и направление движения, устанавливается порядок работы интеграторов. Если подынтегральная функция интегратора, образованного обрабатывающим блоком 6 и ИС 1, ИС 2 увеличивается, то подынтегральная функция интегратора, образованного обрабатывающим блоком 7 и ИСЗ, ИС 4, уменьшается. В этом случае происходит суммирование ИС 1 и ИС 2, а также ИСЗ и ИС 4, как и при линейной интерполяции. Вьделенный перенос поступает с выхода блока 5 через коммутатор 4 на вход ИЛИ 1 и вход сумматора 8. Относительно начала сложения сигнал переноса эквивалентен коду 00001, который поступает на входы сумматоров 8 и 9 и обеспечивает эффект попеременной работы интеграторов, а также коррекцию подынтегральной функции в ИС 2 на сумматоре 9 на "+1", Перенос, возникающий с первого выхода блока 5, поступает через коммутатор 4 на вход элемента ИЛИ 16 и на вход сумматора 14 в виде 111, и обеспечивает коррекцию подынтегральной функции в ИСЗ на "-1" на сумматоре 14. Интерпо. ляция дуги, таким образом продол84727жается до тех пор, пока элементом И 3 не зафиксируется нулевое состояние счетчиков 12 и 17, что является сигналом для перехода интерполятора в фазу подготовки. При интерполяции участка траектории в обратном направлении аналогично работает сумматор 13 и элемент ИЛИ 16, а элемент ИЛИ 11 и сумматор 8 отключаютсяВведение блока памяти и счетчика 10 адреса позволяет исключение регистров,упрощает синхронизирующие цепи и удешевляет устройство, которое становится пригодным. для реализации в виде большой интегральной схемы. 5Формула изобретенияЛинейно-круговой интерполятор, 20 содержащий первый и второй вычислительные блоки, каждый из которых содержит первый, второй и третийсумматоры, элемент ИЛИ и счетчикперемещения, причем первый вход пер вого сумматора соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом второго сумматора, соединенного выходом с первым входом третьего сумматора, второй 30 вход которого подключен к выходу первого сумматора, первые выхоры третьих сумматоров соединены соответственно с первым и вторым входами блока выделения приращений, первые входы эле- З 5 ментов ИЛИ подключены к первому и второму выходам коммутатора, вторые .входы элементов ИЛИ соединены соответственно с третьим и четвевтым выходами коммутатора, первый и второй 40 входы которого соединены соответственно с первым и вторым выходом блока выделения приращений и с первымивходами счетчиков перемещений, выходы которых соединены с первым и 45 9 8вторым входами элемента И, выходкоторого соединен с первым входомблока задания скорости, второй входкоторого соединен с первым выходомблока задания программы, второй итретий выходы которого соединены совторыми входами счетчиков перемещений,а четвертый выход - с третьим входомкоммутатора, о т л и ч а ю щ и й с ятем, что, с целью упрощения интерполятора, он содержит блок памяти исчетчик адреса, управляющий и установочный входы которого соединеныс первым и вторым выходами блока задания скорости соответственно, выходысчетчика адреса соединены с адресными входами блока памяти, первый ивторой управляющие входы которогосоединены соответственно с третьим ичетвертым выходами блока задания скорости, первый и третий разрядныевходы блока памяти соединены со вторыми выходами соответствующих третьихсумматоров, второй и четвертый разрядные входы блока памяти соединеныс выходами вторых сумматоров, а также с пятым и шестым выходами блоказадания программы соответственно,первый и второй разрядные выходы блока памяти соединены со вторыми входами первых сумматоров, а третий и четвертый разрядные выходы - со вторымивходами вторых сумматоров.Источники информации,принятые во внимание при экспертизе1.Воронов А,А. и др, Цифровыеаналоги для систем автоматическогоуправления. М.-Л АН СССР, 1960,с, 114-121,2.Техническое описание системыпрограммного управления Н 33-1 М,Г 63.035117 ТО, Л., 1975, с.45,3. Авторское свидетельство СССРпо заявке У 2574790/18-24,кл. 6 05 В 19/18, 1978(прототип).847279 Составитель Н.Быршкан Техред А. Савка икова Кос то ект Филиал ППП"Патент", г,ужгород,ул.Проектная,4 Заказ 5497/74 Тираж ВНИИПИ Государст по делам изо 113035,.Москва, 940 Подписноенного комитета СССРетений и открытий

СмотретьЗаявка

2795102, 26.06.1979

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРО-ТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. B. И. УЛЬЯНОВА

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, ИОФФЕ ВЛАДИМИР ФЕДОРОВИЧ, КУЗЬМИН ГЕННАДИЙ ЯКОВЛЕВИЧ, КУПРИЯНОВ МИХАИЛ СТЕПАНОВИЧ, ШАВЫРИН ВАДИМ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G05B 19/4103

Метки: интерполятор, линейно-круговой

Опубликовано: 15.07.1981

Код ссылки

<a href="https://patents.su/5-847279-linejjno-krugovojj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Линейно-круговой интерполятор</a>

Предыдущий патент: Устройство управления позиционнымприводом

Следующий патент: Устройство для контроля радиоэлектрон-ных обектов

Случайный патент: Интегральный полупроводниковый детектор ионизирующих излучений и способ его получения