Устройство для моделирования петли гистерезиса

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

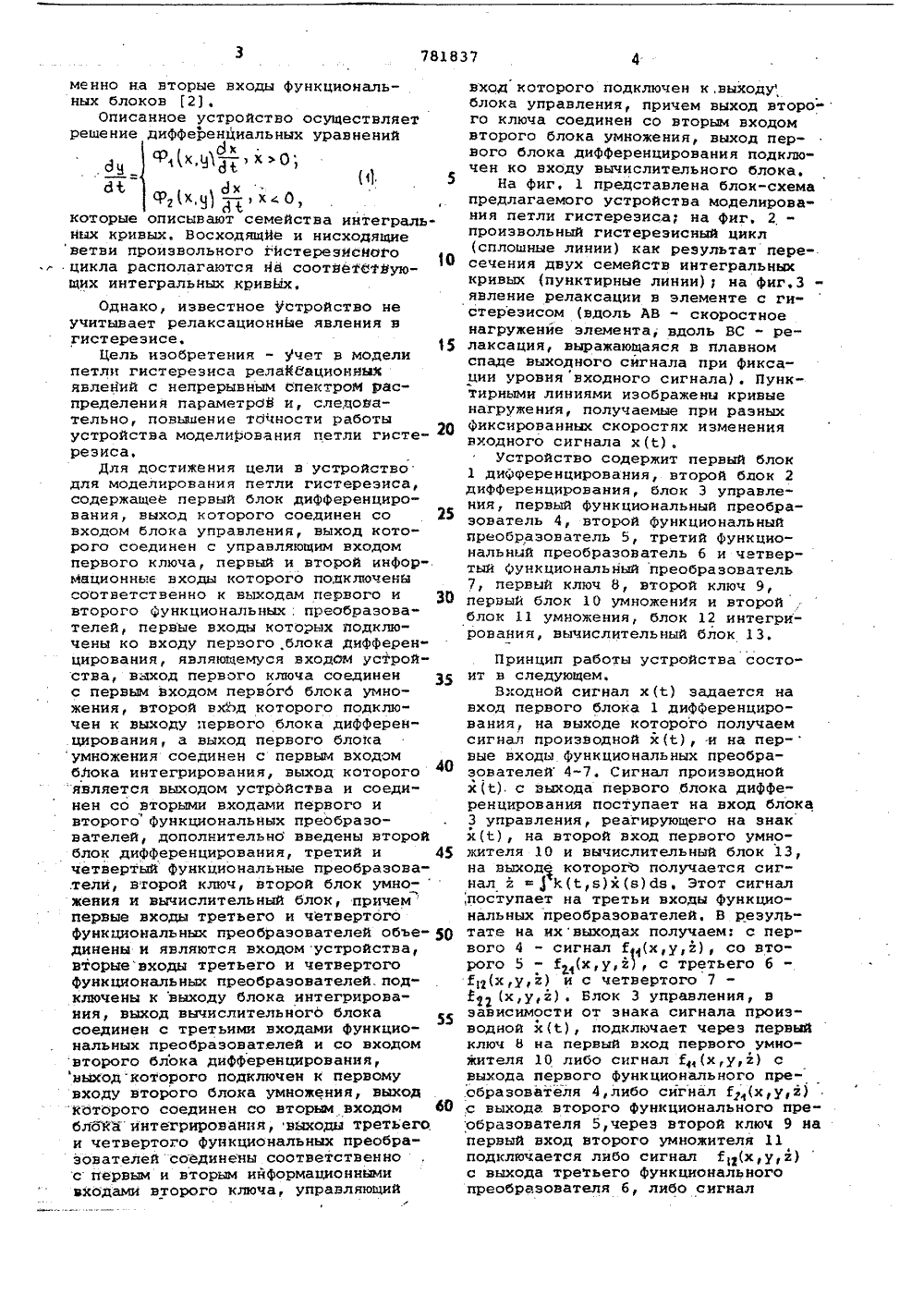

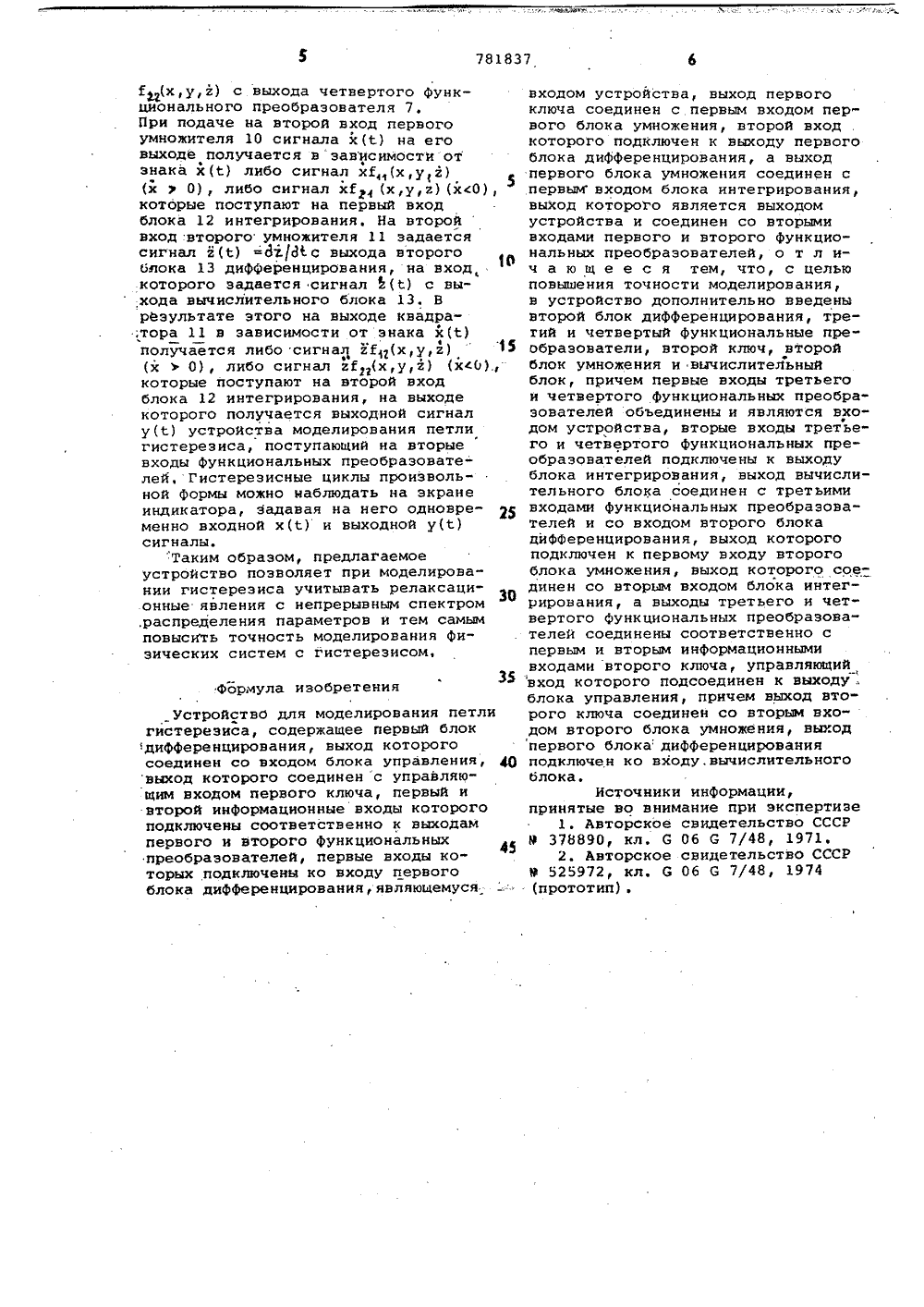

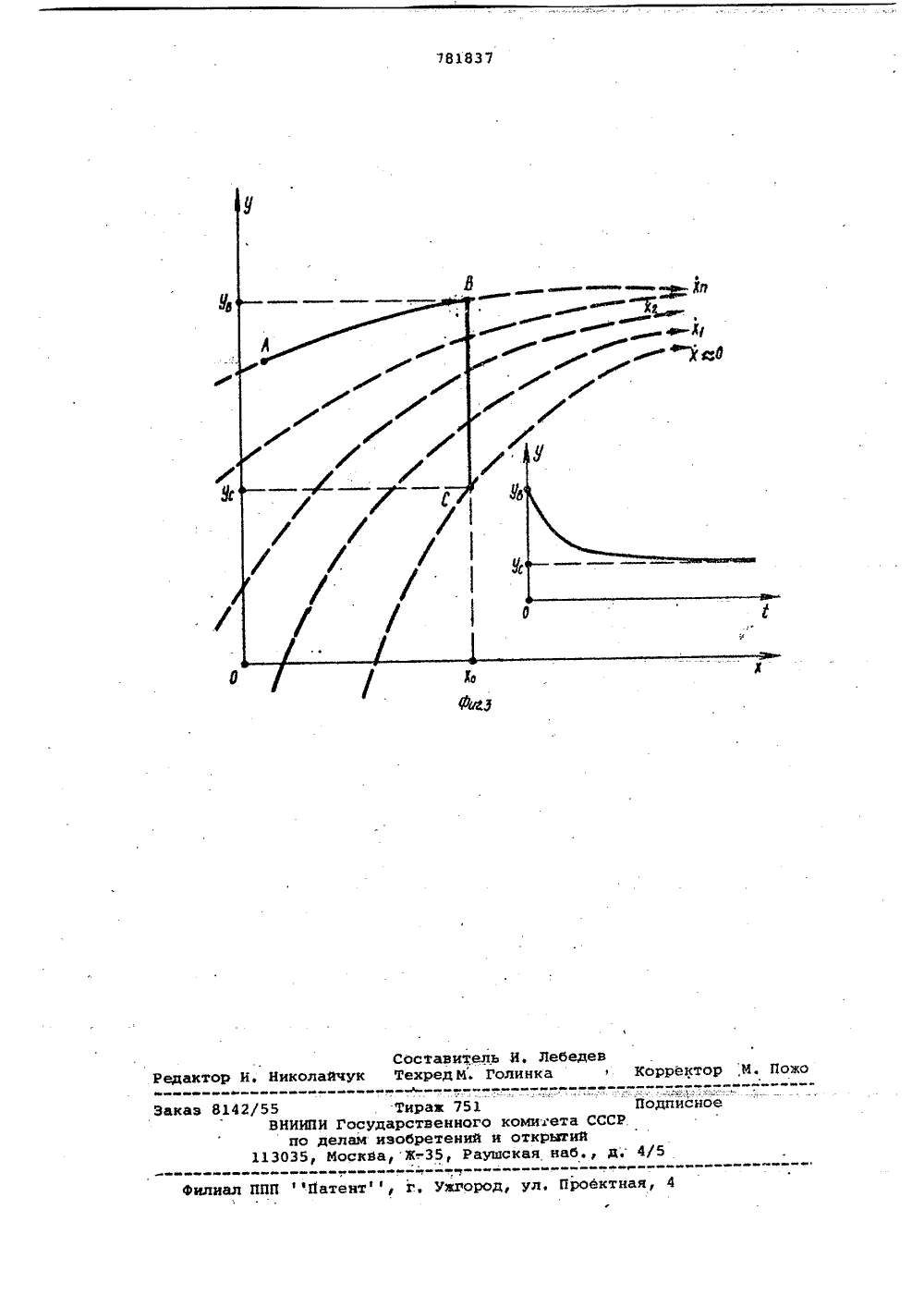

Союз Соввтскии Социалистическими Республик(51)М, Кл,з С 06 6 7/25 тосударственный комитет но делам наобретеннй н открытийДата опубликования описания 2311,80(72) Авторы изобретения 10,П. Бусаров и А,ф, Верлань Горьковский политехнический институт им, А,А, Жданова.и институт электродинамики АН Украинской ССР(54) УСТРОИСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПЕТЛИ ГИСТЕРЕЗИСАИзобретение относится к моделированию процессов в физических систе"мах при произвольных воамущающих воздействиях и любых исходных начальныхцанных, Устройство может быть применено при моделировании на аналоговых вычислительных машинах систем,включающих элементы с гистереэисом,такие как упруго-демпфирующие элементы (образцы и конструкции из металлов, полимеров и др, материалов),узлы трения, магнитные элементы,сегнетоконденсаторы и т,д,Известно устройство для моцелирования петли гистерезиса, содержащееблок воспроизведения однозначнойкривой, сумматор, блок воспроизведения двузначной кривой типа Эллипс, выходной инвертор, дифференциатор и поляризованное реле, причем 20блок воспроизведения двузначной кривой содержит накопитель, входнойсумматор, инвертор, дополнительныйсумматор, умножитель, схему извлечения квадратного корня и масштабный 25усилитель 1),Это устройство не позволяет моделировать реальные гистерезисныепетли, которые, как правило, по Форме далеки от эллиптической. На прак тике Форма петли может существенноменяться в зависимости от амплитудыи частоты входного сигнала элемента.с гистереэисом. Наиболее близким по техническому решению к предлагаемому является устройство, состоящее из дпфференциатора, блока управления, ключа, двух Функциональных преобразователей, блока перемножения и интегратора, Входной сигнал х(С) подается непосредственно на вход дифференциатора и первые входы Функциональных блоков, С выхода дидференциатора производная входного сигнала подается на вход управляющего блока, реаги" рующего на знак х(Ц, и на первый вход блока умножения, При положительном знаке х(с) управляющий блок подключает на второй вход блока умножения через ключ выход первого Функционального блока, при отрица" тельном знакех(т.) - выход второго Функционального блока. Сигнал с блока умножения подается на вход интегратора, на выходе которого получается выходной сигнал у(1) устрой" ства моделирования гистерезиса, Этот сигнал у(с) задается одновременно на вторые входы Функциональных блоков 2),Описанное устройство осуцествляет решение дифференциальных уравнений(Ю д а. Рх,у дх О,которые описывают семейства интеграль первого ключа, первый и второй информационнь входы которого подключенысоответственно к выходам первого ивторого Функциональных, преобразова"телей, первые входы которых подключены ко входу первого, блока дифференцирования, являющемуся входам устройства, выход первого ключа соединенс первым входом первогб блока умножения, второй вхбд которого подключен к выходу первого блока дифференцирования, а выход первого блокаумножения соединен с первым входомблока интегрирования, выход которого"является выходом устройства и соединен со вторыми входами первого ивторого функциональных преобразо 35 40 эателей, дополнительно введены второй блок дифференцирования, третий и 45четвертый Функциональные преобразова" тели, второй ключ, второй блок умножения и вычислительный блок, причемпервые входы третьего и четвертого функциональных преобразователей обае" 5 О динены и являются входом устройства,вторыевходы третьего и четвертогофункциональных преобразователей, подключены к выходу блоха интегрирования, выход вычислительного блокасоединен с третьими входами функциональных преобразователей и со входомвторого блока дифференцирования,выход которого подключен к первому входу второго блока умножения, выходкоторого соединен со вторим входом блокй интегрирования, выходы третьего и четвертого Функциональных преобразователей соединены соответственнос первым и вторим ийформациоинымивходами второго ключа, управляющий ных кривых. Восходяцйе и нисходяциеветви произвольного гистереэйсного. . цикла располагаются н 6 соответбтвуюцих интегральных, кривЫх,Однако, известное Устройство неучитывает релаксационнЫе явления эгистерезисе, 15Цель изобретения - )чет в моделипетли гистерезиса релаЖсационнымявлений с непрерывным епектрой распределения параметров и, слецоэательно, повышение точности работыустройства моделирования петли гисте- Орезиса,для достижения цели в устройстводля моделирования петли гистереэиса,содержащее первый блок дифференцирования, выход которого соединен со 25входом блока управления, выход которого соединен с управляющим входом вход которого подключен к,выходу блока управления, причем выход второ" го ключа соединен со вторым входом второго блока умножения, выход первого блока дифференцирования подключен ко входу вычислительного блока.На Фиг. 1 представлена блок-схема предлагаемого устройства моделирования петли гистереэиса; на фиг. 2 произвольный гистереэисный цикл (сплошные линии) как результат пере" сечения двух семейств интегральных кривых (пунктирные линии) на Фиг,3 явление релаксации в элементе с гистерезисом (вдоль АВ - скоростное нагруженйе элемента, вдоль ВС - релаксация, выражаюцаяся в плавном спаде выходного сигнала при Фиксации уровня входного сигнала). Пунктирными линиями изображены кривые нагружения, получаемые при разных фиксированных скоростях изменения входного сигнала х.Устройство содержит первый блок 1 дифференцирования, второй блок 2 дифференцирования, блок 3 управления, первый Функциональный преобразователь 4, второй Функциональный преобразователь 5, третий функциональный преобразователь 6 и четвертый функциональный преобразователь 7, первый ключ 8, второй ключ 9, первый блок 10 умноженйя и второй блок 11 умножения, блок 12 интегрирования, вычислительный блок 13,Принцип работы устройства состоит в следующем,Входной сигнал х(1) задается навход первого блока 1 дифференцирования, на выходе которого получаемсигнал производной х, .и на первые входы функциональных преобразователей 4-7. Сигнал производнойх. с выхода первого блока дифференцирования поступает на вход блока3 управления, реагирующего на знакх(Т), на второй вход первого умножителя 10 и вычислительный блок 13,на выход которого получается сигнал г,) )с(1,э)х(в)дэ, Этот сигнал,поступает на третьи входы функциональных преобразователей. В резуЛьтате на ихвыходах получаем: с перваго 4 - сигнал Еи(х,у,г), со вто"рого 5 - Е(х,у,ю), с третьего 6 Еи(х,у,г) и с четвертого 7Е 2 (х,у,г) . Блок 3 управления, эзависимости от знака сигнала производной х, подключает через первыйключ 8 на первый вход первого умножителя 10 либо сигнал Е,(х,у,г) свыхода первого Функционального преобразователя 4,либо сигнал Е(х,у,й)с выхода второго функционального преобразователя 5,через второй ключ 9 напервый вход второго умножителя 11подключается либо сигнал Ец(х,у,й)с выхода третьего Функциональногопреобразователя б, либо сигналЙ(х,у,г) с выхода четвертого функционального преобразователя 7.При подаче на второй вход первогоумножителя 10 сигнала х на еговыходе получается в зависимости отзнака х либо сигнал хЕ(х,уя)(х т О), либо сигнал хГ (х,у,к)(хс 0),которые поступают на первый входблока 12 интегрирования, На второйвход второго умножителя 11 задаетсясигнал г ЗЦ 31 с выхода второгоблока 13 дифФеренцирования, на вход,которого задается сигнал е с выхода вычислительного блока 13. Врезультате этого на выходе квадра;тора 11 в зависимости от знака х(Т)получается либо сигнал ай(х,у, а)15(хО), либо сигнал эй(х,у,з) (хсзр).,которые поступают на второй нходблока 12 интегрирования, на выходекоторого получается выходной сигналу(1) устройства моделирования петлигистерезиса, поступающий на вторыевходы Функциональных преобразовате-лей, Гистерезисные циклы произволь"ной формы можно наблюдать на экранеиндикатора, задавая на него однонре- дменно входной х и выходной у(С)сигналы,Таким образом, предлагаемоеустройство позволяет при моделировании гистерезиса учитывать релаксационные явления с непрерынным спектром,распределения параметров и тем самымповысить точность моделирования физических систем с гистерезисом,35формула изобретенияУстройство для моделирования петли гистерезиса, содержащее первый блок дифференцирования, выход которого соединен со входом блока управления, 4 О выход которого соединен с управляю" щим нходом первого ключа, первый и второй информационные входы которого подключены соответственно к выходам первого и второго функциональных преобразователей, первые нходы которых подключены ко входу первого блока дифференцирования, являюцемуся входом устройства, выход первогоключа соединен с первым входом первого блока умножения, второй входкоторого подключен к выходу перногоблока дифференцирования, а выходпервого блока умножения соединен спервым входом блока интегрирования,выход которого является выходомустройства и соединен со вторымивходами первого и нторого Функциональных преобразователей, о т л ич а ю щ е е с я тем, что, с цельюповышения точности моделирования,в устройство дополнительно введенывторой блок дифференцирования, третий и четвертый функциональные пре"обраэователи, второй ключ, второйблок умножения и вычислительныйблок, причем первые входы третьегои четвертого функциональных преобразователей объединены и являются входом устройства, вторые входы третьего и четвертого Функциональных преобразователей подключены к выходублока интегрирования, выход вычислительного блока соединен с третьимивходами Функциональных преобразователей и со входом нторого блокадифференцирования, выход которогоподключен к первому входу второгоблока умножения, выход которого соединен со вторым входом блока интегрирования, а выходы третьего и четвертого функциональных преобразователей соединены соответственно спервым и вторым информационнымивходами второго ключа, управляющийвход которого подсоединен к выходу .,блока управления, причем выход второго ключа соединен со вторым входом второго блока умножения, выходпервого блокадифференцированияподключен ко входу. вычислительногоблока.источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 378890, кл. О 06 6 7/48, 1971.2. Авторское свидетельство СССР9 525972, кл. 6 06 С 7/48, 1974Подпианое 4/5 илиал ППП фПатент г ужгород, ул. Проектная, т тЕв аказ 8142/55 ВНИНПИ Госу по делам 113035 Москаеее тв аа ав тт т ав т и ва т авв ев ттТираж 751арственного комитета СССэобретений и открытий

СмотретьЗаявка

2622339, 01.06.1978

ГОРЬКОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. А. ЖДАНОВА, ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УКРАИНСКОЙ ССР

БУСАРОВ ЮРИЙ ПАВЛОВИЧ, ВЕРЛАНЬ АНАТОЛИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G06G 7/25

Метки: гистерезиса, моделирования, петли

Опубликовано: 23.11.1980

Код ссылки

<a href="https://patents.su/5-781837-ustrojjstvo-dlya-modelirovaniya-petli-gisterezisa.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования петли гистерезиса</a>

Предыдущий патент: Разностно-логарифмический преобразователь

Следующий патент: Функциональный преобразователь

Случайный патент: Устройство для поверки индикаторов часового типа