Устройство для исправления ошибок в волоконно-оптических системах передачи информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

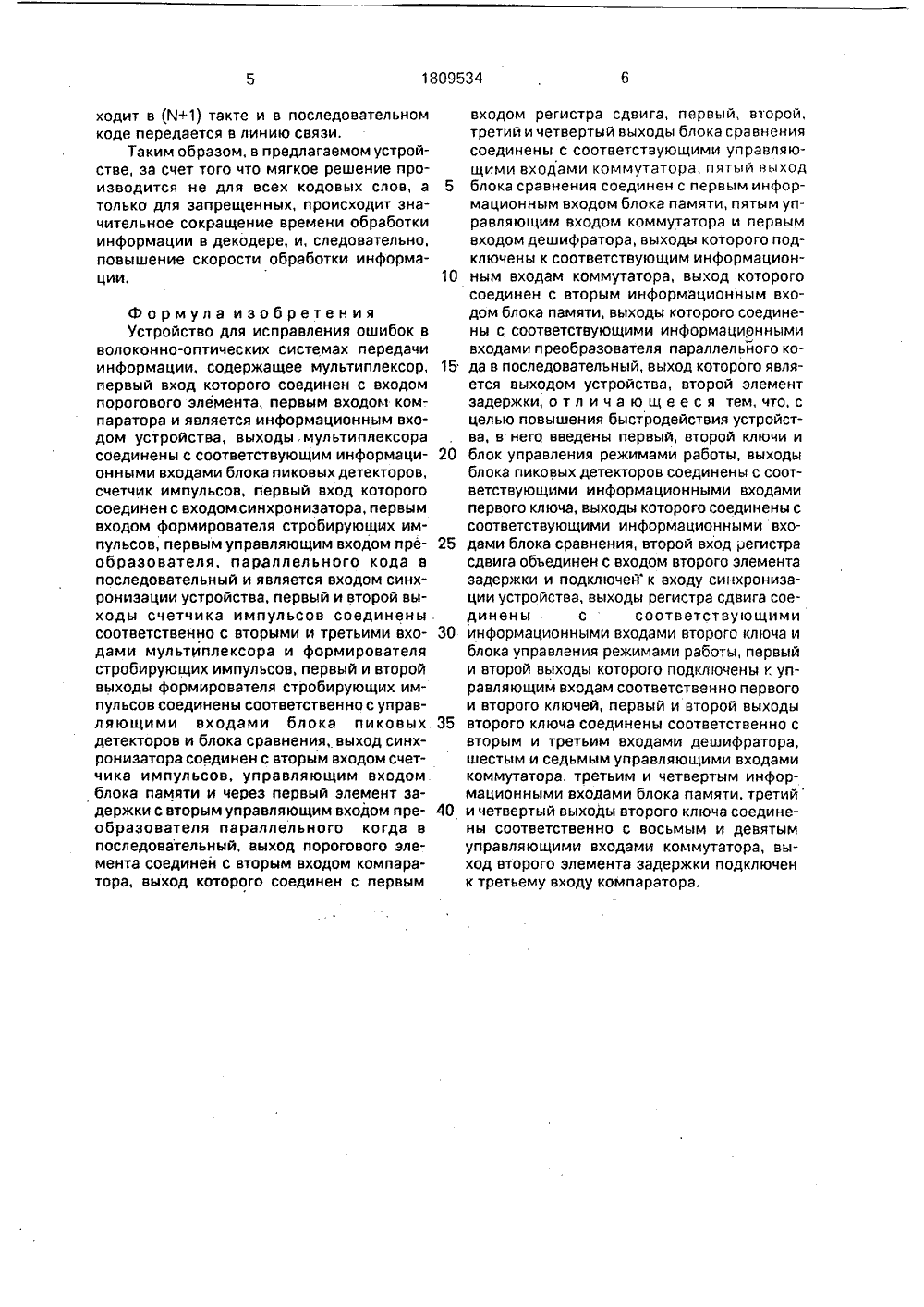

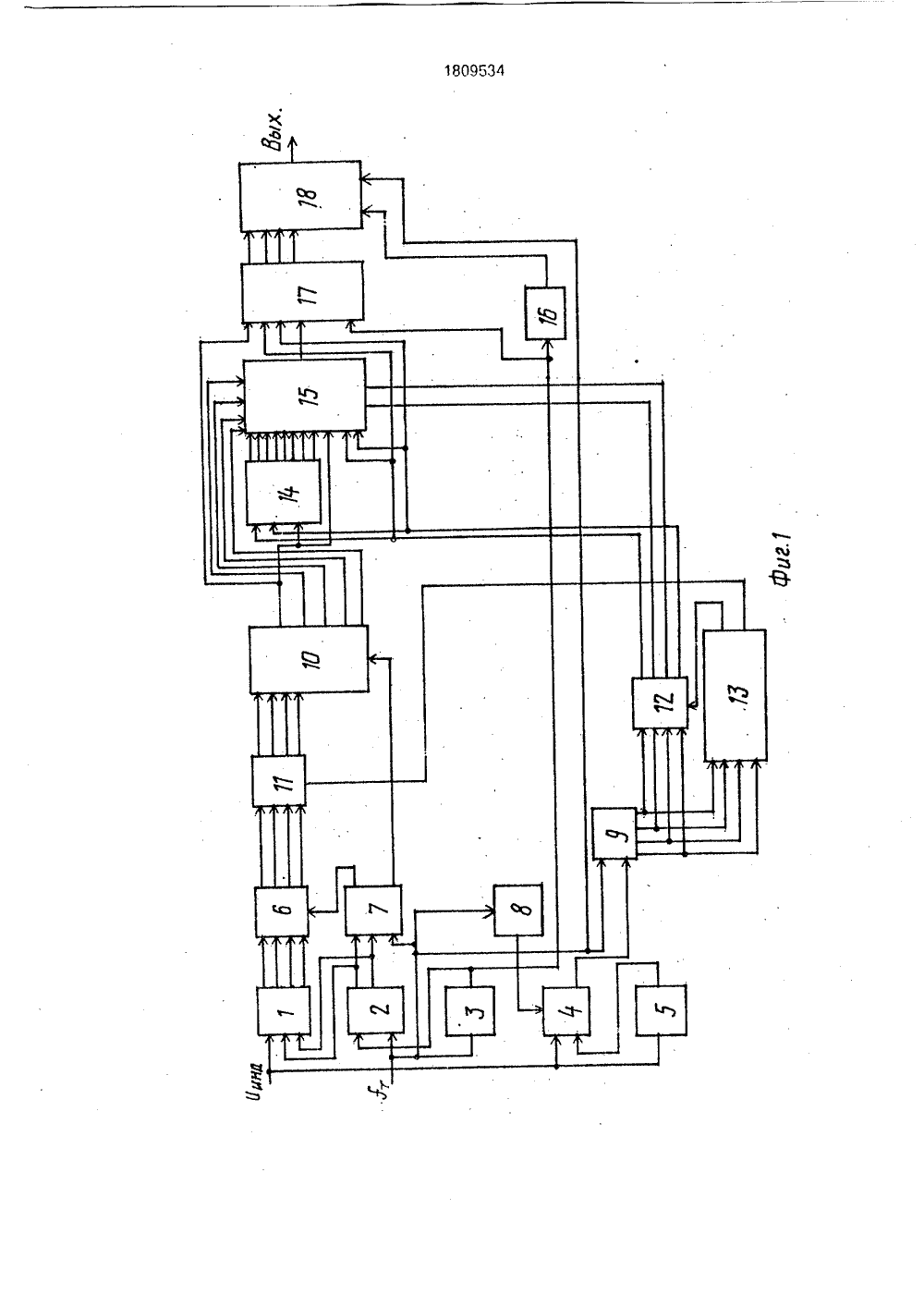

) (1) ОЗМ 51 ГОСУДАРСТВЕННОЕ ПАТЕНВЕДОМСТВО СССР(56) Авторское свидетельство СССРВ 1367028, кл. Н 03 М 5/12, 1988,Авторское свидетельство СССРМ 1608730, кл. Н 03 М 5(12, 1.989. 54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯОШИБОК В ВОЛОКОННО-ОПТИЧЕСКИХСИСТЕМАХ ПЕРЕДАЧИ ИНФОРМАЦИИ Изобретение относится к вычислительной технике и может быть использовано для исправления ошибок в волоконно-оптических системах передачи информации.Целью изобретения является повышение быстродействия устройства.На фиг.1 приведена структурная схема предлагаемого устройства; на фиг,2 - эпюры напряжений в различных точках устройства,Устройство содержит мультиплексор 1, счетчик 2, синхронизатор 3, компаратор 4, пороговый элемент 5, блок 6 пиковых детекторов, блок 7 формирования стробирующих импульсов, два элемента задержки 8 и 16, регистр 9 сдвига, блок 10 сравнения, два ключа 11 и 12, блок 13 управления режимами работы, дешифратор 14, коммутатор 15, блок 17 памяти, преобразователь 18 параллельного кода в последовательный,Устройство работает следующим образом.Пусть для передачи информации в волоо-оптической цифровой системе пере(57) Изобретение относится к вычислительной технике и может быть использовано для исправления ошибок в волоконно-оптических системах передачи информации. Целью изобретения является повышение быстродействия устройства. Устройство содержит мультиплексор, счетчик, синхронизатор, компаратор, пороговый элемент, блок пиковых детекторов, блок 7 формирования стробирующих импульсов; два элемента задержки, регистр сдвига, блок сравнения, два ключа, блок управления режимами работы, дешифратор, коммутатор, блок памяти, преобразователь параллельного кода в последовательный. 2 ил. дачи используется код ЭВВ, который трем двоичным символам ставит в соответствие д блок из четырех двоичных символов, причем, минимальное кодовое расстояние = 1. На информационный вход устройства поступают сигналы, искаженные помехой. Входной сигнал (фиг.2 а) поступает на вход мультиплексора 1, который управляется счетчиком - а 2, Счетчик 2 срабатывает по импульсам так-0 р товой частоты (фиг,2 б) и синхронизируется импульсно-блочной частоты (фиг.2 в), вырабатываемой синхронизатором 3, На первом выходе мультиплексора 1 формируется сигнал (фиг.2 г), соответствующий отсчету пер- Ы вого разряда Х 1, принятого кодового слова Ь Х, на втором выходе мультиплексора 1 формируется сигиея (фиг.2 д) соответствуюотии ) отсчету второго разряда Х 2 принятого сигнала Х и т,д, (фиг,2 е и фиг.2 ж). Таким образом, на вход устройства поступает вектор сигналов - Х 1, Х 2, Хэ, Х 4.Синхронизатор 3 формирует сигнялы блочной синхронизации, соответствующие началу кодового слова. С выхода мультиплексорэ 1 принятый сигнал в параллель-. словом, то замыкается второй ключ 12, и ном коде поступает нэ соответствующие размыкается первый ключ 11,т.е. принимавходы блока, пиковых детекторов, управля- ется только жесткое решение. Если же оценемых сигналом с выхода блока 7 формиро- ки жесткого решения не, совпадают ни с вания стробирующих импульсов (фиг.2 м). 5 одним из разрешенных кодовых слов, то Блокбпиковыхдетектороввыбираетмакси- замыкается первый ключ 11 и размыкается мал ьное значение сигнала на входе второй ключ 12 и информация поступает на (фиг.2 г,д,е,ж) и запоминает его до конца ко. блок сравнения и т.д., по схеме, т.е. принидового слова(фиг.2 з,и,к,л). Блок 7 формиро- мается мягкое решение, Таким образом, вания стробирующих импульсов 7 "О мягкое решение производится не для всех генерируетимпульсысдлительностью, рав- кодовых слов, а только для запрещенных, ной 0 25 периода тактовой частоты итолько что дает возможность повысить скорость в те моменты, когда на его первых двух обработки информации в декодере, входах присутствуют сигналы логической Блок сравнения 10 осуществляетследу- "1", а на третьем входе отрицательный пе ющие сравнения; Х 1 Х 2; Х 2 Хз; Хз Х 4; репад напряжения, что соответствует сере- Х 1 Хз, Х 2 Х,дине четвертого тактового интервала, т,е. В случае, выполнения неравенства на четвертого разряда принятого кодового сло- соответствующих выходах блока сравнений ва, при этом сигнал с неинвертирующего 10 формируется сигнал логической "1", а в выхода проходит через элемент задержки 20 случае невыполнения - сигнал логический на 0,25 такта, находящийся внутри блока 7 "0",формирования стробирующих импульсов Сигнал с первого выхода блока сравне(фиг,2 м), а сигнал с инвертирующего выхода ний 10 поступает на третий адресный вход (фиг,2 н)поступает на выход без задержки. дешифратора. 14, на первые два адресных Таким образом, сброс блоков пиковых де входа которого поступают сигналы с четвертекторов происходит после того, как на нем того и первого выхода регистра 9, Все зти запомнится максимальное значение приня- три сигнала являются адресом для дешифтого кодового слова. Входной сигнал Х ратора 14 и в соответствии с пришедшей фиг,2 а) поступает также на вход компарато- двоичной комбинацией активизируется сора 4, на второй вход которого поступает ЗО ответствующий выходдешифратора 14. Высигнал с выхода порогового злемента 5, а на ходы дешифратора 14 подключены к управляющий вход компаратора поступает информационным входам коммутатора 15, сигнал тактовой частоты компаратороткры- Вышеприведенные адресные сигналы девается уровнем логического "0". шифратора 14 поступают так же и на седьВ моменты времени, задаваемые отри- З 5 мой, восьмой и девятый управляющий цательным перепадом тактовой частоты и. входы коммутатора 15 и на первые три инсоответствующие середине тактового ин- формационныевходы блокапамяти 14, Комтервала, компаратор 4 осуществляет срав- мутатор 15 пропускаетнавыходтолькоодин нение принятого сигнала со значением. соответствующий результат сравнения в порога, и, если сигнал превышает порог, то 40 каждом конкретном случае, задаваемом на выходе компаратора 4 формируется сиг- сигналами управления.нал логической "1". В противном случае сиг- Выход коммутатора 15 подключен к пянал логического "О" (фиг.2 о). Фактически, в тому информационному входу блока памяти компэраторе 4 формируются оценки жест, в который заранее записаны необходикого решения. Величина порога (фиг.2 а) вы мые кодовые слова по соответствующему бирается расной половине амплитуды адресу. Каждый поступающей комбинации принятого сигнала, С выхода компаратора 4 блок памяти 17 ставит в соответствие одно вектор оценки жесткого решения поступает кодовое слово, т,е. происходит восстановлена второй вход регистра сдвига 9, на первыйние регенерация) принятого кодового словход которого поступает сигнал тактовойча ва. Полученный на выходе блока памяти 17 стоты с задержкой, На выходе регистра 9 четырехразрядный параллельный код формируются четыре оценки жесткого ре- фиг.2 р) поступает на преобразователь пашения в параллельном коде, поступающие . раллельного кода в последовательный 18, на вход блока управления режимами рабо- на первый управляющий вход которого паты, 55 ступает сигнал от синхронизатора 3 черезБлок управления режимами работы второй элемент задержки 16, и на второй сравнивает результаты жесткого решения управляющий вход поступает тактовая чассо всеми возможными разрешенными сло- тота, с помощью которой осуществляется вами. Если оценки жесткого решения совпа- сдвиг информации, Таким образом, полне дают с каким-либо разрешенным кодовым восстановление й-го кодового слова нроисходит в (И+1) такте и в последовательном коде передается в линию связи.Таким образом, в предлагаемом устройстве, за счет того что мягкое решение производится не для всех кодовых слов, а 5 только для запрещенных, происходит значительное сокращение времени обработки информации в декодере, и, следовательно, повышение скорости обработки информации, 10 Формула изобретенияУстройство для исправления ошибок в волоконно-оптических системах передачи информации, содержащее мультиплексор, 15 первый вход которого соединен с входом порогового элемента, первым входом ком-. паратора и является информационным входом устройства, выходы:мультиплексора соединены с соответствующим информаци онными входами блока пиковых детекторов, счетчик импульсов, первый вход которого соединен с входом синхронизатора, первым входом формирователя стробирующих импульсов, первым управляющим входом пре образователя, параллельного кода в последовательный и является входом синхронизации устройства, первый и второй выходы счетчика импульсов соединены. соответственно с вторыми и третьими вхо дами мультиплексора и формирователя стробирующих импульсов, первый и второй выходы формирователя стробирующих импульсов соединены соответственно с управляющими входами блока пиковых 35 детекторов и блока сравнения, выход синхронизатора соединен с вторым входом счетчика импульсов, управляющим входом блока памяти и через первый элемент задержки с вторым управляющим входом пре образователя параллельного когда в последовательный, выход порогового элемента соединен с вторым входом компаратора, выход которого соединен с первым входом регистра сдвига, первый, второй, третий и четвертый выходы блока сравнения соединены с соответствующими управляющими входами коммутатора, пятый выход блока сравнения соединен с первым информационным входом блока памяти, пятым управляющим входом коммутатора и первым входом дешифратора, выходы которого подключены к соответствующим информационным входам коммутатора, выход которого соединен с вторым информационным входом блока памяти, выходы которого соединены с соответствующими информационными входами преобразователя параллельного кода в последовательный, выход которого является выходом устройства, второй элемент задержки, отл и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, в него введены первый, второй ключи и блок управления режимами работы, выходы блока пиковых детекторов соединены с соответствующими информационными входами первого ключа, выходы которого соединены с соответствующими информационными входами блока сравнения, второй вход регистра сдвига объединен с входом второго элемента задержки и подключей к входу синхронизации устройства, выходы регистра сдвига соединены с соответствующими информационными входами второго ключа и блока управления режимами работы, первый и второй выходы которого подключены к управляющим входам соответственно первого и второго ключей, первый и второй выходы второго ключа соединены соответственно с вторым и третьим входами дешифратора, шестым и седьмым управляющими входами коммутатора, третьим и четвертым информационными входами блока памяти, третий и четвертый выходы второго ключа соединены соответственно с восьмым и девятым управляющими входами коммутатора, выход второго элемента задержки подключен к третьему входу компаратора.ивринц Реда кто орректо каэ 1291 Тираж Подписное ВНИИПИ Государственногкомитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб 4/5 ро эводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

СмотретьЗаявка

4861360, 28.06.1990

ИНСТИТУТ РАДИОФИЗИКИ И ЭЛЕКТРОНИКИ АН АРМССР

МАРКАРЯН ГАРЕГИН СТЕПАНОВИЧ, МЕЖЛУМЯН РОМАН РАДИКОВИЧ, ХОНАРИ БАГРАМ

МПК / Метки

МПК: H03M 5/12

Метки: волоконно-оптических, информации, исправления, ошибок, передачи, системах

Опубликовано: 15.04.1993

Код ссылки

<a href="https://patents.su/5-1809534-ustrojjstvo-dlya-ispravleniya-oshibok-v-volokonno-opticheskikh-sistemakh-peredachi-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок в волоконно-оптических системах передачи информации</a>

Предыдущий патент: Преобразователь код мощность

Следующий патент: Устройство для преобразования дискретной информации в код

Случайный патент: Устройство для определения границы области работоспособности непрерывных технических объектов