Запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1361569

Авторы: Белков, Братальский, Смирнов

Текст

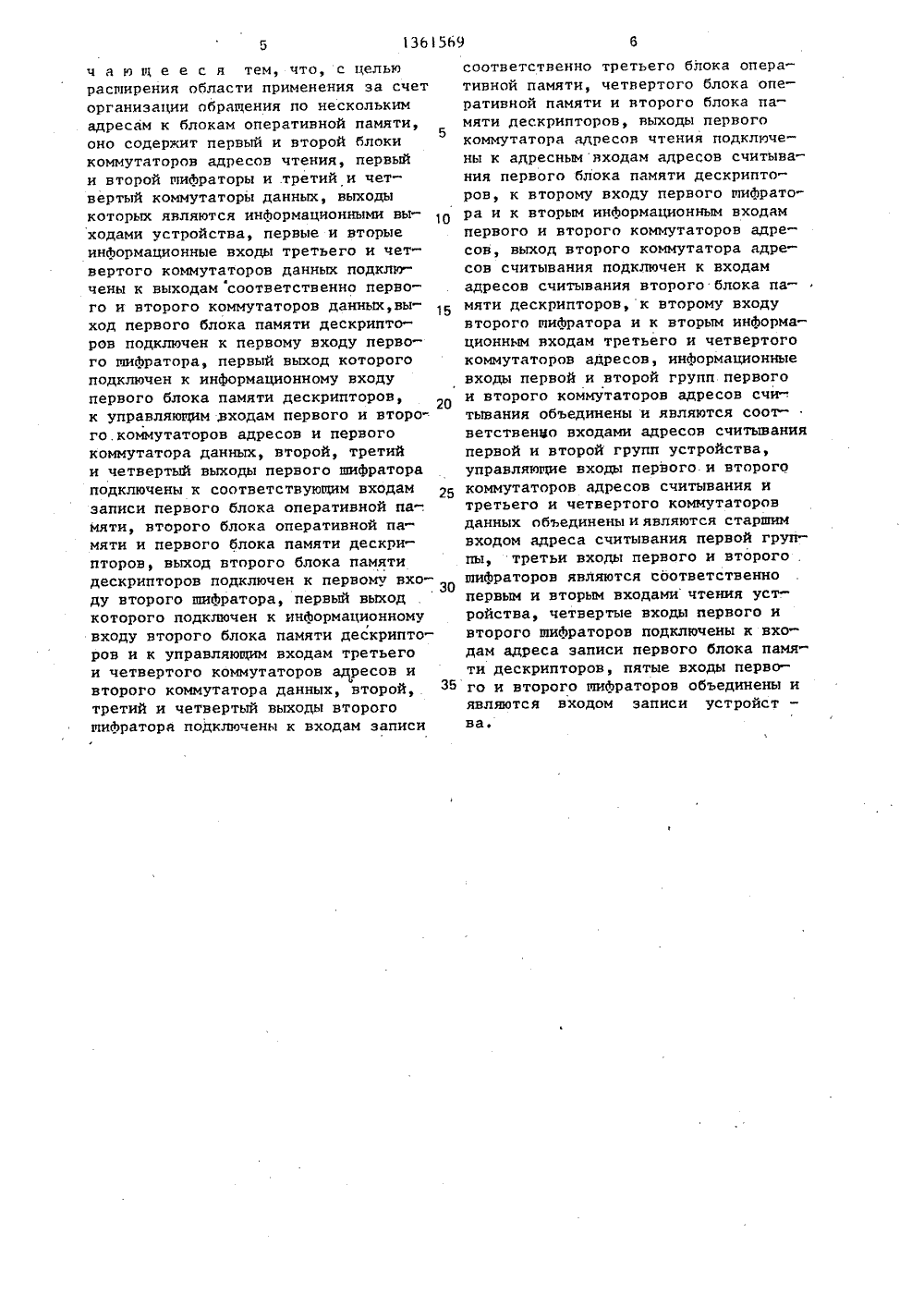

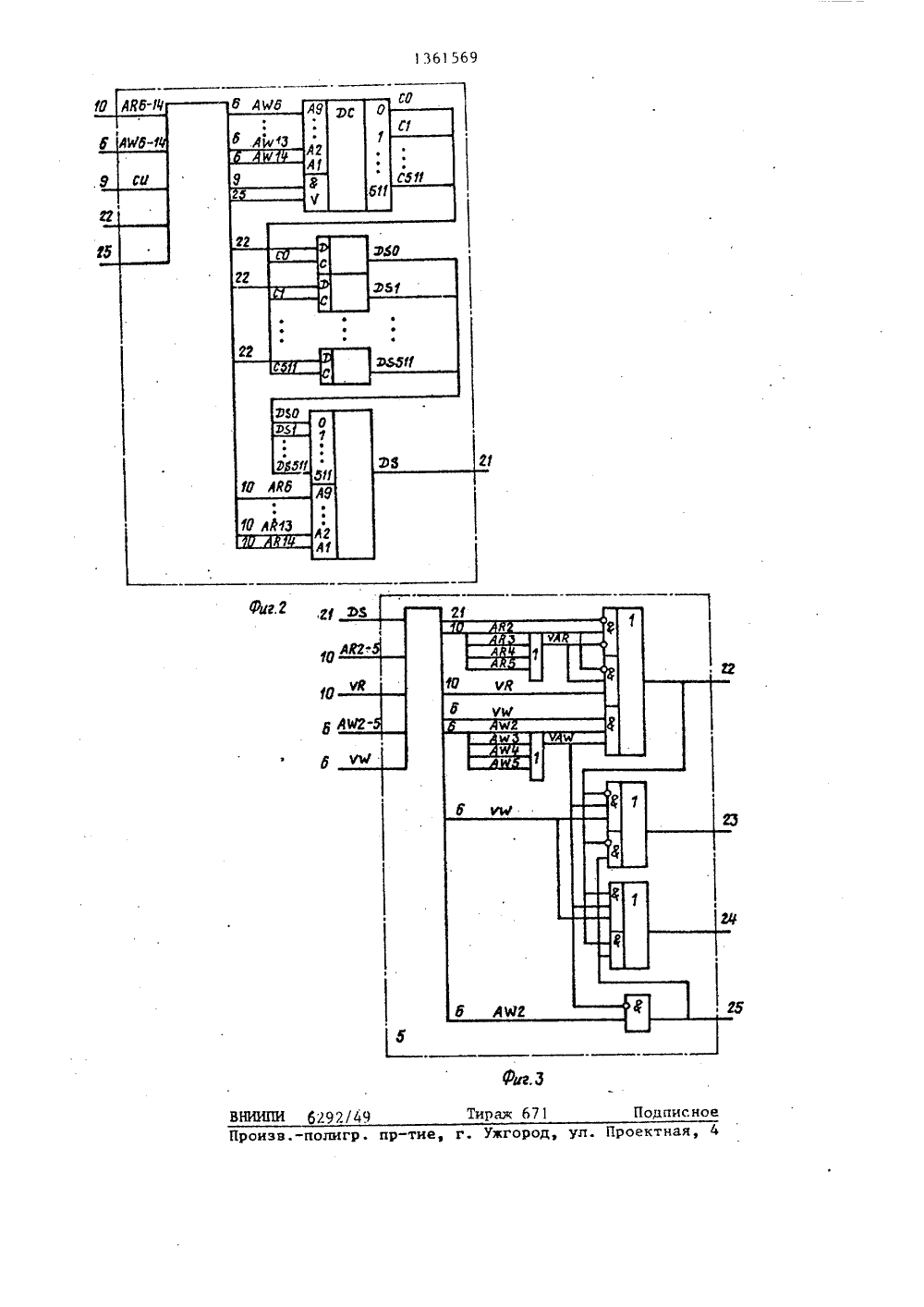

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 9) 4 Б 06 У 13/14, С 11 С 1 НИЕ ИЗОБРЕТ 0 польэовано для и ющих устройств с пом. Цель иэобре области применен ции обращения по к блокам операти ройство содержит адреса, блоки 7., торов, шифраторы 5 оперативной и 6,-6 данных. Целчто в структуру память второго у ий мы и ред.51,96 СР УСТРОЙСТВО тносится к и может быт ью бескон 4 жик ольким (трем) ычисис.1 ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ТОРСКОМУ СВИДЕТЕЛЬСТ.Энслоу. - М.: Мир, 1976, сАвторское свидетельство СМ 947866, кл. 3 06 Р 13/14,(57) Изобретение олительной технике строения запомина произвольным достуения - расширениея эа счет организанескольким адресамной памяти. Усткоммутаторы 1, 1и 2 памяти дескрип3 Зэ, блоки 5, -амяти, коммутаторы ь достигается тем,амяти встроенаовня с возможноого обращения по неадресам. 3 ил.136 10 Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройств с произвольным доступом,Цель изобретения - расширение области применения эа счет органиэации обращения по нескольким адресам к блокам оперативной памяти.На Лиг. 1 приведена структурная схема предлагаемого устройства; на Лиг. 2 - пример выполнения блока памяти дескрипторов (для объема памяти 512 адресов); на Лиг. 3 - пример реализации шифратора.Устройство содержит коммутаторы 1, и 1 г адресов чтения, блоки 2 и 2 г памяти дескрипторов, шифраторы З и 3 , коммутаторы 4,-4 4 адресов, блоки 5,-54 оперативной памяти и коммутаторы 6,-6 данных.Кроме того, устройство содержит вход 7 первого адреса чтения (1 АБ, 1 А 31 - первый разряд первого адреса чтения), вход 8 второго адреса чтения (2 АВ), вход 9 адреса записи (АМ), входы 10 и 11 чтения, вход 12 записи, информационный входд 13,. синхровходы 14 и 15, входы 16 и 17 коммутаторов 1, и 1 г адресов чтения, выходы 18 блока 2, памяти дескрипторов,выходы 19 и 20 коммутаторов 4 и 4 г адресов, выход 21 блока 2 г памяти дескрипторов, выходы 22 и 23 коммутаторов 5 и 5 адресов, выходы 24-27 шифратора 3 выходы 28 и 29 блоков 5 и 5 оперативной памяти, выходы 30-33 шифратора Зг, выходы 34 и 35 блоков 5и. 5 оперативной памяти и выходы 36-39 коммутаторов б, -6 данных.Коммутаторы 1 и 1 г предназначены для выдачи требуемого адреса чтения через коммутаторы 4,4 адресов на входы блоков 5, -5 памяти. Каждая пара блоков 5, 5 г и 5,5образует накопитель с двумя уровнями памяти - ОЗУ и СОЗУ, ОЗУ и СОЗУ имеют общие адресные и информационные цепи и различаются занимаемыми зонами в накопителях. Блоки 2 и 2 г памяти дескрипторов служат для хранения и выдачи дескрипторов при обращении к памяти второго уровня (СОЗУ), Дескрипторы ЭЯ; с выходов 18 и 21 указывают блок памяти, в котором находится информация чтения по адресу А , Например, для блоков 51 и 5 г дескриптор с выхода 18 означает 1569 20 - информация н блоке 5 ФШифраторы 3, и 3 предназначены 5 для Аормирования сигналов управленияна выходах 24-27 и 30-33, которые имеют следующий смысл: 24 - чтение из блока 5гфзапись в блок 5новое значение дескриптора;25 - разрешение записи в блок 5, 26 - разрешение записи в блок 5 г;27 - разрешение записи в блок памяти дескрипторов 2, . Коммутаторы 6, -64 служат для подачи требуемой индюрмации чтения на выходы 38 и 39 устройства.Обозначим основную память (ОЗУ) 20 через П, а память второго уровня(СОЗУ) через Р. Устройство выполняет следующий набор операций:(Р 1, в , ПЗ) - чтение 1, отсутствиечтения 2,запись ПЗ.Таким образом, первое чтение и за"пись могут относиться как к ОЗУ, таки к СОЗУ, второе чтение всегда относится к СОЗУ. Если операция вклю.;чает одно обращение к ОЗУ, то остальные относятся к СОЗУ.При этом, если обращение к ОЗУпроизводится через блоки 5, и 5 , точтение из СОЗУ выполняется через40блоки 5 з и 5, и наоборот. Запись вСОЗУ производится дважды, в оба блока по одному адресу. При выполненииоперации (Р 1, Р 2, РЗ) чтение по первому адресу Р 1 производится из пер 45 вого блока 5, и 5 г, чтение по второмуадресу Р 2 - из второго блока 5 и5, а запись РЗ производится дважды,в оба блока памяти,Каждый блок памяти выполняет следующий набор бескондпиктных операций:(Р 1, Р 2) - чтение Р 1, запись Р 2.В каждом такте блоки 5 5 и 5 54 получают по два адреса, записи и чтения, и выполнявт по два бесконАликтных обращения, Дескрипторы свыходов 18 и 21 блоков 2, и 2 определяют в накопителе блок памяти, выполняющий чтение, и блок памяти, выполняющий запись. Зона памяти СОЗУ дублируется в кажцом блоке памяти5 5 5 и 5, 5. При этом по каждому адресу используется одна из двух ячеек, вторая свободна. Иэ двух СОЗУ, размещенных в блоках 5 5 и 5, 5, образуется одно общее СОЗУ с возможностью трех бесконфликтных обращений (два чтения и одна запись).Адрес обращения к памяти ОЗУ имеет полную длину, например, для памяти емкостью 16 К слов 14 разрядов (АВ 1-14, АМ 1-14). Адрес обращения к памяти СОЗУ короче, так как объем этой памяти меньше. В рассматриваемом примере адреса СОЗУ короче на 5 разрядов (АБ 6-14, АМ 6-14). Старщий (первый) разряд первого адреса чтения (1 АВ 1), определяет блок памяти, к которому производится обращениеО - чтение иэ блоков 55;1 - чтение из блоков 5 ,5 Шифраторы 3 и 3 формируют уп равляющие сигналы на выходах 24-27, 30-33, определяющие режим обращения к памяти, Коды старщих разрядов адреса определяют режим обращения 0000 - отсутствие обращения;1000 - обращение к СОЗУ;0000 - обращение к ОЗУ,первый блок памяти;1000 - обращение к ОЗУ,второй блок памяти,АВ 2-5= АМ 2-5= В начале такта на входы устройства подаются адреса обращения 1 АВ, 2 АВ, АИ, которые могут относиться как к ОЗУ, так и к СОЗУ, и сигналы - на выходы 7-15. Коммутаторы 1, и 1 При обращении к памяти ОЗУ разряды адреса 3-5 содержат хотя бы одну 40единицу, т,е, код в этих разрядахне равен 000,Так как адресные и информационныецепи памятей ОЗУ и СОЗУ совмещены,то конструктивно они могут быть раз- . 45мещены в одних и тех же БИС ЗУПВ, выпускаемых промьпдленностью, Например,в микросхемах емкостью 16 К первые1 К адресов могут быть использованыдля СОЗУ, а остальные - для памяти 50ОЗУ,Устройство работает следующим образом. под управлением сигнала 1 АБвитают требуемые адреса чтения с выходов 16 и 17 на входы коммутаторов4 и 4, 4 , которые передают их на входы блоков 5 5 и 5, 5, При обращении к памяти ОЗУ каждый блок памяти производит требуемое обращение, чтение или запись. При выполнении обращения к СОЗУ в каждом блоке памяти сначала производится обращение по адресу чтения к бчокам 2, и 2. Прочитанные дескрипторы с выходов 18 и 21 поступают в шифраторы 3и 3, которые формируют сигналы управления на выходах 24-27, 30-33. Затем блоки 5, 5 и 5 , 5 выполняют заданные операции обращения, а блоки 2, и 2 - запись нового значения дескрипторов.Информация из блоков памяти поступает на входы коммутаторов 6, -6, которые выдают ее на выходы 38 и 39 устройства, Аналогично выполняется смещанная операция одновременного обращения к памяти ОЗУ и СОЗУ.Таким образом, в структуру оперативной памяти (ОЗУ) встроена память второго уровня (СОЗУ) с возможностью бесконфликтного обращения по нескольким (трем) адресам.Формула изобретенияЗапоминающее устройство, содержащее первый, второй, третий и четвертый блоки оперативной памяти, адресные входы которых подключены к выходам соответственно первого, второго, третьего и четвертого коммутаторов адресов, выходы первого и второго блоков оперативной памяти подключены к информационным входам первого коммутатора данных, выходы третьего и четвертого блоков оперативной памяти подключены к информационным входам .второго коммутатора данных, первый и второй блоки памяти дескрипторов, входы адресов записи которых объединены и подключены к первым информационным входам первого, второго, третьего и четвертого коммутаторов адресов и являются входом адреса записи устройства, информационные входы и входы стробирования первого, второго, третьего и четвертого блоков оперативной памяти объединены и являются соответственно информационным входом и первым синхровходом устройства, о т л и -ч а ю щ е е с я тем, что, с цельюрасширения области применения за счеторганизации обращения по несколькимадресам к блокам оперативной памяти,оно содержит первый и второй блокикоммутаторов адресов чтения, первыйи второй шифраторы и .третий и четвертый коммутаторы данных, выходыкоторых являются информационными выходами устройства, первые и вторыеинформационные входы третьего и четвертого коммутаторов данных подключены к выходам соответственно первого и второго коммутаторов данных,выход первого блока памяти дескрипторов подключен к первому входу первого шифратора, первый выход которогоподключен к информационному входупервого блока памяти дескрипторов,к управляющим входам первого и второго,коммутаторов адресов и первогокоммутатора данных, второй, третийи четвертый выходы первого шифратораподключены к соответствующим входамзаписи первого блока оперативной па-.мяти, второго блока оперативной памяти и первого блока памяти дескрипторов, выход второго блока памятидескрипторов подключен к первому входу второго шифратора, первый выходкоторого подключен к информационномувходу второго блока памяти дескрипторов и к управляющим входам третьегои четвертого коммутаторов адресов ивторого коммутатора данных, второй,третий и четвертый выходы второгошифратора подключены к входам записи соответственно третьего блока оперативной памяти, четвертого блока оперативной памяти и второго блока памяти дескрипторов, выходы первого 5коммутатора адресов чтения подключены к адреснымвходам адресов считывания первого блока памяти дескрипторов, к второму входу первого шифратора и к вторым информационным входампервого и второго коммутаторов адресов, выход второго коммутатора адресов считывания подключен к входамадресов считывания второго блока памяти дескрипторов, к второму входувторого шифратора и к вторым информационным входам третьего и четвертогокоммутаторов адресов, информационныевходы первой и второй групп первогои второго коммутаторов адресов считывания объединены и являются соответственыо входами адресов считыванияпервой и второй групп устройства,управляющие входы первого и второгокоммутаторов адресов считывания итретьего и четвертого коммутаторовданных объединены и являются старшимвходом адреса считывания первой группы, третьи входы первого и второго .30шифраторов являются соответственнопервым и вторым входами чтения устройства, четвертые входы первого ивторого шифраторов подключены к входам адреса записи первого блока памяти дескрипторов, пятые входы перво- ЗБ го и второго шифраторов объединены иявляются входом записи устройст -ва.

СмотретьЗаявка

3999334, 26.12.1985

ПРЕДПРИЯТИЕ ПЯ М-5489

БЕЛКОВ МИХАИЛ СЕМЕНОВИЧ, БРАТАЛЬСКИЙ ЕВГЕНИЙ АВРЕЛЬЕВИЧ, СМИРНОВ АЛЕКСАНДР ПАВЛОВИЧ

МПК / Метки

МПК: G06F 13/14, G11C 11/00

Метки: запоминающее

Опубликовано: 23.12.1987

Код ссылки

<a href="https://patents.su/5-1361569-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство</a>

Предыдущий патент: Устройство микропроцессорной связи

Следующий патент: Устройство для сопряжения абонентов с магистралью

Случайный патент: Глушитель шума двигателя внутреннего сгорания