Интерполятор функций двух аргументов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1247893

Автор: Анисимов

Текст

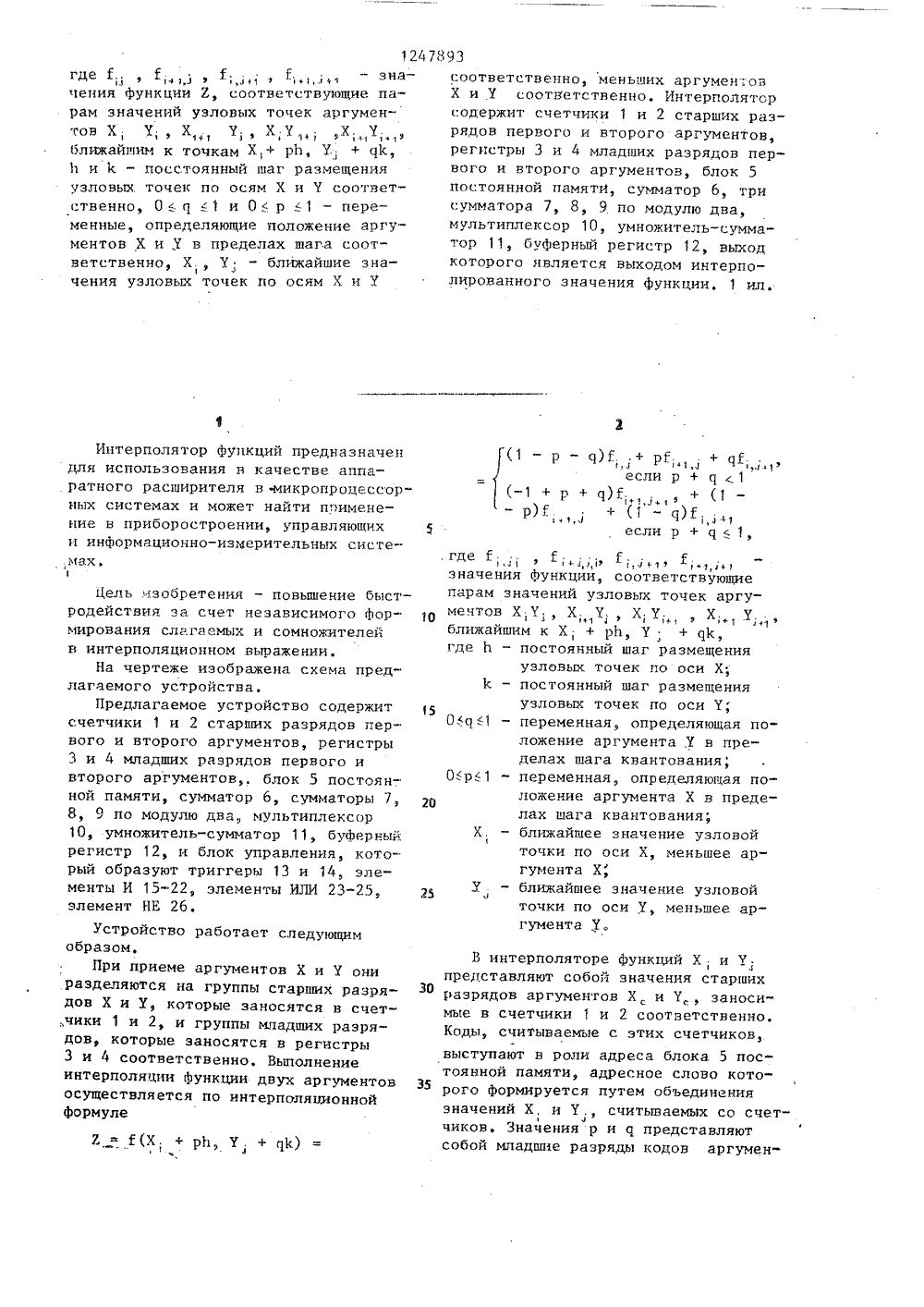

(19) 111) 8 159 4 Г 15/ УДАРСТВЕННЫЙ НОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ 1 (ф 1 юле,ОБРЕТЕНИЯ ЕТЕЛЬСТВ(54) ИНТЕРПОЛЯТОР ФУНКЦИЙ ДВУХ АРГУМЕНТОВ(57) Изобретение относится к областивычислительной техники и позволяетсократить время интерполяции фУнкцийдвух аргументов за счет независимогоформирования слагаемых и сомножителей в интерполяционном выражении,которое имеет следующий вид; ен о СССР 1980. СССР 1980+ (1 с)К, ,р + сг, 1 де Г, 2+чения Функции 2, соответствующие парам значений узловых точек аргуменближайшим к точкам Х,+ Р У + ЧЬ и 1 - посстоянный шаг размещенияузловых точек по осям Х и У соответ:твенно, О с и -1 и О с р с 1 - переменные, определяющие положение аргументов Х и У в пределах шага соответственно, Х У - ближайшие значения узловых точек по осям Х и У Интерполятор Функций предназначен для использования в качестве аппаратного расширителя в микропроцессорных системах и может найти применение в приборостроении, управляющих и информационно-измерительных систеЦель изобретения - повышение быстродействия за счет независимого формирования слагаемых и сомножителей в интерполяционном выражении.На чертеже изображена схема предлагаемого устройства.Предлагаемое устройство содержит счетчики 1 и 2 старших разрядов первого и второго аргументов, регистры 3 и 4 младших разрядов первого и второго аргументов,. блок 5 постоянной памяти, сумматор 6, сумматоры 7, 8, 9 по модулю два мультиплексор 10, умножитель-сумматор 11, буферный регистр 12, и блок управления, который образуют триггеры 13 и 14, элементы И 15-22, элементы ИЛИ 23-25, элемент НЕ 2 б. Устройство работает следующим образом.При приеме аргументов Х и У они разделяются на группы старших разрядов Х и У, которые заносятся в счет,чики 1 и 2, и группы младших разрядов, которые заносятся в регистры 3 и 4 соответственно. Выполнение интерполяции Функции двух аргументов осуществляется по интерполяционной формуле соответственно, меньших аргументовХ и У соответственно, Интерполяторсодержит счетчики 1 и 2 старших разрядов первого и второго аргументов,регистры 3 и 4 младших разрядов первого и второго аргументов, блок 5постоянной памяти, сумматор б, трисумматора 7, 8, 9 по модулю два,мультиплексор 10, умножитель-сумматор 11, буферный регистр 12, выходкоторого является выходом интерполированного значения функции, 1 ил.значения Функции, соответствующиепарам значений узловых точек аргуближайшим к Х, + рЬ, У + 1 с,где Ь - постоянный шаг размещенияузловых точек по оси Х;Е - постоянный шаг размещенияузловых точек по оси У;09 с 1 - переменная, определяющая положение аргумента У в пределах шага квантования,Орб 1 - переменная, определяющая положение аргумента Х в пределах шага квантования;Х, - ближайшее значение узловой1точки по оси Х, меньшее аргумента Х,У - ближайшее значение узловойточки по оси У, меньшее аргумента У,В интерполяторе Функций Х, и У представляют собой значения старших разрядов аргументов Х, и У заносимые в счетчики 1 и 2 соответственно. Коры, считываемые с этих счетчиков, выступают в роли адреса блока 5 постоянной памяти, адресное слово которого Формируется путем объединения значений Х, и У ., считываемых со счет 1 4Ф чиков. Значения р и и представляют собой младшие разряды кодов аргуменВ третьем такте производится вычисление следующего частичного произведения и суммирование его с результатом, полученным во втором так 3 12478 тов Х и У , считываемые с регистрови м3 и 4 соответственно.Процедура интерполяции значений функции двух переменных выполняется в предлагаемом устройстве за три такта. Первый такт начинается после выдачи сигнала на вход пуска устройства, синхронизируемого синхросерией С. При этом триггеры 13 и 14 устанавливаются в нулевое состояние, буферный 10 регистр 12 обнуляется, а в счетчики 1 и 2, регистры 3 и 4 заносятся аргументы Х и 7, разделенные на группы разрядов Х Х, У У . Управляющий код 00, устанавливаемьй на триггерах 13 и 14, поступает на логические элементы на входах счетчиков 1, 2 и обеспечивает увеличение на единицу кода в счетчике. Управляющий сигнал на вход +1 счетчика 1 поступает с выхода элемента И 19, на который поступают сигналы с инверсных плеч триггеров 13 и 14, Такое изменение кода счетчика 1 обеспечивает адресацию узловой точки Е, в блоке 5 25 постоянной памяти. Коды входных регистров 3 и 4 поступают на входы первого и второго операндов сумматора 6 и суммируются в нем. Если сумма р + Ч 11, то в первом такте нужно вычислить интерполяционный член р Г,если р + Ч 1, то вычисляется (1 - р) ф Г . Значение указанного нера 1+1,4венства определяется по разряду переноса сумматора 6, который поступает на третий вход управления мультиплек 35сора 10 и на элементы 26, 16 и 18. Если разряд переноса равен О, то р + е Чс 1, если разряд переноса равен 1, то р + Ч 1. В зависимости от значе 40 ния разряда переноса на выход мультиплексора 10 поступает код с входа А или с входа В. Соответственно с входа А поступает код 1 - р, а с входа В - . код р. Последний поступает с прямого45 выхода регистра 3, а код 1 - р формируется путем прибавления единицы в младший разряд инверсии кода р, снимаемого с инверсного выхода регистра 3. Это преобразование осуществляется в сумматоре по модулю два 7. Резуль 50 тат первого такта запоминается в буферном регистре 12 при поступлении синхросигнала С, который устанавливает также в триггере 13 код 1, т.е. код второго такта. Собственно умноже.55 ние значения узловой точки функции на код, считываемый с мультиплексора ,10, производится асинхронно и не тре 93 4бует сигналов управления, Для реализации такого матричного умножителя -сумматора 11 целесообразно использование матричного умножителя типаК 53 ИК 1.Во втором такте производится вы-"числение следующего частичного произведения и суммирование его с результатом, полученным в первом такте. Частичное произведение, вычисляемое во втором такте, имеет вид (1- Р - Ч) Е . если бит переноса навыходе сумматора 6 равен нулю, и(Р + с 1 - 1)Й,+, если бит переноса на выходе сумматора 6 равенединице. Соответствующее изменениеадреса памяти обеспечивается путемуменьшения кода счетчика 1 на единицу, если бит переноса равен нулю,или путем увеличения кода счетчика2 на единицу, если бит переноса равен единице. Уменьшение кода счетчика 1 осуществляется подачей управляющего сигнала на вход счетчикачерез элемент И 15 и элемент ИЛИ 23.Увеличение кода счетчика 2 осуществляется подачей управляющего сигналана вход + 1 этого счетчика черезэлемент И 18 и элемент ИЛИ 24. Сомножитель (1 - р - с 1) поступает наинформационный вход С мультиплексора И 1 с выхода сумматора 8 по модулю два, где к инверсии кода р + одобавляется единица младшего разряда. Сомножитель р + Ч - 1 поступаетс прямого выхода сумматора 6 приигнорировании единицы переноса. Прямой выход сумматора 6 соединен вустройстве с информационным входом0 мультиплексора 10, В зависимостиот значения бита переноса на выходесумматора 6 управляющий код на входе управления мультиплексора 1 Ообеспечивает подачу на выход мультиплексора 10 либо кода с входа С,либо кода с входа Р, что и обеспечивает получение на входе У матричного умножителя-сумматора 11 искомогосомножителя. Результат второго такта запоминается в буферном регистре12 при поступлении синхросигналаС, который устанавливает также втриггерах 13 и 14 код 01, т.е. кодтретьего такта, 1247893те. Частичное произведение, Вычисляе:мое в третьем такте, имеет Вид а.,х г,.1, ечесли р + 1; или ,1 - с)"дГ., .если р + сд 1.Выбор табличного значения Функциипооизводится следующим образом,Если бит переноса на Вьпсоде. сумма-тора 6 равен нулю, то В счетчикекод не изменяется, а в счетчике 2 че црез элемент И 17 и элемент ИГЯ 24поступает управляющий си;нял на вход+1, Если бит переноса равен единице,то управляющий сигнал поступает нявход -1 счетчика 1 через элементИ 16 и элемент ИЛИ 23. Ссмпажительсе или. самнажитель 1 - я поступаег чявход Х матричного умножителя 11 либос ВХОДЯ. Е, либО с ВходЯ ъультипле 1 сса ра 10 В зависимости ат значения би- гбта переноса. Формирование кода 1 - цв сумматоре 9 по модулю двя осуществляется также кяк и в сумматорах 7 и8, Результат третьего такта запоминается в буферном регистре 12 при пос- ,еБтуплении синхраси=нала С, Посколькутретий такт эта последний такт та,поступление синхрасигняла на вход Сбуферного регистра 12 не должно сопровождаться изменением кода в тригге"рах 13 и 14, Зта абесп чяпаатся Вустройстве следующим образом,После первеех двух тактов синхро-"сигнала поступает с Выходя элементаИ 21 который В третьем гаесте блакируется сигналам с иегверснага плечатриггера 14, В связис э.;11 м послетретьего такта синхросигняла ня счет-.нь 1 й вход триггера 13 не постуггает.На вход С буферного регисера 1 ги:-.х, росигнал поступает через элементИ 22, который открывается сигналам спрямого выхода триггера 14, Вьвсадыэлементов И 21 и 22 саеде вень с пходом С буферного регистра 12 черезйэлемент ИЛИ 25, Призна 1 сом тара, чтоВ устройстве наступкл последний тактвычислений, является сигнал Татов.,считываемый с прямого выхода тригге-"ра 14, При необходимости получениястробированного признака готовностив качестве таковога признака можетбыть использован сигнал на Вьехадеэлемента И 22,1Таким образом, в результате опи-.:санных тактов интерполяции ня Выходебчферного регистра 12 сфаркирав;п ис =камней результат,. Фовмулаизабретения Инт"рпалятор функций двух аргументов, содержащий счетчики старших разрядов первого и второго аргументов, блок постоянной памяти, регистры младших разрядов первого и второго аргументов, сумматор, буферный регистр, блок управления, выходы счетчиков стярпеих разрядов первого и вто рого аргументов подключены к первому и .второму адресным входам блока постоянной памяти, прямые выходы регист ров млацших разрядов первого и второго аргументов подключены к входам первого и второго операндов сумматора, причем блок управления содержит два триггера, пять элементов И, три элемента ИЛИ и элемент НЕ, прямые выходы первого и второго триггеров подключены к первым Входам первого и второго элементов И, о т л и ч а ю щ и й с я тем, чта, с целью повышения быстродействия за счет независимости Формирования слагаемьех 1, и сомножителей в интерполяционном Выраженепе, в него введены умнажительсумматар, мультиплексор, три сумматора па модулю ДВЯ, Входы млаДших разрядов первых операндов которых подключены к шипе потенциала логической единицы интерполятора, входы Вторых операндов с первого по третий сумматор па модулю два подключены к инверсным выходам регистров младших разрядов первого и второго аргументов и к инверсному выходу суммы сумматора, соответственно с первого па шестой информационные входы мультиплексора подключены к Выходам с первого по третий сумматор па модулю два, прямым Выходом регистров младших разрядов первого и второго аргументов и к прямому выходу суммы суммятаря саатветстВенна Выходь 1 блакЯ пастопенОЙ памяти с мульти илексора подключены к Входам первого и второго сомножителей умножителя - сумматора выход которого подключен . ИНФОВЕеацианнаму входу буферноГО регистра, Выход которого подключен к Входу слагаемого умнажителя-сумматора и является выходак значения функции интерпалятора, информационные входы счетчиков старших разрядов первого и второго аргументов являются входами старших разрядов перво го и второго аргументов интерполято1247893 ра, информационные входы регистрамладших разрядов первого и второгоАргументов являются входами младшихразрядов первого и второго аргументов интерполятора, причем в блокуправления дополнительно введены триэлемента И, выходы первого и второго элементов И подключены к первомуи второму входам первого элементаИЛИ, выход которого подключен к входу режима вычитания счетчика старшихразрядов первого аргумента, прямыевыходы первого и второго триггеровподключены к первому и второму входам адреса мультиплексора и к первымвходам третьего и четвертого элементов И соответственно, выходы которыхподключены к первому и второму входам второго элемента ИЛИ, выход кото.рого подключен к входу режима суммирования счетчика старших разрядоввторого аргумента, выход переносасумматора подключен к третьему входуадреса мультиплексора, к вторым входам второго и третьего элементов Ии через элемент НЕ к вторым входампервого и четвертого элементов И, инверсный и прямой выходы первого триггера подключены к первому входу пятого элемента И и к счетному входувторого триггера, инверсный выход которого подключен к второму входу пятого элемента И и первому входу шестого элемента И, выход которого под= .ключен к счетному входу первого триггера и к первому входу третьего элемента ИЛИ, выход и вход которого10 подключены к входу синхронизации буферного регистра и к выходу седьмогоэлемента И, первый вход восьмогоэлемента И является входом пуска интерполятора, выход готовности резуль 15 тата которого соединен с прямым выходом второго триггера и с первымвходом седьмого элемента И, входсинхронизации интерполятора соединен,с вторыми входами с шестого по вось 20 мой элементов И, выход восьмого элемента И подключен к входам сбросапервого и второго триггеров и буферного регистра и к входам синхронизации счетчиков старших разрядов перво 25 го и второго аргументов и регистровмладших разрядов первого и второгоаргументов, выход шестого элемента Иподключен к входу режима суммирова-.ния счетчика старших разрядов перво"30 го аргумента,Составитель А.УшаковТехред М.Ходанич Корректор М,Максимишинец Редактор Т.Митейко Заказ 4128/50 Тираж б 71 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

3823196, 10.12.1984

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

АНИСИМОВ АНДРЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 17/17

Метки: аргументов, двух, интерполятор, функций

Опубликовано: 30.07.1986

Код ссылки

<a href="https://patents.su/5-1247893-interpolyator-funkcijj-dvukh-argumentov.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор функций двух аргументов</a>

Предыдущий патент: Матричное вычислительное устройство

Следующий патент: Анализатор амплитудных распределений

Случайный патент: Способ контроля вакуума в герметичном сосуде