Устройство для умножения -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

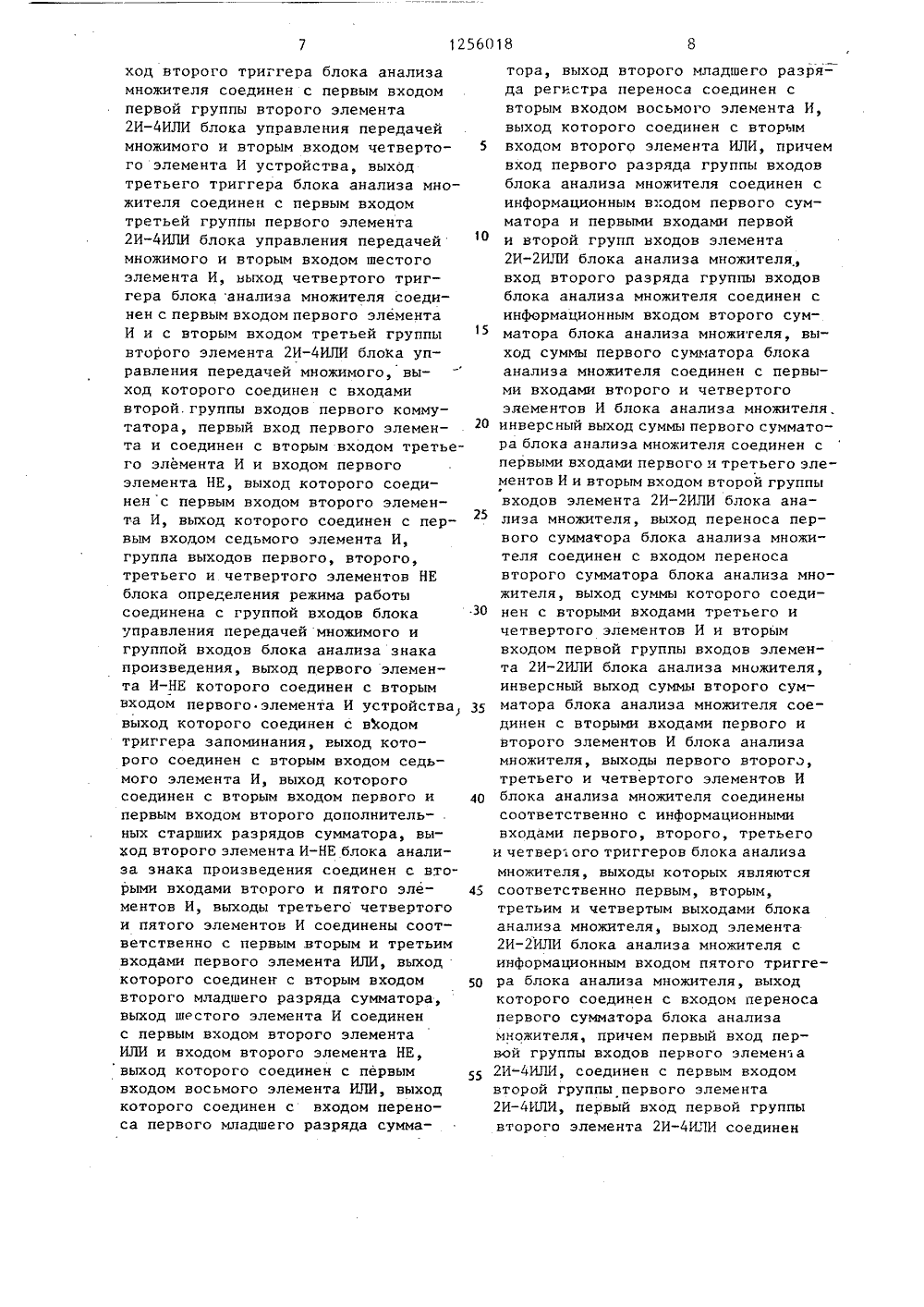

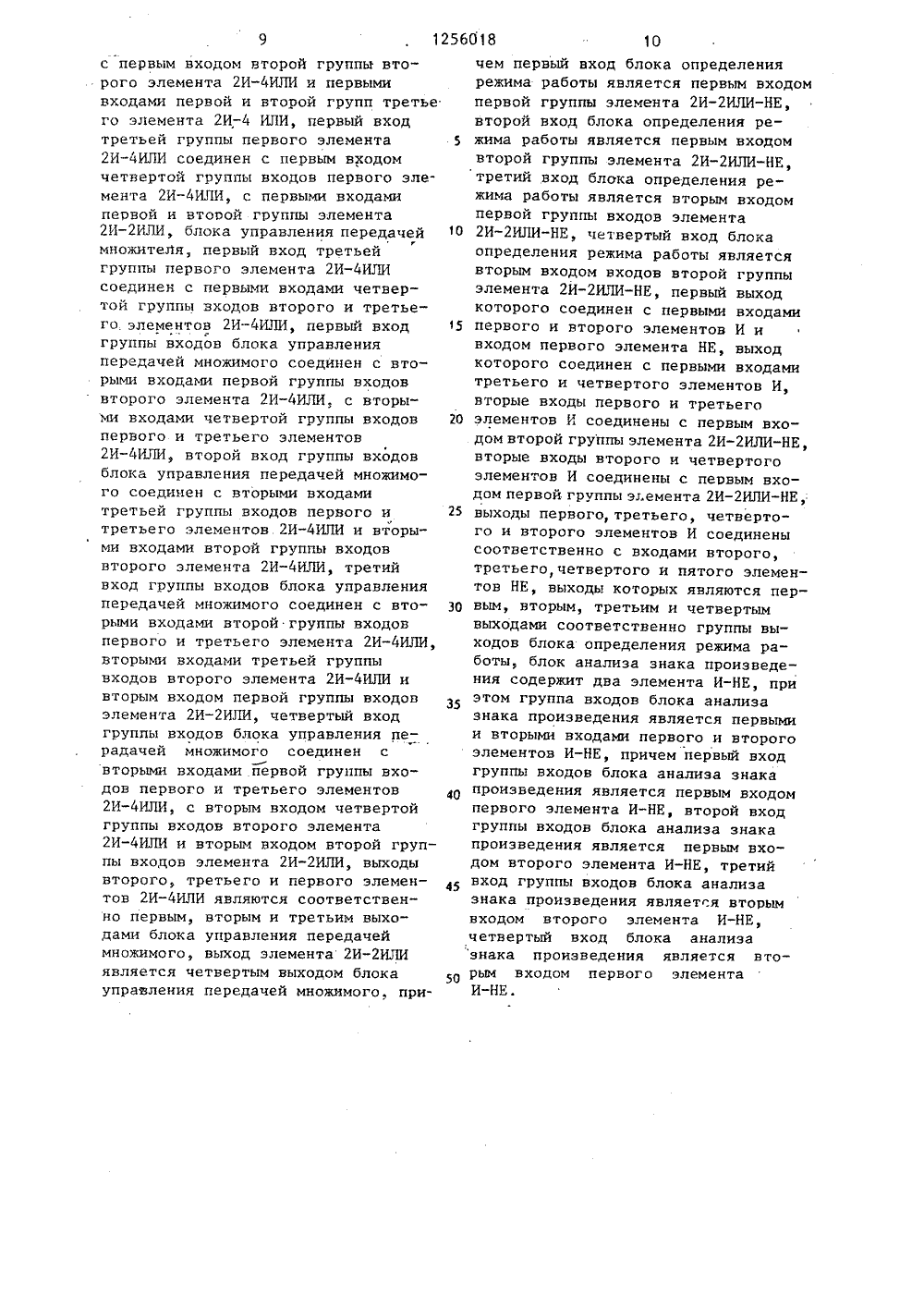

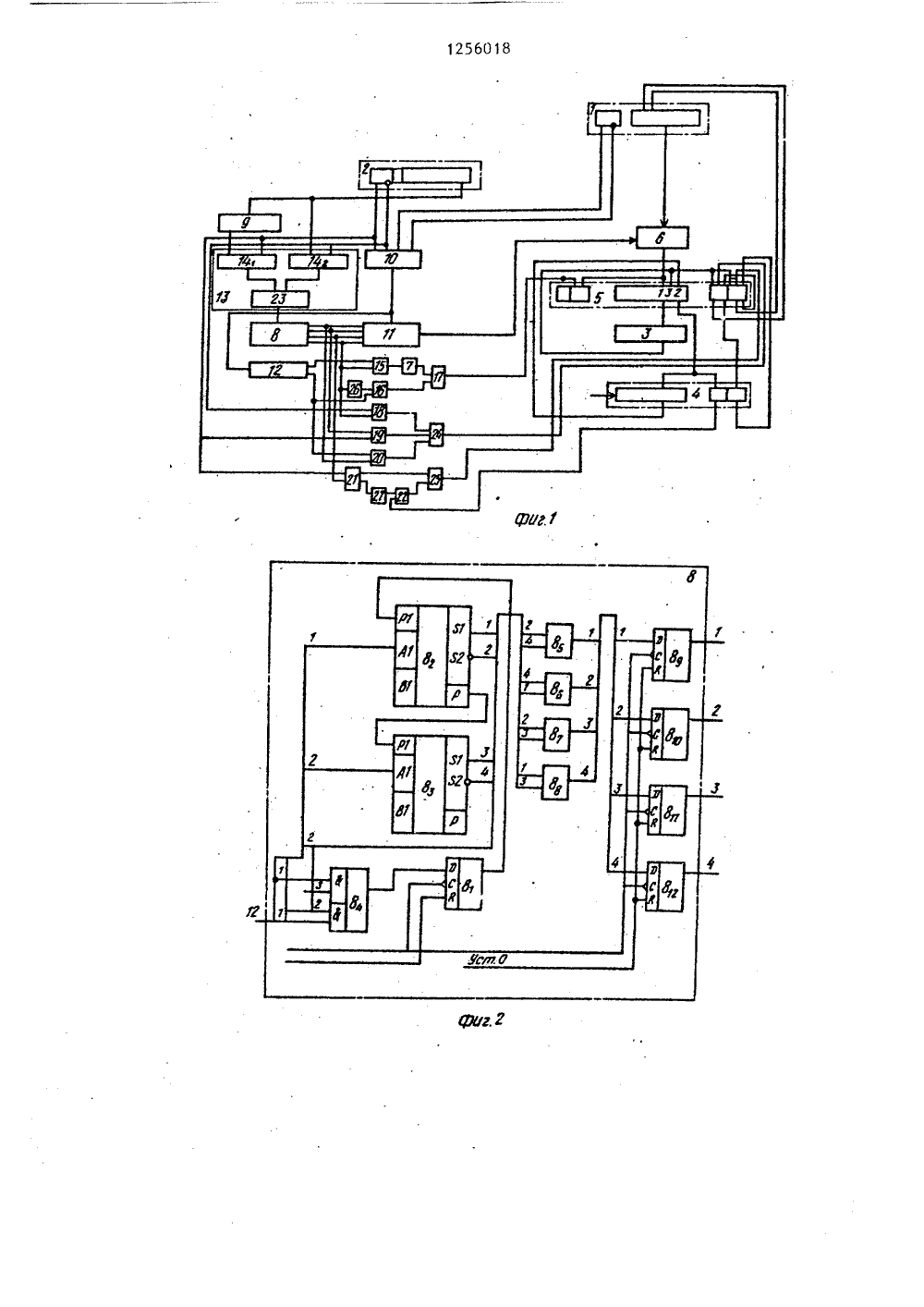

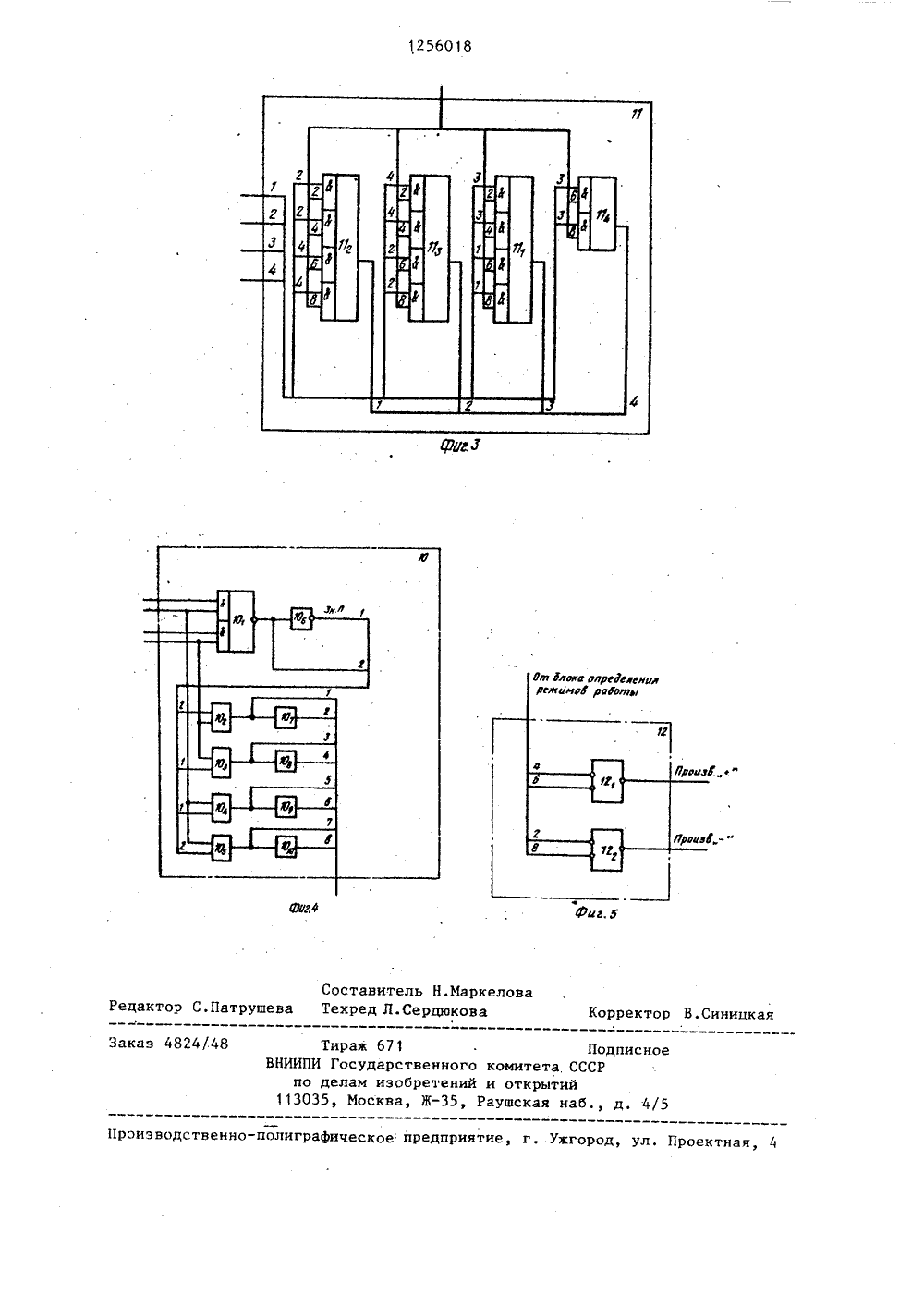

(51) 4 С БРЕТЕНИ ТВ ычисеноЦель ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ПИСАНИЕ К АВТОРСКОМУ СВИДЕТ(56) Авторское свидетельство СССР У 734683, кл, С 06 Р 7/52, 1980.Авторское свидетельство СССР У 357561, кл. С 06 Р 7/52, 1972. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И-РА РЯДНЫХ ЧИСЕЛ.(57) Изобретение относитсяк в лительной технике и предназнач для умножения двоичных чисел. изобретения - расширение функциональных возможностей, обеспечение работы устройства с положительными и отрицательными числами, представленными соответственно в прямых и дополнительных кодант-е-.автоматйческим получением отрицательных результатов в дополнительном коде. Новымв данном устройстве является введение преобразователя в дополнительный код, блока определения режимаработы, блока управления передачеймножимого, блока анализа знака произведения, десяти элементов И, элемептов ИЛИ и элементов НЕ, а в регистры множителя и множимого - знаковых разрядов. Применение предлагаемого устройства умножения варифметических устройствах позволяет повысить их быстродействие иуменьшить затраты на оборудование,так как исключаются операции преобразования отрицательных чисел навходе и выходе арифметическогоустройства. 5 ил.Изобретение относится к вычислительной технике и предназначенодля использования в специализированных и универсальных ЦВМ,Цель изобретения - расширениефункциональных возможностей путемобеспечения работы устройства с отрицательными числами, представляемыми в дополнительных кодах, с автоматическим представлением отрицательных гезультатов в дополнительном коде.На фиг. 1 представлена функциональная схема устройства; на фиг. 2 -блок анализа множителя; на фиг. 3блок управления передачей множимого,на фиг, 4 - блок определения режима работы, на фиг. 5 - блок анализазнака произведения.Устройство содержит (ь+2) разрядные регистры множимого 1, множителя 2, (ь+4) разрядный регистр 3 произведений, (и+2) разрядный регистр4 переносов, сумматор 5, первый коммутатор 6, триггер 7 запоминания,блок 8 анализа множителя, преобразователь 9 в дополнительный код, блок10 определения режима работы, блок1 управления передачей множимого,блок 12 анализа знака произведения,второй коммутатор 13; две группыэлементов И 14 и 14 , входящие всостав коммутатора, и восемь элементов И 15-22, группу элементов ИЛИ 23,входящих в состав коммутатора, дваэлемента ИЛИ 24-25, два элементаНЕ 26-27.Блок анализа множителя содержитпервый триггер 8 , первый и второйсумматоры 8 -8, элемент 2 ИИЛИ 84,четыре элемента И 8 -88, второй,третий, четвертый и пятый триггеры8 -8Блок управления передачей множимого содержит три элемента 2 ИИЛИ11 -11 и элемент 2 ИИЛИ 11Блок определения режима работысодержит элемент 2 ИИЛИ-НЕ 10четьре элемента И 10 -10, пятьэлементов НЕ 10 -10 . Блок анали 1 Оза знака произведения содержит дваэлемента И-НЕ 12 -121 2Устройство работает следующимобразом.В исходном состоянии в регистрымножителя 2 и множимого 1 записываются соответствующие сомножителисо знаками. При этом положительные 5 10 15 20 25 30 35 40 45 50 55 числа - в прямом коде и в знаковом разряде О, а отрицательные - в дополнительном код и в знаковом разряде 1.В каждом такте умножения в блоке 8 анализа множителя анализируется пара разрядов множителя. Причем, если множитель отрицательный, то анализируемая пара поступает на блок 8 через преобразователь 9, в котором осуществляется перевод дополнительного кода этой пары в прямой, через элемент И 14 г, открытый по первому входу положительным сигналом с прямого выхода знакового разряда регистра множителя 2 и первый вход элемента ИЛИ 23, если множитель положительный, то анализируемая пара поступает на блок 8 в прямом коде через элемент И 14, открытый по второму входч положительным сигналос инверсного выхода знакового разряда регистра множителя 2 и через второй вход элемента ИЛИ 23.В зависимости от комбинации разрядов анализируемой пары в блоке 8 вырабатываются соответствующие сигналы, которые поступают на 1-4 входы блока 11 управления передачей множимого. На пятый вход блока 11 поступают сигналы с выхода блока определения 10 режима работы, Режимы работы устройства определяется тем, с какими знакамигпоступают на его вход сомножители Таким образом в каждом такте умножения в зависимости от комбинации анализируемой пары и режима работы устройства блок 11 вырабатывает сигнал, который определяет в коммутаторе 6 вид передачи множимого на первый вход сумматора 5, На второй и третий входы сумматора 5 поступают коды соответственно с регистра 4 переносов и регистра 3 частичныхпроизведений, записанные в эти регистры в предыдугцем такте.Сумма по год 2, полученная на выходе сумматора 5 и представляющая частичные произведения от умножения множимогг. на два младших разряда множителя, записывается в регистр 3 частичных произведений, а поразрядные переносы с выхода сумматора 5 записываются в регистр 4 переносов. После чего осуществляется сдвиг вправо информации в регистрах 3 и 21256на 2 разряда, а в регистр 4 переносов - на 1 разряд. При этом два младших разряда произведения из регистра 3 частичных произведений переписываются в освободившиеся разряды регистра 2. А в младших разрядах того же регистра 2 оказывается 2-я анализируемая пара множителя, на которую осуществляется умножение во 2-м такте. Полученные два очеред О ных разряда произведения записываются в освободившиеся старшие разряды регистра 2 множителя.На последнем такте обеспечивает- ся умножение на последнюю пару раз рядов множителя. При этом сумматор 5 работает со сквозным переносом и в регистр 3 частичных произведений записываются старшие разряды окончательного произведения, млад шие - в регистр 2. Положительные произведения представляют в прямом1 коде со знаком О, отрицательные - в дополнительном со знаком 1.Устройство работает в четырех 25 режимах.Множимое положительное (прямой код). Множитель положительный (прямой код). Произведение положительное.При этом, если анализируемая 30 пара разрядов множителя:00 - на первый вход сумматора 5 множимое не поступает, а подаются нули;01 - на первый вход сумматора 5 множимое поступает в исходном коде,10 - на первый вход сумматора 5 множимое поступает в исходном коде, сдвинутое на 1 разряд влево,11 на первый Вход сумматора 5 40 множимое поступает в обратном коде, а в следующем такте в первый младший разряд сумматора 5 подается единица.45В два старших разряда сумматора5 в каждом следующем такте записываются нули, если комбинация этих двух старших разрядов на выходе сумматора в предыдущем такте 00, 01, 10, и записываются единицы, если комбинация 11. 2. Множимое отрицательное (дополнительный код). Множитель отрицательный (дополнительный код).Произведение положительное (прямой код). При этом, если анализируемая пара разрядов множителя: 018 400 - на первый вход сумматора5 множимое не поступает, а подаютсянули,01 - на первый вход сумматора5 множимое поступает в обратномкоде, а в следующем такте в младшийразряд сумматора 5 подается единица,10. - на первый вход сумматора 5множимое поступает в обратном коде,сдвинутое на 1 разряд влево, а вследующем такте в младший разрядсумматора 5 подается единица;11 - на первый вход сумматора 5множимое поступает в исходном коде,В два старших разряда сумматора5 в следующем такте пишутся нули,если в предыдущем такте в старшихразрядах сумматора 5 следующие комбинации 00, О 1, 1 О, и записываютсяединицы, если комбинация 11.3. Множимое отрицательное (дополнительный код). Множитель положительный (прямой код). Произведениеотрицательное (дополнительный код).При этом, если анализируемая параразрядов множителя:00 - на первый вход сумматора 5множимое не поступает, подаютсянули;01 - на первый вход сумматора 5множимое поступает в исходном коде,10 - на первый вход сумматора 5множимое поступает в исходном коде,сдвинутое на 1 разряд влево;11 - на первый вход сумматора 5множимое поступает. в обратном коде,а в следующем такте в младший разряд сумматора 2 подается единица,В два старших разряда сумматора 5в каждом следующем такте записываются единицы, если комбинации этихстарших разрядов на выходе сумматора 5 в предыдущем такте 01, 10, 11и записываются нули, если комбинация 00.4. Множимое положительное(прямой код). Множитель отрицательный (дополнительный код). Произведение отрицательное (дополнительныйкод).При этом, если анализируемая пара разрядов множителя:00 - на первый вход сумматора 5множимое не поступает, а подаютсянули,01 - на первый вход сумматора 5множимое поступает в обратном коде,а в следующем такте н младший разряд сумматора 5 подается единица, 5 1256010 - на первый вход сумматора 5множимое поступает в обратном кодесдвинутое на 1 разряд влево, а вследующем такте в младший разрядсумматора 5 подается .единица,511 - на первый вход сумматора 5множимое поступает в исходном коде.В два старших разряда сумматора5 в каждом следующем такте записываются единицы, если комбинации 10этих старших разрядов на выходесумматора 5 в предыдущем такте 01,10, 11, и записываются нули, есликомбинация 00.15Формула изобретения Устройство для умножения-разрядных чисел, содержащее (+2)-разрчдные регистры множимого, множите ля и .переносов, коммутатор, триггер запоминания, (и+4)-разрядный регистр частичных произведений, сумматор, содержащий ( 1+2) основных и два дополнительных разряда, причем 25 выходы сумматора соединены с входами регистра частичных произведений, выходы которого соединены с входами переносаосновных и двух дополнительных разрядов сумматора, выходы переносов (и+1) основных разрядов сумматора соединены с (+1) старшими разрядами регистра переносов, выход переноса первого дополнительного разряда сумматора соединен с Первым входом второго дополнительного разряда сумматора, выход переноса второго дополнительного разряда сумматора соединен с входом первого разряда регистра переносов, выход 40 которого соединен с первым входом первого дополнительного разряда сумматора, выходы ь старших разрядов регистра переносов соединены с входами первой группыосновных раз рядов сумматора, выходы суммы первого и второго дополнительных разрядов сумматора соединены со старшими разрядами регистра множителя, о т - л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения работы устройства с отрицательными числами, представляемыми в дополнительных кодах, с автоматическим представ.55 лением отрицательных результатов в дополнительном коде, в него введен преобразователь в дополнительный 18 Ькод, блок определения режима работы, содержащий элемент 2 ИИЛИ-НЕ, четыре элемента И, п ть элементов НЕ, блок анализа множителя, содержащий два сумматора, четыре элемента И, пять триггеров и один элемент ,2 ИИЛИ, блок управления передачей множимого, содержащий три элемента 2 ИИЛИ и один элемент 2 ИИЛИ, блок анализа знака произведения, восемь элементов И, второй коммутатор, содержащий два элемента И и один элемент ИЛИ, два элемента НЕ, причем прямой выход знакового разряда регистра множителя соединен с первым входом первой группы элемента 2 ИИЛИ блока определения режима работы, с первыми входами первого элемента И второго коммутатора, первыми входами четвертого и шестого элементов И устройства, инверсный выход знакового второго разряда регистра множителя соединен с первым входом второй группы элемента 2 ИИЛИ блока определения режима работы и первыми входами второго элемента И второго коммутатора и третьего элемента И устройства, прямой и инверсный выходы знакового разряда регистра множимого соединены с вторыми входами первой и второй групп входов элемента 2 ИИЛИ блока определения режима работы соответственно, информационные выходы регистра множимого соединены с входами первой группы первого коммутатора, выходы которого соединены с входами второй группы основных разрядов сумматора, выходы двух младших разрядов регистра множителя соединены с входами преобразователя в дополнительный код и вторым входом второго элемента И второго коммутатора, выход которого соединен с первым входом элемента ИЛИ второго коммутатора, выход преобразовате- ля в дополнительный код соединен с вторым входом первого элемента И второго коммутатора, выход которого соединен с вторым входом элемента ИЛИ второго коммутатора, группа выходов коорого соединена с группой входов блока анализа множителя, выход первого триггера которого соединен с первым входом первой группы первого элемента 2 ИИЛИ блока управления передачей множимого и первым входом пятого элемента И, вы 125601840 ход второго триггера блока анализамножителя соединен с первым входомпервой группы второго элемента2 ИИЛИ блоха управления передачеймножимого и вторым входом четвертого элемента И устройства, выходтретьего триггера блока анализа множителя соединен с первым входомтретьей группы перного элемента2 ИИЛИ блока управления передачеймножимого и вторым входом шестогоэлемента И, выход четвертого триггера блока анализа множителя соединен с первым входом первого элементаИ и с вторым входом третьей группывторого элемента 2 ИИЛИ блока управления передачей множимого, выход которого соединен с входамивторой. группы входов первого коммутатора, первый вход первого элемента и соединен с вторым входом третьего элемента И и входом первогоэлемента НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом седьмого элемента И,группа выходов первого, второго,третьего и четвертого элементов НЕблока определения режима работысоединена с группой входов блока30управления передачей множимого игруппой входов блока анализа знакапроизведения, выход первого элемента И-НЕ которого соединен с вторымвходом первого элемента И устройства 35выход которого соединен с входомтриггера запоминания, выход которого соединен с вторым входом седьмого элемента И, выход которогосоединен с вторым входом первого ипервым входом второго дополнительных старших разрядов сумматора, выход второго элемента И-НЕ блока анализа знака произведения соединен с вторыми входами второго и пятого элементов И, выходы третьего четвертогои пятого элементов И соединены соответственно с первым вторым и третьимвходами первого элемента ИЛИ, выходкоторого соединен с вторым входом 50второго младшего разряда сумматора,выход шестого элемента И соединенс первым входом второго элементаИЛИ и входом второго элемента НЕ,выход которого соединен с первым 55входом восьмого элемента ИЛИ, выходкоторого соединен с входом переноса первого младшего разряда сумматора, выход второго младшего разряда регистра переноса соединен с вторым входом восьмого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, причем вход первого разряда группы входов блока анализа множителя соединен с информационным входом первого сумматора и первыми входами первой и второй групп входов элемента 2 ИИЛИ блока анализа множителя, вход второго разряда группы входов блока анализа множителя соединен с информационным входом второго сумматора блока анализа множителя, выход суммы первого сумматора блока анализа множителя соединен с первыми входами второго и четвертого элементов И блока анализа множителя. инверсный выход суммы первого сумматора блока анализа множителя соединен с первыми входами первого и третьего элементов И и вторым входом второй группы входов элемента 2 ИИЛИ блока анализа множителя, выход переноса первого сумматора блока анализа множителя соединен с входом переноса второго сумматора блока анализа множителя, выход суммы которого соединен с вторыми входами третьего и четвертого элементов И и вторым входом первой группы входов элемента 2 ИИЛИ блока анализа множителя, инверсный выход суммы второго сумматора блока анализа множителя соединен с вторыми входами первого и второго элементов И блока анализа множителя, выходы первого второго, третьего и четвертого элементов И блока анализа множителя соединены соответственно с информационными входами первого, второго, третьего и четвер. ого триггеров блока анализамножителя, выходы которых являются соответственно первым, вторым, третьим и четвертым выходами блока анализа множителя, выход элемента 2 ИИЛИ блока анализа множителя с информационным входом пятого триггера блока анализа множителя, выход которого соединен с входом переноса первого сумматора блока анализа множителя, причем первый вход первой группы входов первого элемен"1 а 2 ИИЛИ, соединен с первым входом второй группы первого элемента 2 ИИЛИ, первый вход первой группы второго элемента 2 ИИЛИ соединен10 15 20 25 30 35 с первым входом второй группы второго элемента 2 ИИЛИ и первымивходами первой и второй групп третьего элемента 2 ИИЛИ, первый входтретьей группы первого элемента2 ИИЛИ соединен с первым входомчетвертой группы входов первого элемента 2 ИИЛИ, с первыми входамипервой и второй группы элемента2 ИИЛИ, блока управления передачеймножителя, первый вход третьейгруппы первого элемента 2 ИИЛИсоединен с первыми входами четвертой группы входов второго и третьего элементов 2 ИИЛИ, первый входгруппы входов блока управленияпередачей множимого соединен с вторыми входами первой группы входоввторого элемента 2 ИИЛИ, с вторыми входами четвертой группы входовпервого и третьего элементов2 ИИЛИ, второй вход группы входовблока управления передачей множимого соединен с вторыми входамитретьей группы входов первого итретьего элементов 2 ИИЛИ и вторыми входами второй группы входоввторого элемента 2 ИИЛИ, третийвход группы входов блока управленияпередачей множимого соединен с вторыми входами второй группы входовпервого и третьего элемента 2 ИИЛИ,вторыми входами третьей группывходов второго элемента 2 ИИЛИ ивторым входом первой группы входовэлемента 2 ИИЛИ, четвертый входгруппы входов блока управления перадачей множимого соединен свторыми входами йервой группы входов первого и третьего элементов2 ИИЛИ, с вторым входом четвертойгруппы входов второго элемента2 ИИЛИ и вторым входом второй группы входов элемента 2 ИИЛИ, выходывторого, третьего и первого элементов 2 ИИЛИ являются соответственно первым, вторым и третьим выходами блока управления передачеймножимого, выход элемента 2 ИИЛИявляется четвертым выходом блокауправления передачей множимого, причем первый вход блока определениярежима работы является первым входомпервой группы элемента 2 ИИЛИ-НЕ,второй вход блока определения режима работы является первым входомвторой группы элемента 2 ИИЛИ-НЕ,третий вход блока определения режима работы является вторым входомпервой группы входов элемента 2 ИИЛИ-НЕ, четвертый вход блокаопределения режима работы являетсявторым входом входов второй группыэлемента 2 ИИЛИ-НЕ, первый выходкоторого соединен с первыми входамипервого и второго элементов И ивходом первого элемента НЕ, выходкоторого соединен с первыми входамитретьего и четвертого элементов И,вторые входы первого и третьего элементов И соединены с первым входом второй группы элемента 2 ИИЛИ-НЕ,вторые входы второго и четвертогоэлементов И соединены с первым входом первой группы элемента 2 ИИЛИ-НЕ,выходы первого, третьего, четвертого и второго элементов И соединенысоответственно с входами второго,третьего, четвертого и пятого элементов НЕ, выходы которых являются первым, вторым, третьим и четвертым выходами соответственно группы выходов блока определения режима работы, блок анализа знака произведения содержит два элемента И-НЕ, приэтом группа входов блока анализазнака произведения является первымии вторыми входами первого и второгоэлементов И-НЕ, причем первый входгруппы входов блока анализа знака произведения является первым входом первого элемента И-НЕ, второй входгруппы входов блока анализа знакапроизведения является первым входом второго элемента И-НЕ, третий вход группы входов блока анализа знака произведения является вторым входом второго элемента И-НЕ, четвертый вход блока анализа знака произведения является вторым входом первого элементаИ-НЕ.1256018 Составитель Н.МаркеловаРедактор С.Патрушева Техред Л.Сердюкова орректор В.Снницк каз 4824/48 писное та С ытий 4/ 1 роиэводственно-полиграфическоепредприятие, г. Ужгород, у оектная, 4 Тираж НИИПИ Госуд по делам 113035, Мос

СмотретьЗаявка

3756125, 24.04.1984

ПРЕДПРИЯТИЕ ПЯ А-3759

ДИВИН ГЕННАДИЙ ВЛАДИМИРОВИЧ, РОМАНОВА ИННА ДМИТРИЕВНА, СОЛОДИЛОВ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

Опубликовано: 07.09.1986

Код ссылки

<a href="https://patents.su/8-1256018-ustrojjstvo-dlya-umnozheniya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения -разрядных чисел</a>

Предыдущий патент: Устройство для сложения в избыточной системе счисления

Следующий патент: Устройство для деления

Случайный патент: Радиальный химический реактор